# AceXtreme® C Software Development Kit

Model: BU-69092SX

# Software User's Manual

The AceXtreme<sup>®</sup> C Software Development Kit (SDK) provides the framework for efficient development of applications with DDC's series of MIL-STD-1553 components and cards.

For more information: www.ddc-web.com/BU-69092SX

# DDC's Data Networking Solutions

# MIL-STD-1553 | ARINC 429 | Fibre Channel

As the leading global supplier of data bus components, cards, and software solutions for the military, commercial, and aerospace markets, DDC's data bus networking solutions encompass the full range of data interface protocols from MIL-STD-1553 and ARINC 429 to USB, and Fibre Channel, for applications utilizing a spectrum of form-factors including PMC, PCI, Compact PCI, PC/104, ISA, and VME/VXI.

DDC has developed its line of high-speed Fibre Channel and Extended 1553 products to support the real-time processing of field-critical data networking netween sensors, compute notes, data storage displays, and weapons for air, sea, and ground military vehicles.

Whether employed in increased bandwidth, high-speed serial communications, or traditional avionics and ground support applications, DDC's data solutions fufill the expanse of military requirements including reliability, determinism, low CPU utilization, real-time performance, and ruggedness within harsh environments. Out use of in-house intellectual property ensures superior multi-generational support, independent of the life cycles of commercial devices. Moreover, we maintain software compatibility between product generations to protect our customers' investments in software development, system testing, and end-product qualification.

#### \_ MIL-STD-1553 \_

DDC provides an assortment of quality MIL-STD-1553 commercial, military, and COTS grade cards and components to meet your data conversion and data interface needs. DDC supplies MIL-STD-1553 board level products in a variety of form factors including AMC, USB, PCI, cPCI, PCI-104, PCMCIA, PMC, PC/104, PC/104-Plus, VME/VXI, and ISAbus cards. Our 1553 data bus board solutions are integral elements of military, aerospace, and industrial applications. Our extensive line of military and space grade components provide MIL-STD-1553 interface solutions for microprocessors, PCI buses, and simple systems. Our 1553 data bus solutions are designed into a global network of aircraft, helicopter, and missle programs.

#### \_ ARINC 429

DDC also has a wide assortment of quality ARINC-429 commercial, military, and COTS grade cards and components, which will meet your data conversion and data interface needs. DDC supplies ARINC-429 board level products in a variety of form factors including AMC, USB, PCI, PMC, PCI-104, PC/104 Plus, and PCMCIA boards. DDC's ARINC 429 components ensure the accurate and reliable transfer of flight-critical data. Our 429 interfaces support data bus development, validation, and the transfer of flight-critical data aboard commercial aerospace platforms.

#### \_ Fibre Channel \_

DDC has developed its line of high-speed Fibre Channel network access controllers and switches to support the real-time processing demands of field-critical data networking between sensors, computer nodes, data storage, displays, and weapons, for air, sea, and ground military vehicles. Fibre Channel's architecture is optimized to meet the performance, reliability, and demanding environmental requirements of embedded, real time, military applications, and designed to endure the multi-decade life cycle demands of military/aerospace programs.

# BU-69092SX ACEXTREME<sup>®</sup> C SDK SOFTWARE USER'S MANUAL

# MN-69092SX-002

The information provided in this Software User's Manual is believed to be accurate; however, no responsibility is assumed by Data Device Corporation for its use, and no license or rights are granted by implication or otherwise connection therewith.

Specifications are subject to change without notice. Please visit our Web site at <u>http://www.ddc-web.com/</u> for the latest information.

All rights reserved. No part of this Software User's Manual may be reproduced or transmitted in any form or by any mean, electronic, mechanical photocopying recording, or otherwise, without the prior written permission of Data Device Corporation.

105 Wilbur Place Bohemia, New York 11716-2426 Tel: (631) 567-5600, Fax: (631) 567-7358 World Wide Web - <u>http://www.ddc-web.com</u>

For Technical Support - 1-800-DDC-5757 ext. 7771 United Kingdom - Tel: +44-(0)1635-811140, Fax: +44-(0)1635-32264 France - Tel: +33-(0)1-41-16-3424, Fax: +33-(0)1-41-16-3425 Germany - Tel: +49-(0)89-15 00 12-11, Fax: +49-(0)89-15 00 12-22 Japan - Tel: +81-(0)3-3814-7688, Fax: +81-(0)3-3814-7689 Asia - Tel: +65- 6489-4801

© 2010 Data Device Corp.

Please note that this manual was developed from the EMACE PLUS SDK Manual (MN-69092SX-001). Please refer to the last page of this manual for record of change to the original manual.

| Revision | Date    | Pages                                                          | Description                                                                                                                                                                                                              |  |

|----------|---------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| А        | 2/2009  | All                                                            | Initial Release - Added the AceXtreme information throughout the manual. New section of functions added – Multi-RT                                                                                                       |  |

| В        | 5/2009  | 71-80, 123,<br>567, 604,<br>637, 639,<br>675, 694,<br>701, 707 | Minor updates on indicated pages                                                                                                                                                                                         |  |

| С        | 6/2009  | 161, 163,<br>165, 167,<br>231, 235                             | Function reference descriptions edited. Changed acexMRTDataBlkCreate to aceRTDataBlkCreate.                                                                                                                              |  |

| D        | 8/2009  | 519 - 954                                                      | Minor edits made to aceRTSetAddress, aceRTSetAddrSource, and<br>AceRTModeCodeWriteData. New Function subsections AvionicsI/O<br>and Discrete I/O added. New functions and structures added for<br>software version 3.1.2 |  |

| E        | 1/2010  | 449-461,<br>509-521                                            | Edited the following functions: aceBCOpCodeCreate,<br>acexBCMemObjCreate, acexBCMemObjDelete,<br>acexBCMemWrdCreate, acexBCMemWrdDelete,<br>acexBCMemWrdRead, acexBCMemWrdWrite                                          |  |

| F        | 7/2010  | All                                                            | New Format Applied. Function sections removed and created into new manual.                                                                                                                                               |  |

| G        | 10/2010 | 22                                                             | Removed section 1 that had the software licensing<br>Table 4 added dots for RTMTI in both SF and MF columns<br>Added a note for ACE _MODE_MT and ACE_MODE_RTMT as "Not<br>Recommended for new designs" for AceXtreme     |  |

| Н        | 12/2010 | 120                                                            | In table 45, in the ACE_RT_OPT_ALT_STS row,<br>"aceRTStatusBitsXlear()" was changed to "aceRTStatusBitsClear()"                                                                                                          |  |

| J        | 5/2011  | 17                                                             | Updated Table 3 to incorporate BU-67211U                                                                                                                                                                                 |  |

| K        | 12/2011 | 48                                                             | Updated Table 15                                                                                                                                                                                                         |  |

| L        | 4/2012  | 73, 128                                                        | Updated aceBCGetMsgFromIDRaw, Changed text from "cognizant"<br>to "contiguous"                                                                                                                                           |  |

| М        | 12/2015 | various                                                        | Updates to Windows, Linux, and VxWorks sections. New sections<br>added for DIOs and AIOs, updated description of the BSW for all<br>modes.                                                                               |  |

| 1 P | PREFA  | CE                                        | .12 |

|-----|--------|-------------------------------------------|-----|

| 1.1 | Text l | Jsage                                     | .12 |

| 1.2 | Speci  | al Handling and Cautions                  | .12 |

| 1.3 | Trade  | emarks                                    | .12 |

| 1.4 | Techr  | nical Support                             | .12 |

| 2 C |        | /IEW                                      | 13  |

| 2.1 |        | ription                                   |     |

| 2.2 |        | iption                                    |     |

| 2.2 |        | m Requirements                            |     |

| 2.4 | -      | MIL-STD-1553 Device Families              |     |

| 2.4 |        | treme SDK Directory Structure for Windows |     |

| -   | .5.1   | AceLibrarySupport                         |     |

|     | .5.2   | Documentation                             |     |

|     | .5.3   | Drivers                                   |     |

|     | 5.4    | Firmware                                  |     |

| _   | 5.4    | Include Directory                         |     |

|     | .5.6   | Lib Directory                             |     |

|     | 5.0    |                                           |     |

| _   | .5.7   | Samples                                   |     |

|     |        | TesterSimulatorLibrarySupport             |     |

|     | .5.9   | Utilities                                 |     |

|     |        | treme SDK Directory Structure for Linux   |     |

|     | .6.1   | ddccm                                     |     |

|     | .6.2   | docs                                      |     |

|     | .6.3   | drivers                                   |     |

|     | .6.1   | Firmware                                  |     |

|     | .6.2   | libraries                                 |     |

|     | .6.3   | samples                                   |     |

|     | .6.4   | tools                                     |     |

|     |        | treme SDK Directory Structure for VxWorks |     |

|     | .7.1   | bsp                                       |     |

|     | .7.2   | ddccm                                     |     |

|     | .7.3   | docs                                      |     |

|     | .7.4   | drivers                                   |     |

|     | .7.5   | Firmware                                  |     |

|     | .7.6   | libraries                                 |     |

|     | .7.7   | samples                                   |     |

| 2   | .7.8   | tools                                     | .27 |

| 3 U | JSING  | THE ACEXTREME C SDK                       | .29 |

| 3.1 |        | ization and Setup                         |     |

|     |        |                                           |     |

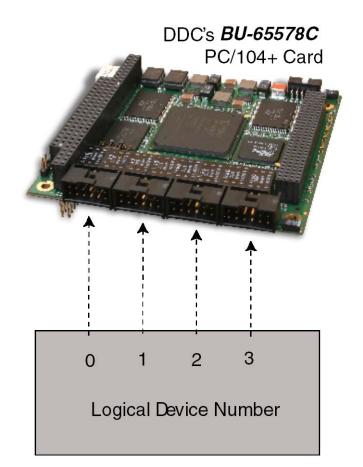

| 3.1.1                                                                                                                                                                                         | Logical Device Numbers                                                                                                                                                                                                                                   | 29                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.1.2                                                                                                                                                                                         | Assigning Logical Device Numbers                                                                                                                                                                                                                         | 30                                                                                                                                              |

| 3.1.3                                                                                                                                                                                         | Initializing a MIL-STD-1553 Channel                                                                                                                                                                                                                      | 32                                                                                                                                              |

| 3.2 Gene                                                                                                                                                                                      | eral Concepts                                                                                                                                                                                                                                            |                                                                                                                                                 |

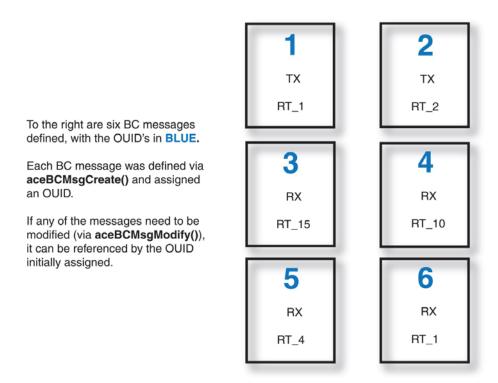

| 3.2.1                                                                                                                                                                                         | Object Unique Identifiers (OUID)                                                                                                                                                                                                                         | 33                                                                                                                                              |

| 3.2.2                                                                                                                                                                                         | Hardware Time Tags                                                                                                                                                                                                                                       | 34                                                                                                                                              |

| 3.2.3                                                                                                                                                                                         | Configuring Hardware Interrupts and Callback Routines                                                                                                                                                                                                    | 35                                                                                                                                              |

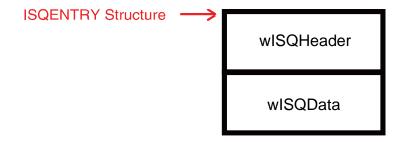

| 3.2.4                                                                                                                                                                                         | Interrupt Status Queues                                                                                                                                                                                                                                  | 37                                                                                                                                              |

| 3.2.5                                                                                                                                                                                         | Discrete Digital I/O                                                                                                                                                                                                                                     | 39                                                                                                                                              |

| 3.2.6                                                                                                                                                                                         | Avionics I/O                                                                                                                                                                                                                                             | 46                                                                                                                                              |

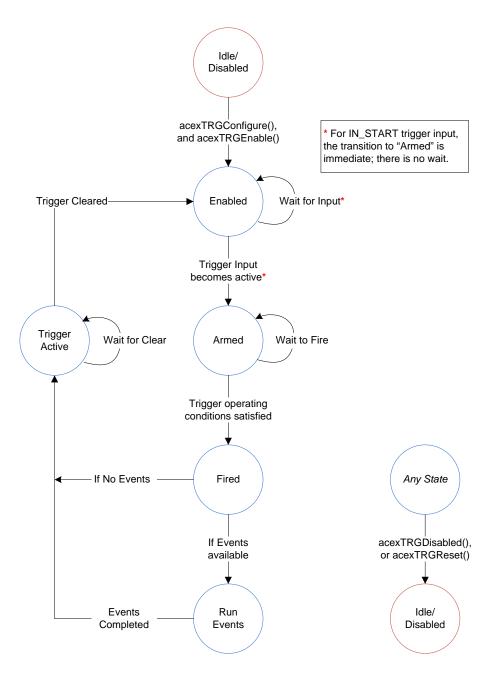

| 3.2.7                                                                                                                                                                                         | Triggers                                                                                                                                                                                                                                                 | 51                                                                                                                                              |

| 3.3 1553                                                                                                                                                                                      | Modes of Operation                                                                                                                                                                                                                                       | 62                                                                                                                                              |

| 3.3.1                                                                                                                                                                                         | Bus Controller (ACE_MODE_BC)                                                                                                                                                                                                                             |                                                                                                                                                 |

| 3.3.2                                                                                                                                                                                         | IRIG-106 Chapter 10 Monitor (ACE_MODE_MTI)                                                                                                                                                                                                               | 111                                                                                                                                             |

| 3.3.3                                                                                                                                                                                         | Classic Monitor (ACE_MODE_MT)                                                                                                                                                                                                                            | 132                                                                                                                                             |

| 3.3.4                                                                                                                                                                                         | Remote Terminal (ACE_MODE_RT)                                                                                                                                                                                                                            | 145                                                                                                                                             |

| 3.3.5                                                                                                                                                                                         | Multi-RT (ACE_MODE_MRT)                                                                                                                                                                                                                                  | 175                                                                                                                                             |

| 3.3.6                                                                                                                                                                                         | Combination Modes                                                                                                                                                                                                                                        | 193                                                                                                                                             |

| 3.3.7                                                                                                                                                                                         | Error Injection                                                                                                                                                                                                                                          | 203                                                                                                                                             |

| 3.3.8                                                                                                                                                                                         | Amplitude                                                                                                                                                                                                                                                | 209                                                                                                                                             |

| 3.3.9                                                                                                                                                                                         | Self-Test Capabilities (ACE_MODE_TEST)                                                                                                                                                                                                                   | 209                                                                                                                                             |

| 3.3.10                                                                                                                                                                                        | Testing Hardware Memory                                                                                                                                                                                                                                  | 211                                                                                                                                             |

|                                                                                                                                                                                               |                                                                                                                                                                                                                                                          |                                                                                                                                                 |

|                                                                                                                                                                                               |                                                                                                                                                                                                                                                          | 215                                                                                                                                             |

|                                                                                                                                                                                               | DED DEMOS                                                                                                                                                                                                                                                |                                                                                                                                                 |

| 4.1 Gene                                                                                                                                                                                      | eral Demo Programs                                                                                                                                                                                                                                       | 215                                                                                                                                             |

| 4.1 Gene<br>4.1.1                                                                                                                                                                             | eral Demo Programs<br>AIO.c                                                                                                                                                                                                                              | 215<br>215                                                                                                                                      |

| 4.1 Gene<br>4.1.1<br>4.1.2                                                                                                                                                                    | eral Demo Programs<br>AIO.c<br>BcAsync.c                                                                                                                                                                                                                 | 215<br>215<br>216                                                                                                                               |

| 4.1 Gene<br>4.1.1<br>4.1.2<br>4.1.3                                                                                                                                                           | eral Demo Programs<br>AIO.c<br>BcAsync.c<br>BCAsync2.c                                                                                                                                                                                                   | 215<br>215<br>216<br>216                                                                                                                        |

| 4.1 Gene<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4                                                                                                                                                  | eral Demo Programs<br>AIO.c<br>BcAsync.c<br>BCAsync2.c<br>BCDemo.c                                                                                                                                                                                       | 215<br>215<br>216<br>216<br>216                                                                                                                 |

| 4.1 Gene<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5                                                                                                                                         | eral Demo Programs<br>AIO.c<br>BcAsync.c<br>BCAsync2.c<br>BCDemo.c<br>BCDBuf.c                                                                                                                                                                           | 215<br>215<br>216<br>216<br>216<br>216                                                                                                          |

| 4.1 Gene<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>4.1.6                                                                                                                                | eral Demo Programs<br>AIO.c<br>BcAsync.c<br>BCAsync2.c<br>BCDemo.c<br>BCDBuf.c<br>RTDBuf.c                                                                                                                                                               | 215<br>215<br>216<br>216<br>216<br>216<br>217                                                                                                   |

| 4.1 Gene<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>4.1.6<br>4.1.7                                                                                                                       | AIO.c<br>BcAsync.c<br>BCAsync2.c<br>BCDemo.c<br>BCDBuf.c<br>RTDBuf.c<br>RTMode.c                                                                                                                                                                         | 215<br>215<br>216<br>216<br>216<br>216<br>217<br>217                                                                                            |

| 4.1 Gene<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>4.1.6<br>4.1.7<br>4.1.8                                                                                                              | eral Demo Programs<br>AIO.c<br>BcAsync.c<br>BCAsync2.c<br>BCDemo.c<br>BCDBuf.c<br>RTDBuf.c<br>RTMode.c<br>RTMTDemo.c                                                                                                                                     | 215<br>215<br>216<br>216<br>216<br>216<br>217<br>217<br>217                                                                                     |

| 4.1 Gene<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>4.1.6<br>4.1.7<br>4.1.8<br>4.1.9                                                                                                     | AIO.c<br>BcAsync.c<br>BCAsync2.c<br>BCDemo.c<br>BCDBuf.c<br>RTDBuf.c<br>RTMode.c<br>RTMTDemo.c<br>MTPoll.c                                                                                                                                               | 215<br>215<br>216<br>216<br>216<br>216<br>217<br>217<br>217<br>218                                                                              |

| 4.1 Gene<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>4.1.6<br>4.1.7<br>4.1.8<br>4.1.9<br>4.1.10                                                                                           | AIO.c<br>BcAsync.c<br>BCAsync2.c.<br>BCDemo.c<br>BCDBuf.c.<br>RTDBuf.c.<br>RTMode.c.<br>RTMTDemo.c.<br>MTPoll.c.<br>MTIrq.c.                                                                                                                             | 215<br>215<br>216<br>216<br>216<br>216<br>217<br>217<br>217<br>217<br>218<br>218                                                                |

| 4.1 Gene<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>4.1.6<br>4.1.7<br>4.1.8<br>4.1.9<br>4.1.10<br>4.1.11                                                                                 | AIO.c<br>BcAsync.c<br>BCAsync2.c<br>BCDemo.c<br>BCDBuf.c<br>RTDBuf.c<br>RTMode.c<br>RTMTDemo.c<br>MTPoll.c<br>MTIrq.c<br>DIO.c                                                                                                                           | 215<br>215<br>216<br>216<br>216<br>216<br>217<br>217<br>217<br>218<br>218<br>218                                                                |

| 4.1 Gene<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>4.1.6<br>4.1.7<br>4.1.8<br>4.1.9<br>4.1.10<br>4.1.11<br>4.1.12                                                                       | AIO.c<br>BcAsync.c<br>BCAsync2.c.<br>BCDemo.c<br>BCDBuf.c.<br>RTDBuf.c.<br>RTMode.c.<br>RTMTDemo.c<br>MTPoll.c.<br>MTIrq.c<br>DIO.c.                                                                                                                     | 215<br>215<br>216<br>216<br>216<br>216<br>217<br>217<br>217<br>217<br>218<br>218<br>218<br>219                                                  |

| 4.1 Gene<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>4.1.6<br>4.1.7<br>4.1.8<br>4.1.9<br>4.1.10<br>4.1.11<br>4.1.12<br>4.1.13                                                             | AIO.c.<br>BCAsync.c.<br>BCAsync2.c.<br>BCDemo.c.<br>BCDBuf.c.<br>RTDBuf.c.<br>RTMode.c.<br>RTMTDemo.c.<br>MTPoll.c.<br>MTIrq.c.<br>DIO.c.<br>DIOALL.c.<br>Irigdemo.c.                                                                                    | 215<br>215<br>216<br>216<br>216<br>216<br>217<br>217<br>217<br>217<br>218<br>218<br>218<br>218<br>219<br>219                                    |

| 4.1 Gene<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>4.1.6<br>4.1.7<br>4.1.8<br>4.1.9<br>4.1.10<br>4.1.11<br>4.1.12<br>4.1.13<br>4.1.14                                                   | AIO.c<br>BcAsync.c<br>BCAsync2.c<br>BCDemo.c<br>BCDBuf.c<br>RTDBuf.c<br>RTMode.c<br>RTMTDemo.c<br>MTPoll.c<br>MTIrq.c<br>DIO.c<br>DIOALL.c<br>Irigdemo.c<br>Looptest.c                                                                                   | 215<br>215<br>216<br>216<br>216<br>217<br>217<br>217<br>217<br>218<br>218<br>218<br>218<br>219<br>219<br>219                                    |

| 4.1 Gene<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>4.1.6<br>4.1.7<br>4.1.8<br>4.1.9<br>4.1.10<br>4.1.10<br>4.1.11<br>4.1.12<br>4.1.13<br>4.1.4<br>4.1.2                                 | AIO.c<br>BcAsync.c.<br>BCAsync2.c.<br>BCDemo.c.<br>BCDBuf.c.<br>RTDBuf.c.<br>RTMode.c.<br>RTMTDemo.c.<br>MTPoll.c.<br>MTIrq.c.<br>DIO.c.<br>DIO.c.<br>Looptest.c.<br>Mti2disk.c.                                                                         | 215<br>215<br>216<br>216<br>216<br>216<br>217<br>217<br>217<br>217<br>218<br>218<br>218<br>218<br>219<br>219<br>219<br>220                      |

| 4.1 Gene<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>4.1.6<br>4.1.7<br>4.1.8<br>4.1.9<br>4.1.10<br>4.1.11<br>4.1.12<br>4.1.13<br>4.1.14<br>4.1.15<br>4.1.16                               | AIO.c.<br>BcAsync.c.<br>BCAsync2.c.<br>BCDemo.c.<br>BCDBuf.c.<br>RTDBuf.c.<br>RTMode.c.<br>RTMTDemo.c.<br>MTPoll.c.<br>MTIrq.c.<br>DIO.c.<br>DIOALL.c.<br>Irigdemo.c.<br>Looptest.c.<br>Mti2disk.c.                                                      | 215<br>215<br>216<br>216<br>216<br>216<br>217<br>217<br>217<br>217<br>218<br>218<br>218<br>218<br>219<br>219<br>219<br>220                      |

| 4.1 Gene<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>4.1.6<br>4.1.7<br>4.1.8<br>4.1.9<br>4.1.10<br>4.1.11<br>4.1.12<br>4.1.13<br>4.1.14<br>4.1.15<br>4.1.16<br>4.1.15<br>4.1.16<br>4.1.17 | AIO.c.<br>BcAsync.c.<br>BCAsync2.c.<br>BCDemo.c.<br>BCDemo.c.<br>BCDBuf.c.<br>RTDBuf.c.<br>RTMode.c.<br>RTMTDemo.c.<br>MTPoll.c.<br>MTIrq.c.<br>DIO.c.<br>DIO.c.<br>DIOALL.c.<br>Irigdemo.c.<br>Looptest.c.<br>Mti2disk.c.<br>Mti2disk2.c.<br>Mtidemo.c. | 215<br>215<br>216<br>216<br>216<br>217<br>217<br>217<br>217<br>217<br>218<br>218<br>218<br>218<br>219<br>219<br>219<br>219<br>220<br>220        |

| 4.1 Gene<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>4.1.6<br>4.1.7<br>4.1.8<br>4.1.9<br>4.1.10<br>4.1.11<br>4.1.12<br>4.1.13<br>4.1.14<br>4.1.15<br>4.1.16                               | AIO.c.<br>BcAsync.c.<br>BCAsync2.c.<br>BCDemo.c.<br>BCDBuf.c.<br>RTDBuf.c.<br>RTMode.c.<br>RTMTDemo.c.<br>MTPoll.c.<br>MTIrq.c.<br>DIO.c.<br>DIOALL.c.<br>Irigdemo.c.<br>Looptest.c.<br>Mti2disk.c.                                                      | 215<br>215<br>216<br>216<br>216<br>216<br>217<br>217<br>217<br>217<br>218<br>218<br>218<br>218<br>219<br>219<br>219<br>219<br>220<br>220<br>220 |

| 4.1.20   | RTirq.c                          | 220 |

|----------|----------------------------------|-----|

| 4.1.21   | RTMTiDemo.c                      | 220 |

| 4.1.22   | RTPoll.c                         | 221 |

| 4.1.23   | Tester.c                         | 221 |

| 4.2 AceX | treme Demo Programs              | 221 |

| 4.2.1    | Aesdemo.c                        | 221 |

| 4.2.2    | Bcmti.c                          | 221 |

| 4.2.3    | MTIedemo.c                       | 221 |

| 4.2.4    | MRTMTi.c                         | 221 |

| 4.2.5    | RTDataArray.c                    | 222 |

| 4.2.6    | DataArray.c                      | 222 |

| 4.2.7    | DataStrm.c                       | 222 |

| 4.2.8    | Mrtdemo.c                        | 222 |

| 4.3 AceX | treme MF Samples                 | 222 |

| 4.3.1    | BCei .c (AceXtreme MF only)      | 222 |

| 4.3.2    | BCIMR.c (AceXtreme MF only)      | 223 |

| 4.3.3    | BCMemobj .c (AceXtreme MF only)  | 223 |

| 4.3.4    | BCMRT.c (AceXtreme MF only)      | 223 |

| 4.3.5    | BCMRTMTI.c (AceXtreme MF only)   | 224 |

| 4.3.6    | BCOpcode.c (AceXtreme MF only)   | 224 |

| 4.3.7    | BCTime.c (AceXtreme MF only)     | 224 |

| 4.3.8    | DBCDEMO.c (AceXtreme MF only)    |     |

| 4.3.9    | MRTEI.c (AceXtreme MF only)      | 225 |

| 4.3.10   | MTRDemo.c (AceXtreme MF only)    | 225 |

| 4.3.11   | ReplayDemo.c (AceXtreme MF only) | 225 |

| 4.3.12   | Resptime.c (AceXtreme MF only)   | 226 |

| 4.3.13   | Trigdio.c (AceXtreme MF only)    | 226 |

| 4.3.14   | Trigger.c (AceXtreme MF only)    | 226 |

| 4.3.15   | Voltage.c (AceXtreme MF only)    | 226 |

| Figure 1. AceXtreme SDK for Windows Directory Structure                    | 15  |

|----------------------------------------------------------------------------|-----|

| Figure 2. Ace Library Option Screen                                        |     |

| Figure 3. Tester Simulator Library Option Screen                           |     |

| Figure 4. AceXtreme SDK for Linux Directory Structure                      | 20  |

| Figure 5. AceXtreme SDK for VxWorks Directory Structure                    | 25  |

| Figure 6. Logical Device Number Assignments                                | 29  |

| Figure 7. DDC Card Manager for Windows                                     | 30  |

| Figure 8. DDC Card Manger for Linux                                        | 31  |

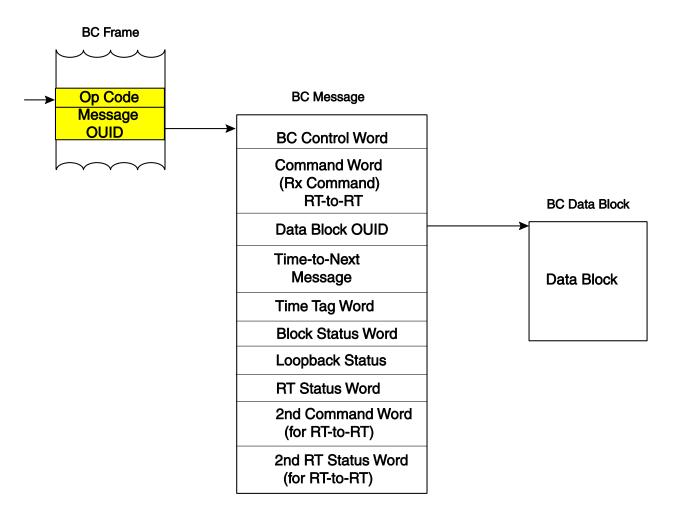

| Figure 9. Defined BC Messages Showing OUID and Message Configuration       | 34  |

| Figure 10. Trigger State Diagram                                           |     |

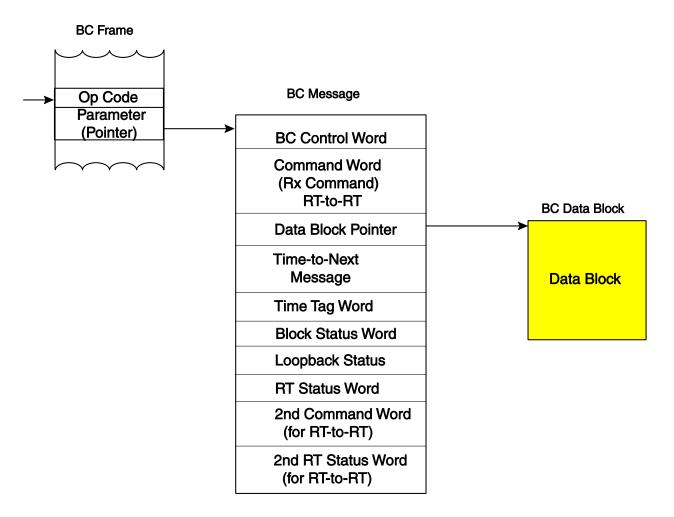

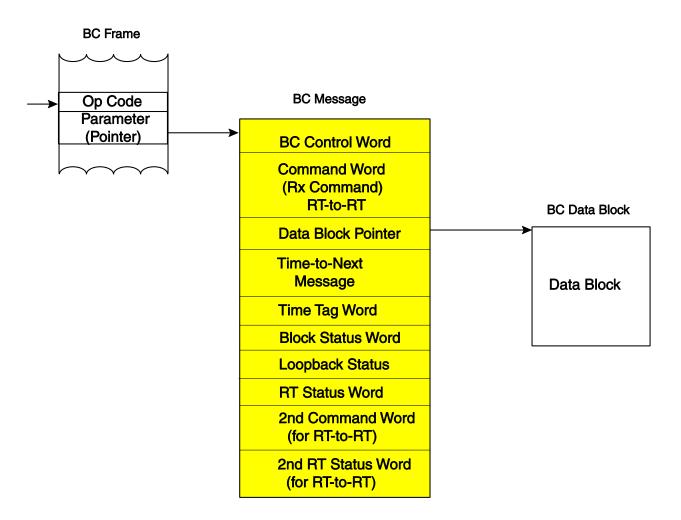

| Figure 11. Relationship of BC Data Blocks                                  | 65  |

| Figure 12. Relationship of BC Message Blocks                               | 67  |

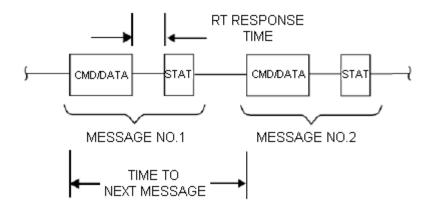

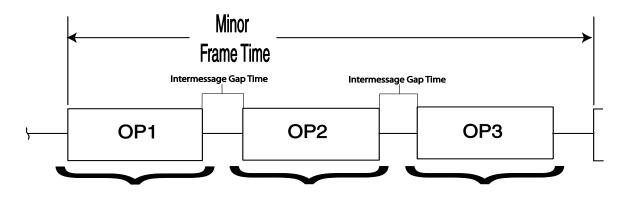

| Figure 13. Time To Next Message                                            | 68  |

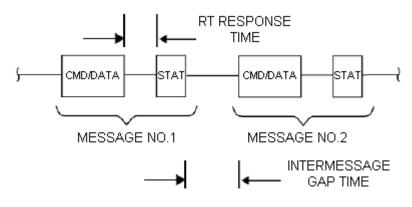

| Figure 14. Inter-message Gap Time                                          | 68  |

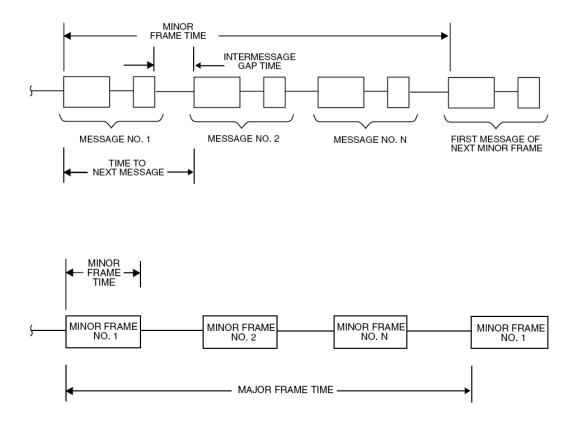

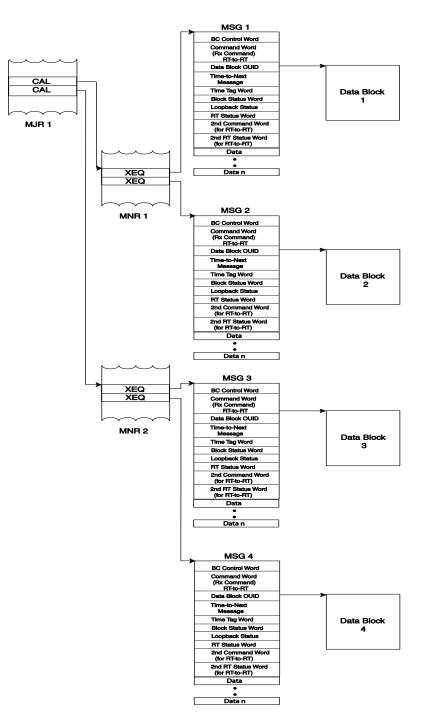

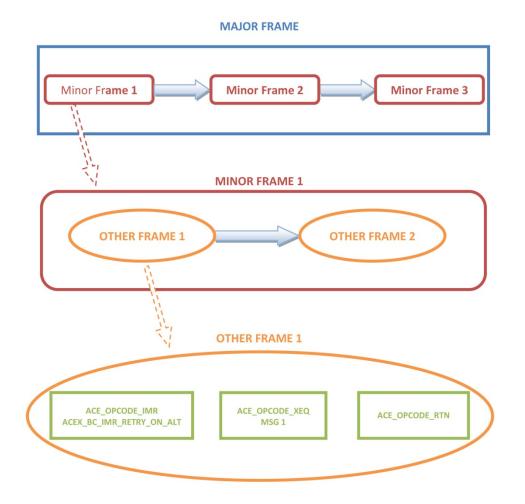

| Figure 15. BC Major and Minor Frames                                       | 74  |

| Figure 16. BC Opcode Relationships                                         |     |

| Figure 17. Minor Frame Defined as a Collection of BC Opcodes               | 80  |

| Figure 18. BC Framing/Sequencing Object Relation                           |     |

| Figure 19. BC Host Buffer MSGSTRUCT Object Definition                      | 93  |

| Figure 20. BC Message Block MSGSTRUCT Object Definition                    | 98  |

| Figure 21. IMR Frame Sequence                                              | 107 |

| Figure 22. MT-I 1553 Data Packet – Channel Specific Data                   | 116 |

| Figure 23. MT-I 1553 Data Packet – Block Status Word                       | 117 |

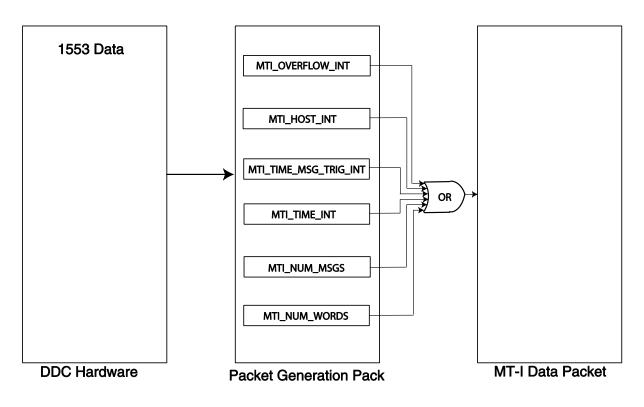

| Figure 24. MT-I Data Packet Generation – Interrupt Events                  |     |

| Figure 25. MT-I Time Data Packet – Channel Specific Data                   | 125 |

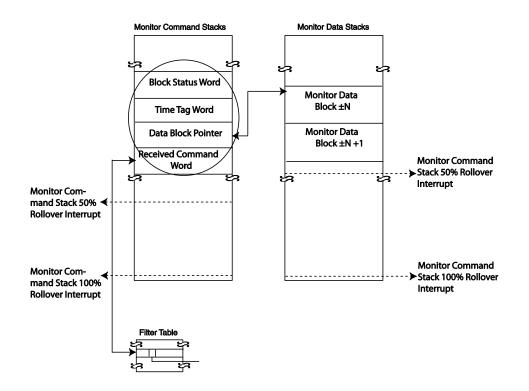

| Figure 26. Monitor Command and Data Stacks Relationship                    |     |

| Figure 27. MT Host Buffer MSGSTRUCT Object Definition                      | 140 |

| Figure 28. MT Stack MSGSTRUCT Object Definition                            | 143 |

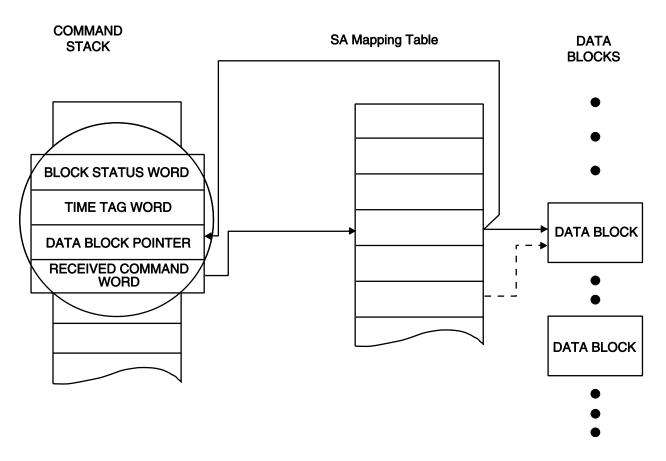

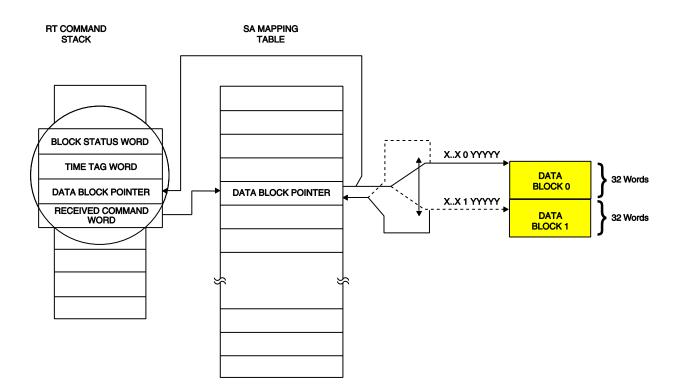

| Figure 29. RT Command Stack, SA Mapping Table and Data Blocks Relationship | 146 |

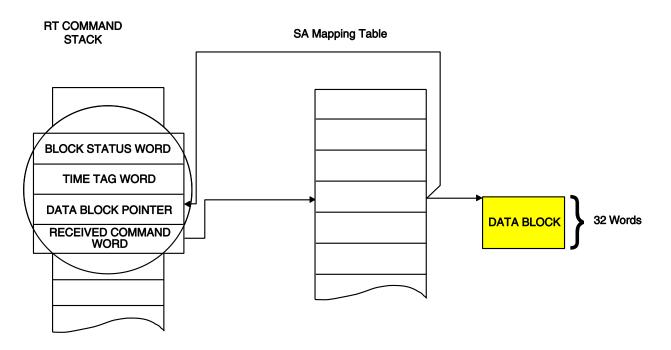

| Figure 30. Single-Buffer RT Data Block Storage                             | 155 |

| Figure 31. Double-Buffered RT Data Block Storage                           | 156 |

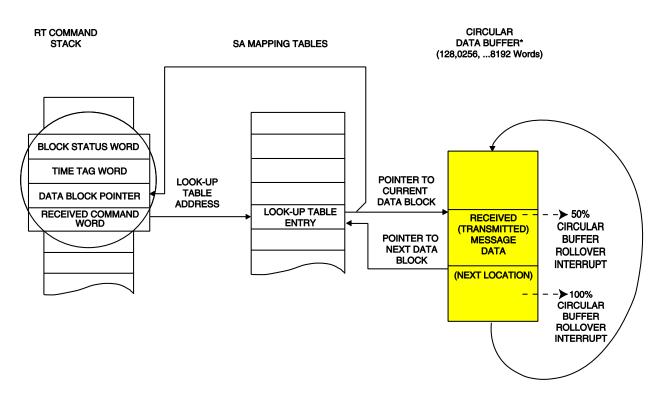

| Figure 32. Circular-Buffered RT Data Block Storage                         | 157 |

| Figure 33. RT Command Stack MSGSTRUCT Object Definition                    |     |

| Figure 34. RT Data Block MSGSTRUCT Object Definition                       | 170 |

| Figure 35. AceXtreme BC Error Injection                                    | 206 |

| Figure 36. AceXtreme RT Error Injection                                    | 209 |

|                                                                            |     |

| Table 1. DDC MIL-STD-1553 Family Features                                           |     |

|-------------------------------------------------------------------------------------|-----|

| Table 2. AceXtreme SDK Directory Structure for Windows                              |     |

| Table 3. Drivers of DDC Hardware                                                    |     |

| Table 4. Discontinued Drivers of DDC Hardware for Windows                           | 17  |

| Table 5. AceXtreme SDK Directory Structure for Linux                                | 21  |

| Table 6. Drivers of DDC Hardware for Linux                                          |     |

| Table 7. Discontinued Drivers of DDC Hardware for Linux                             |     |

| Table 8. AceXtreme SDK Directory Structure for VxWorks                              | 25  |

| Table 9. Drivers of DDC Hardware for VxWorks                                        |     |

| Table 10. Discontinued Drivers of DDC Hardware for VxWorks                          | 27  |

| Table 11. MIL-STD-1553 Channel Modes                                                |     |

| Table 12. Initialization Minimal Input Requirements                                 | 33  |

| Table 13. Data Object Types                                                         |     |

| Table 14. Interrupt Events                                                          |     |

| Table 15. Interrupt Status Queue Header Values                                      | 38  |

| Table 16. Trigger IDs                                                               |     |

| Table 17. Trigger Inputs (u8InTmtTrg or u8InGptTrg)                                 | 55  |

| Table 18. Trigger Events                                                            | 57  |

| Table 19. Trigger Status Block                                                      | 60  |

| Table 20. Trigger Interrupt Status Block                                            | 61  |

| Table 21. BC Configuration Options                                                  | 63  |

| Table 22. BC Configuration Options for AceXtreme Hardware                           | 63  |

| Table 23. Synchronous Message Block Type Create Functions                           | 69  |

| Table 24. Synchronous Message Options                                               |     |

| Table 25. Asynchronous Message Block Type Create Functions                          | 71  |

| Table 26. Asynchronous Message Options                                              |     |

| Table 27. BC Opcode Definitions and Parameter Meanings                              | 75  |

| Table 28. Intermessage Routines                                                     | 76  |

| Table 29. Block Data Size                                                           | 77  |

| Table 30. BC Host Buffer Raw Format for One Message                                 | 91  |

| Table 31. BC Host Buffer Message Location and Purge Options (wMsgLoc)               | 92  |

| Table 32. BC Block Status Word                                                      |     |

| Table 33. BC Block Status Word Retry Count                                          | 95  |

| Table 34. BC Raw Format for One Message                                             | 96  |

| Table 35. BC Interrupt Event Options                                                | 100 |

| Table 36. Intermessage Routines                                                     |     |

| Table 37. MT-I General Data Packet Format                                           | 112 |

| Table 38. MT-I 1553 Complete Data Packet                                            |     |

| Table 39. MT-I 1553 Data Packet - Intra-Packet Data Header                          |     |

| Table 40. MT-I 1553 Data Packet – Data Portion (1553 Command / Data / Status Words) | 118 |

| Table 41. MT-I Configuration Parameters                                             |     |

| Table 42. MT-I Configuration Options                                                |     |

| Table 43. Getting 1553 Data Packets: Blocking Options                               | 124 |

|                                                                                     |     |

| Table 44. | MT-I Time Data Packet Format                             | 124 |  |

|-----------|----------------------------------------------------------|-----|--|

|           | 3CD Day Format                                           |     |  |

| Table 46. | MT-I Time Data Packet - Time Data                        | 126 |  |

| Table 47. | Getting Time Data Packets - Blocking Options             | 128 |  |

|           | MT Host Buffer Raw Format for One Message                |     |  |

| Table 49. | Host Buffer Message Location and Purge Options (wMsgLoc) | 139 |  |

| Table 50. | MT Raw Format for Message One                            | 141 |  |

| Table 51. | Stacks Message Location and Purge Options (wMsgLoc)      | 142 |  |

| Table 52. | MT Block Status Word                                     | 144 |  |

| Table 53. | MT Interrupt Events                                      | 145 |  |

| Table 54. | RT Configuration Parameters                              | 147 |  |

|           | RT Configuration Options                                 |     |  |

| Table 56. | Busy Bit Lookup Table                                    | 150 |  |

| Table 57. | Standard RT Status Word                                  | 151 |  |

| Table 58. | Internal Built-in-Test (BIT) Data Word                   | 152 |  |

|           | RT Data Block Types                                      |     |  |

| Table 60. | RT Command Stack Raw Format for One Message              | 161 |  |

|           | RT Block Status Word                                     |     |  |

| Table 62. | RT Host Buffer Raw Format for One RT Message             | 169 |  |

| Table 63. | Mode Code Family Types                                   |     |  |

| Table 64. | Mode Code Interrupt Event Options                        | 172 |  |

| Table 65. | Command Legalization Lookup Table                        | 174 |  |

| Table 66. | RT Interrupt Event Options                               | 175 |  |

| Table 67. | MRT Configuration Parameters                             | 176 |  |

| Table 68. | Multi-RT Configuration Options                           | 177 |  |

| Table 69. | Busy Bit Lookup Table                                    | 179 |  |

|           | Standard RT Status Word                                  |     |  |

| Table 71. | Internal Built-In-Test (BIT) Data Word                   | 181 |  |

|           | Mode Code Family Types                                   |     |  |

| Table 73. | Mode Code Interrupt Event Options                        | 186 |  |

| Table 74. | Command Legalization Lookup Table                        | 188 |  |

| Table 75. | RT Interrupt Event Options                               | 189 |  |

| Table 76. | MRT Intermessage Routines                                | 192 |  |

| Table 77. | RTMT-I Configuration Parameters                          | 194 |  |

| Table 78. | RTMT-I Configuration Options                             | 195 |  |

| Table 79. | RTMT Configuration Parameters                            | 198 |  |

|           | RTMT Configuration Options                               |     |  |

|           | ACEX_ERR_INJ Structure – BC Error Injection              |     |  |

| Table 82. | ACEX_ERR_INJ Structure – RT Error Injection              | 207 |  |

|           |                                                          |     |  |

| Code Example 1. Initializing LDN #0 to Act as a Bus Controller (BC)                   |      |

|---------------------------------------------------------------------------------------|------|

| Code Example 2. Setting Resolution (2µs/LSB) & Value of the Hardware 48-bit Time Tag  |      |

| Code Example 3. Setting the Interrupt Callback Routine for Hardware Time Tag Rollover | . 37 |

| Code Example 4. Reading an Entry from the Interrupt Status Queue (ISQ)                |      |

| Code Example 5. Configuring Discrete lines.                                           | . 40 |

| Code Example 6. Reading DIO Channel direction                                         | . 41 |

| Code Example 7. Setting DIO Line Output Value                                         |      |

| Code Example 8. Setting DIO Line Output Value                                         | . 43 |

| Code Example 9. Using aceSetDiscAll() and aceGetDiscAll()                             | .44  |

| Code Example 10. Configuring DIO time stamp and ISR.                                  |      |

| Code Example 11. Starting Time Tag recording and reading Time tags.                   | . 46 |

| Code Example 12. Configuring Avionic Discrete lines                                   |      |

| Code Example 13. Reading AIO Channel direction                                        | . 48 |

| Code Example 14. Setting AIO Line Output Value.                                       |      |

| Code Example 15. Setting AIO Line Output Value.                                       |      |

| Code Example 16. Using aceSetAioAll() and aceGetAioAll().                             |      |

| Code Example 17. ACEX_TRG_CONFIG_TMT Structure                                        |      |

| Code Example 18. ACEX_TRG_CONFIG_GPT Structure                                        | . 54 |

| Code Example 19. Selecting an Event                                                   |      |

| Code Example 20. Event Enable and Select                                              | . 58 |

| Code Example 21. ACEX_DISC_CONFIG Structure                                           |      |

| Code Example 22. Configure a Discrete I/O                                             | . 59 |

| Code Example 23. Get Trigger and Interrupt Status                                     | . 61 |

| Code Example 24. Get Latched Time Tag                                                 |      |

| Code Example 25. Configuring the BC to Support "High-Priority" Asynchronous Messaging | . 64 |

| Code Example 26. Creating and Initializing a BC Data Block                            | . 66 |

| Code Example 27. Creating a BC to RT Synchronous Message Block                        | . 69 |

| Code Example 28. Creating a BC to RT Asynchronous Message Block                       | .72  |

| Code Example 29. Creating Two XEQ (Execute Message) Opcodes                           |      |

| Code Example 30. Creating a Minor Frame with Two Opcodes                              |      |

| Code Example 31. Creating a Push Timetag to GPQ Opcode                                | . 82 |

| Code Example 32. Reading an Entry from the GPQ                                        | . 82 |

| Code Example 33. Creating a GPF Opcode (Clearing GPF 1)                               | . 83 |

| Code Example 34. Setting GPF State via Host (Setting GPF 1)                           | . 83 |

| Code Example 35. Creating an XEQ (Execute Message) Dependant on GPF5                  | . 84 |

| Code Example 36. Creating a Subroutine Call Opcode to call Minor Frame "MNR1"         |      |

| Code Example 37. Creating a Major Frame (Calling 2 Minor Frames)                      | . 85 |

| Code Example 38. Starting the Bus Controller (BC)                                     | . 87 |

| Code Example 39. Stopping the Bus Controller (BC)                                     | . 88 |

| Code Example 40. Sending a High-Priority Asynchronous Message                         |      |

| Code Example 41. Sending a Low-Priority Asynchronous Message                          |      |

| Code Example 42. Installing the BC Host Buffer                                        |      |

| Code Example 43. Reading Raw Data From the Host Buffer                                |      |

| Code Example 44. Reading a Decoded Message from the Host Buffer                       | . 93 |

|                                                                                       |      |

| Cada Evennala 15. Daading Davy Data From a DC Maaaaga Dlaak                      | 07  |

|----------------------------------------------------------------------------------|-----|

| Code Example 45. Reading Raw Data From a BC Message Block                        |     |

| Code Example 46. Reading a Decoded Message from the BC Message Block             |     |

| Code Example 47. Reading a BC Data Block                                         |     |

| Code Example 48. Enable/Disbale DBC Support                                      |     |

| Code Example 49. Configuring Replay                                              |     |

| Code Example 50. Starting Replay                                                 |     |

| Code Example 51. Pausing / Continue Replay                                       |     |

| Code Example 52. Retrieve Replay Status                                          |     |

| Code Example 53. Configure BC IMRs                                               | 110 |

| Code Example 54. Configure Discrete to IMR                                       | 111 |

| Code Example 55. Filtering Out (Disabling) RT5 Transmit SubAddress 19            | 121 |

| Code Example 56. Starting the MT-I Monitor                                       |     |

| Code Example 57. Stopping the MT-I Monitor                                       |     |

| Code Example 58. Getting a MT-I 1553 Data Packet                                 |     |

| Code Example 59. Enabling Time Data Packets                                      |     |

| Code Example 60. Getting a MT-I 1553 Time Data Packet (TDP)                      | 127 |

| Code Example 61. Open MT-I File with Write Access                                | 129 |

| Code Example 62. Open MT-I File                                                  |     |

| Code Example 63. Read Packet from File                                           |     |

| Code Example 64. Write Packet to File                                            |     |

| Code Example 65. Get File Offset                                                 |     |

| Code Example 66. Set File Offset                                                 |     |

| Code Example 67. Filtering Out (Disabling) RT5 Transmit SubAddress 19            |     |

| Code Example 68. Starting the MT Monitor                                         |     |

| Code Example 69. Stopping the MT Monitor                                         |     |

| Code Example 70. Installing the MT Host Buffer                                   |     |

| Code Example 70. Installing the MT Host Bullet                                   | 101 |

|                                                                                  |     |

| Code Example 72. Reading a Decoded Message from the Host Buffer                  |     |

| Code Example 73. Reading Raw Data From the Stacks                                |     |

| Code Example 74. Reading a Decoded Message from the Stacks                       |     |

| Code Example 75. Setting the RT Address Source and Value                         |     |

| Code Example 76. Setting the Busy Bit for all TRANSMIT Commands to SA19 ("Own Ad |     |

|                                                                                  |     |

| Code Example 77. Setting the "Service Request" Bit in the RT Status Word         |     |

| Code Example 78. Configure and Read the Internal BIT Word                        | 153 |

| Code Example 79. Creating a Single-Buffered RT Data Block                        | 158 |

| Code Example 80. Mapping RTDBLK1 to TX ad RX messages for Subaddress 19          |     |

| Code Example 81. Starting the Remote Terminal (RT)                               |     |

| Code Example 82. Stopping the Remote Terminal (RT)                               | 160 |

| Code Example 83. Reading Raw Data from the RT Command Stack                      |     |

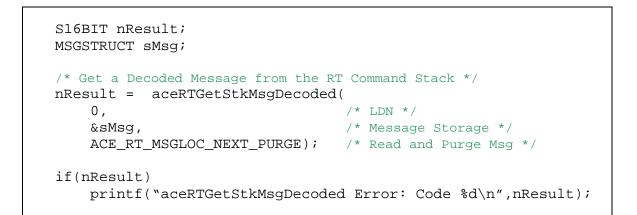

| Code Example 84. Reading a Decoded Message from the RT Command Stack             |     |

| Code Example 85. Reading a "Single-Buffered" Data Block                          |     |

| Code Example 86. Reading a "Circular-Buffered" Data Block                        |     |

| Code Example 87. Installing the RT Host Buffer                                   |     |

| Code Example 88. Reading Raw Data From the Host Buffer                           |     |

| Code Example 89. Reading a Decoded Message from the Host Buffer                  |     |

| ·                                                                                |     |

| Code Example 90. Reading Mode Code Data for "Synchronize"(10001)                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Code Example 93. Setting the Busy Bit for all TRANSMIT Commands to SA19 ("Own Addr", TX, SA 19)                                                                          |

| Code Example 94. Setting the "Service Request" Bit in the RT Status Word                                                                                                 |

| Code Example 96. Mapping RTDBLK1 to TX ad RX messages for RTADDRESS_1,                                                                                                   |

| Subaddress 19                                                                                                                                                            |

| Code Example 98. Stopping the Remote Terminal (RT)                                                                                                                       |

| Code Example 99. Reading Mode Code Data for "Synchronize" (10001) for RT Address 1 185<br>Code Example 100. Enabling an "Transmit Vector Word" Mode Code Interrupt Event |

| Code Example 101. Legalizing a Specific 1553 Command Word ("Own Addr", TX, SA19, All Word Counts)                                                                        |

| Code Example 102. Configuring RT 1's Response Time Value                                                                                                                 |

| Code Example 103. Configuring RT 1's Response Timeout Value                                                                                                              |

| Code Example 104. Clearing Discrete Configuration191                                                                                                                     |

| Code Example 105. Configure Discrete to BC IMR193                                                                                                                        |

| Code Example 106. Configure Discrete to MRT IMR193                                                                                                                       |

| Code Example 107. Starting the MT-I Monitor and Remote Terminal                                                                                                          |

| Code Example 108. Stopping the MT-I Monitor and Remote Terminal                                                                                                          |

| Code Example 109. Starting the MT Monitor and Remote Terminal                                                                                                            |

| Code Example 110. Stopping the MT Monitor and Remote Terminal                                                                                                            |

| Code Example 111. Configuring the BC's Response timeout value                                                                                                            |

| Code Example 112. Configuring the BC's Error Injection                                                                                                                   |

| Code Example 113. Configuring the RT's Error Injection                                                                                                                   |

| Code Example 114. TESTRESULT Structure                                                                                                                                   |

| Code Example 115. Running a Hardware Register Test                                                                                                                       |

| Code Example 116. Running a Hardware Memory Test                                                                                                                         |

| Code Example 117. Running a 1553 Protocol Test                                                                                                                           |

| Code Example 118. Running a Hardware Interrupt Test                                                                                                                      |

| Code Example 119. Running Hardware Vectors                                                                                                                               |

# 1 PREFACE

This manual uses typographical conventions to assist the reader in understanding the content. This section will define the text formatting used in the rest of the manual.

#### 1.1 Text Usage

- **BOLD** text that is written in bold letters indicates important information and table, figure, and chapter references.

- Courier New is used to indicate code examples.

- <...> Indicates user entered text or commands.

#### **1.2 Special Handling and Cautions**

The BU-69092 is delivered on a Compact Disc. Proper care should be used to ensure that the discs are not damaged by heat.

#### 1.3 Trademarks

All trademarks are the property of their respective owners.

#### **1.4 Technical Support**

In the event that problems arise beyond the scope of this manual, you can contact In the event that problems arise beyond the scope of this manual, you can contact DDC by the following:

US Toll Free Technical Support: 1-800-DDC-5757, ext. 7771

Outside of the US Technical Support: 1-631-567-5600, ext. 7771

Fax: 1-631-567-5758 to the attention of DATA BUS Applications

DDC Website: <a href="http://www.ddc-web.com/ContactUs/TechSupport.aspx">www.ddc-web.com/ContactUs/TechSupport.aspx</a>

Please note that the latest revisions of Software and Documentation are available for download at DDC's Web Site, <u>www.ddc-web.com</u>.

# 2 OVERVIEW

# 2.1 Description

The AceXtreme<sup>®</sup> C Software Development Kit (SDK) provides the framework for developing applications for DDC's series of MIL-STD-1553 components and cards, while using minimal development time.

This SDK is written such that all low level access to the DDC MIL-STD-1553 communication processor is simplified through a set of API functions in the interface and interrupt control modules. This abstraction allows one common software interface to any DDC MIL-STD-1553 cards or components.

Note: Version 3.0.1 of the BU-69092S0 only supports the AceXtreme boards.

#### 2.2 Features

- Library of "C" Routines Available for: Windows<sup>®</sup> XP (32 Bit) and Vista/7/8 (32/64 Bit), Linux<sup>®</sup>(32/64 Bit), and VxWorks<sup>®</sup> (32-Bit) Operating Systems

- Documentation Provided

- Provides Modular, Portable, & Readable Code to Reduce Software Development Time

- "C" Structures Eliminate Need to Learn Detailed Address/Bit Maps and Data Formats

- Includes Sample Programs and Compiled Libraries for Quick Startup

- Includes Multiple Environment/Compiler Support

# 2.3 System Requirements

One or more of the following:

- Windows XP, Windows Vista 32/64-bit, Windows 7 32/64-bit, Windows 7 32/64-bit, Linux, or VxWorks (32-Bit) Operating System.

- Workbench software development environment for VxWorks platforms.

- An appropriate compiler or development environment.

- Contact Factory for additional Operating Systems.

#### 2.4 DDC MIL-STD-1553 Device Families

DDC has been developing MIL-STD-1553 interface cards and components for 30 years. There have been numerous generations of devices to add new functionality and improved performance. The BU-69092Sx Software Development Kit supports the 3 latest generations of MIL-STD-1553 hardware families (AceXtreme, E<sup>2</sup>MA, and EMA).

- 1. AceXtreme :

- 2. E<sup>2</sup>MA (Extended Enhanced Mini-ACE):

- 3. EMA (Enhanced Mini-ACE):

| Table 1. DDC MIL-STD-1553 Family Features |                                          |                                     |                                               |                                              |

|-------------------------------------------|------------------------------------------|-------------------------------------|-----------------------------------------------|----------------------------------------------|

| Family                                    | <i>EMA</i><br>Released 1999              | E <sup>2</sup> MA<br>Released 2006  | AceXtreme<br>Single-Function<br>Released 2009 | AceXtreme<br>Multi-Function<br>Released 2010 |

| Part Number                               | BU-6555X<br>BU-6556X                     | BU-65577X<br>BU-65578X<br>BU-6559XX | BU-671XX                                      | BU-672XX                                     |

| Time-Tag support                          | 16-bit<br>Internal 2µs                   | 48-Bit<br>Internal 1µs              | 48-Bit<br>Internal 100ns                      | 48-Bit<br>Internal 100ns                     |

| Hardware Triggers                         | Not-Supported                            | Not-Supported                       | Not-Supported                                 | Supported                                    |

| Inter-Message<br>Routines                 | Not-Supported                            | Not-Supported                       | Not-Supported                                 | Supported                                    |

| Replay                                    | Not-Supported                            | Not-Supported                       | Not-Supported                                 | Supported                                    |

| BC Message Gap                            | >= 6µs                                   | >= 6µs                              | >= 6µs                                        | >= 3.5µs                                     |

| RT Response Time                          | 7µs                                      | 7µs                                 | 7µs                                           | >= 3.5µs                                     |

| BC Frame Time                             | 16-bit                                   | 16-bit                              | 16-bit                                        | 24-bit                                       |

| BC Streaming/Data<br>Arrays               | Not-Supported                            | Not-Supported                       | Supported                                     | Supported                                    |

| RT Streaming/Data<br>Arrays               | Not-Supported                            | Not-Supported                       | Supported                                     | Supported                                    |

| Multiple RT Addresses                     | Not-Supported                            | Not-Supported                       | Supported                                     | Supported                                    |

| MT IRIG106 Chapter 10                     | Not-Supported                            | Supported                           | Supported                                     | Supported                                    |

| MT Advanced Error<br>Sampling (AES)       | Not-Supported                            | Not-Supported                       | Not-Supported                                 | Supported                                    |

| BC Memory OpCodes                         | Not-Supported                            | Not-Supported                       | Supported                                     | Supported                                    |

| Error Injection                           | Not-Supported                            | Not-Supported                       | Not- Supported                                | Supported                                    |

| MIL-STD-1553<br>Operating Modes           | See Table 11. MIL-STD-1553 Channel Modes |                                     |                                               |                                              |

**Note:** Support for most EMACE and E<sup>2</sup>MA Devices with the AceXtreme SDK ended with version 3.5.3. Check the SDK's release notes for which boards of the EMACE and E<sup>2</sup>MA families are still supported with the most current version of the SDK.

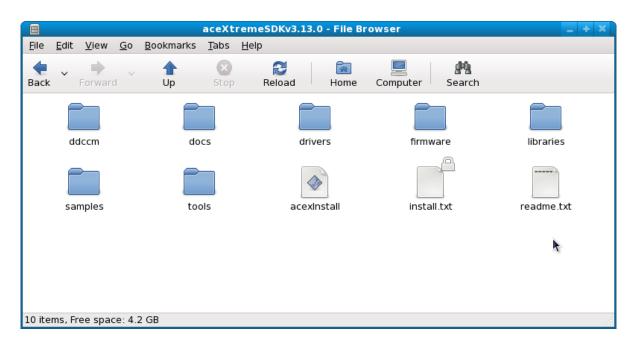

#### 2.5 AceXtreme SDK Directory Structure for Windows

The installation of the AceXtreme SDK for Windows will result in the creation of the folder C:\DDC\aceXtremeSDKvX.Y.Z (where XYZ represents the version of the SDK). The "AceXtremeSDKvX.Z.Y" folder contains the drivers, library, header and samples. Also included are the binary firmware files for applicable DDC hardware. The directory also includes the ACE Library Support Package and Tester Simulator Library Support Package. The Ace Library Support Package allows applications written for the ACE Library (BU-6908x) to run on any DDC MIL-STD-1553 device without the need to recompile source code. While the Tester Simulator Library (BU-69068x), allowing the applications to run on any Multi-Function AceXtreme Based card without the need to recompile source code.

#### Figure 1. AceXtreme SDK for Windows Directory Structure

| Table 2. AceXtreme SDK Directory Structure for Windows |                                                                                    |  |

|--------------------------------------------------------|------------------------------------------------------------------------------------|--|

| Folder Name                                            | Description of Contents                                                            |  |

| AceLibrarySupport                                      | Ace4.lib, Ace4.dll, include files and Ace Library samples.                         |  |

| Documentation                                          | ReleaseNotes.txt, and ReadMe.txt. Contains version information on SDK.             |  |

| Drivers                                                | Driver (.sys) and information files (inf) for driver installation.                 |  |

| Firmware                                               | Firmware for applicable DDC hardware and manual for updating flash                 |  |

| Include                                                | Header files for the AceXtreme SDK.                                                |  |

| Lib                                                    | Library files required for linking to AceXtreme dll (emacepl.dll and emacepl.lib). |  |

| Samples                                                | Samples for AceXtreme SDK (See Section 2.5.7).                                     |  |

| TesterSimulatorLibSupport                              | TestSim32.lib, TestSim.lib, include files and Tester Simulator library samples     |  |

| Utilities                                              | Application used to enable Tx inhibit and BC Disable on an AceXtreme Device.       |  |

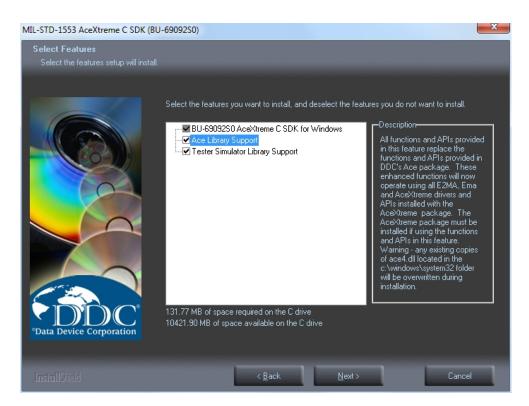

# 2.5.1 AceLibrarySupport

The "AceLibrarySupport" Directory contains the files needed to support current 1553 devices using applications originally written for the ACE Library (BU-6908X). This directory is an optional directory and is only installed when the ACE Library Support option is selected during the AceXtreme SDK installation.

Figure 2. Ace Library Option Screen

The ACE Library Support option is designed to run applications originally developed using the ACE library on current 1553 devices without requiring a recompile of the source code. The AceLibrarySupport Directory contains a new Ace4.lib and Ace4.dll, (the new ace4.dll is copied to C:\Windows\System32 and C:\windows\sysWoW64 upon installation of the ACE Library support option), the header files for the ACE Library and the original samples that came with the ACE Library.

#### 2.5.2 Documentation

The "Documentation" directory contains the Release Notes and ReadMe files for the AceXtreme SDK. The release notes contain information regarding each SDK version such as, the current firmware version for applicable DDC hardware, known issues and corrected defects. Other files included in this directory are the software license agreement and a link to this user's manual.

# 2.5.3 Drivers

The BU-69092Sx software package includes Operating system specific drivers based on the specific release version desired. Table 3 below details the driver file names for Windows (BU-69092S0) based on the DDC MIL-STD-1553 Hardware that are supported in the current version of the AceXtreme SDK.

|               | Table 3. Drivers of DDC Hardware                                                                                                               |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------|