## Total-ACE<sup>®</sup> Complete MIL-STD-1553 Solution

Model: BU-648X3T/U/H/i8

#### Data Sheet

Save board space and simplify your 1553 design and layout with the world's first fully integrated MIL-STD-1553 component, complete with 1553 protocol, memory, transceivers, and isolation transformers—all in one small plastic BGA package with direct and/or transformer coupled 1553 connections inside.

#### **Applications**

- Mission Computers

- Digital Data Recorders

- LRU's

- Displays

- Radios/Modems

- Radar Systems/Situational Awareness

- Ground Vehicles

- Commercial Aerospace

#### Need a Custom Solution?

DDC can customize designs for all products, ranging from simple modifications of standard products to fully customized solutions for commercial, military, aerospace, and industrial applications.

For more information: www.ddc-web.com/BU-64843T

### DDC's Data Networking Solutions

MIL-STD-1553 | ARINC 429 | Fibre Channel | Ethernet

As the leading global supplier of data bus components, boards, modules, computers, and software solutions for the military and commercial aerospace markets, DDC's data bus networking solutions encompass the full range of data interface protocols to support the real-time processing demands of field-critical data networking between systems and subsystems on the platform. These products, along with our traditional MIL-STD-1553 solutions, represent a wide and flexible array of performance and cost solutions, enabling DDC to support multi-generational programs.

Whether employed in increased bandwidth, high-speed serial communications, or traditional avionics and ground support applications, DDC's data bus solutions fulfill the expanse of military, civil aerospace, and space requirements including reliability, determinism, low CPU utilization, real-time performance, and ruggedness within harsh environments. Our use of in-house intellectual property ensures superior multi-generational support, independent of the life cycles of commercial devices. Moreover, we maintain software compatibility between product generations to protect our customers' investments in software development, system testing, and end-product qualification.

#### – MIL-STD-1553 –

DDC, the world leader in MIL-STD-1553 technology, provides the broadest selection of quality MIL-STD-1553 rugged embedded and lab grade computers, boards and components to meet your data conversion and data interface needs. Our 1553 data bus board solutions are integral elements of military, aerospace, and industrial applications. Our extensive line of military and space grade components provide MIL-STD-1553 interface solutions for microprocessors, PCI buses, and simple systems. Our 1553 data bus solutions are designed into almost every aircraft, helicopter, unmanned vehicle, missile programs, and space system that utilizes MIL-STD-1553.

#### ARINC 429

DDC has a wide assortment of quality ARINC 429 embedded and lab grade boards, LRUs, and components, to serve your data conversion and data interface needs. DDC's ARINC 429 components ensure the accurate and reliable transfer of flight-critical data. Our 429 interfaces support data bus development, validation, and the transfer of flight-critical data aboard commercial aerospace platforms.

#### – Fibre Channel

DDC has developed its line of high-speed Fibre Channel network access controllers and switches to support the realtime processing demands of field-critical data networking between sensors, computer nodes, data storage, displays, and weapons, for air, sea, and ground military vehicles. Fibre Channel's architecture is optimized to meet the performance, reliability, and demanding environmental requirements of embedded, real time, military applications, and designed to endure the multi-decade life cycle demands of military/aerospace programs.

#### – Ethernet

DDC offers convenient solutions to convert MIL-STD-1553, ARINC 429, and Ethernet protocol in any direction, in real-time, without a host computer, enabling seamless and cost saving multi-protocol connectivity for test and embedded applications.

#### – Extensions to MIL-STD-1553

DDC offers a wide variety of solutions based on extensions of MIL-STD-1553 for emerging aerospace applications. Turbo 1553 increases the data rate of 1553 from 1 Mbps to 5 Mbps while maintaining the architectural features of MIL-STD-1553. Hyper 1553 provides high speed communication (50 to 100+ Mbps) over MIL-STD-1553 buses while operating concurrently with legacy 1 Mbps 1553 (similar to ADSL for telephone networks).

#### - Form Factors, Software, & Drivers

DDC supplies MIL-STD-1553 and ARINC 429 board level products in a variety of form factors including USB, PCI-Express, PCMCIA, ExpressCard, AMC, PMC, XMC, PCI-104, PC/104-Plus, PC/104, PCI, cPCI, VME, and ISAbus boards. Our laboratory simulation and in-flight products include multi-function and single-function for system integration and production test environments. Our extensive line of military and space grade components provide MIL-STD-1553 interface solutions for microprocessors and simple systems. Our software is supplied in the form of menus, libraries, and drivers. We also offer additional software to expand our data networking range of options.

## TOTAL-ACE® COMPLETE MIL-STD-1553 SOLUTION BU-64843X/64863X DATA SHEET

The information provided in this Data Sheet is believed to be accurate; however, no responsibility is assumed by Data Device Corporation for its use, and no license or rights are granted by implication or otherwise connection therewith.

Specifications are subject to change without notice. Please visit our Web site at <u>http://www.ddc-web.com/</u> for the latest information.

All rights reserved. No part of this Data Sheet may be reproduced or transmitted in any form or by any mean, electronic, mechanical photocopying recording, or otherwise, without the prior written permission of Data Device Corporation.

105 Wilbur Place Bohemia, New York 11716-2426 Tel: (631) 567-5600, Fax: (631) 567-7358 World Wide Web - <u>http://www.ddc-web.com</u>

For Technical Support - 1-800-DDC-5757 ext. 7771 United Kingdom - Tel: +44-(0)1635-811140, Fax: +44-(0)1635-32264 France - Tel: +33-(0)1-41-16-3424, Fax: +33-(0)1-41-16-3425 Germany Tel: +49-(0)89-15 00 12-11, Fax: +49-(0)89-15 00 12-22 Japan - Tel: +81-(0)3-3814-7688, Fax: +81-(0)3-3814-7689 Asia - Tel: +65-6489-4801 India - Tel: +91 080 301 10 200

© 2008 Data Device Corp.

| Revision | Date    | Pages                              | Description                                                                                                                                                                                                                                       |

|----------|---------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A        | 5/2009  | All                                | Initial Release                                                                                                                                                                                                                                   |

| В        | 01/2010 | -                                  | Rev Skipped – Document Error.                                                                                                                                                                                                                     |

| C        | 02/2010 | 1-4, 38,40 - 43,<br>61             | Added lead-free version of product to document.<br>Updated figures 1, 12, &15. Updated table 1 and<br>tables for figures 13 & 14. Updated Ordering<br>Information.                                                                                |

| D        | 3/2010  | All                                | 64K version added.                                                                                                                                                                                                                                |

| E        | 05/2010 | 4                                  | Changed min storage temp from -55° to -65°                                                                                                                                                                                                        |

| F        | 6/2010  | 3, 43                              | Updated Current Drain, Power Dissipation, and<br>Hottest Die specs in Table 1, Updated Table 47                                                                                                                                                   |

| G        | 11/2010 | 4                                  | renaming from "SOLDERING" to<br>"SOLDERING/MOUNTING" and below the<br>information on reflow temperatures included the<br>following Refer to DDC's Application Note<br>#A/N49 "BGA User's Guide" for additional<br>important mounting information. |

| н        | 6/2011  | All                                | Updated to new format. Updated RT-Only information                                                                                                                                                                                                |

| J        | 11/2011 | 8, 85, 87, 95,99                   | Updated Tables 1, 49, 51, 55, 56                                                                                                                                                                                                                  |

| к        | 07/2012 | 6, 7, 12, 14, 93,<br>106           | Updated Table 1, added the BU-64863T(U)8 option.                                                                                                                                                                                                  |

| L        | 11/2012 | 3, 10, 11, 82, 83,<br>86, 106, 107 | Added -1xx -55 to +125C option and Rev B power numbers. Updated Figure 18.                                                                                                                                                                        |

| М        | 12/2012 | 10                                 | Updated max storage temperature                                                                                                                                                                                                                   |

| N        | 7/2017  | 7, 10, 92                          | Corrected typo "BU-64863X8" to "BU-64843X8"<br>Corrected typo ". DTGRT" to ". DTREQ". Added<br>Max peak body temperature to table 1.                                                                                                              |

|          |         |                                    |                                                                                                                                                                                                                                                   |

|          |         |                                    |                                                                                                                                                                                                                                                   |

|          |         |                                    |                                                                                                                                                                                                                                                   |

| 1 P  | REFACE                                                     | 1        |

|------|------------------------------------------------------------|----------|

| 1.1  | Text Usage                                                 | 1        |

| 1.2  | Special Handling and Cautions                              | 1        |

| 1.3  | Trademarks                                                 | 1        |

| 1.4  | What is included in this data sheet?                       | 1        |

| 1.5  | Technical Support                                          | 2        |

|      |                                                            | •        |

|      |                                                            |          |

| 2.1  | Features                                                   | 3        |

| 3 IN | NTRODUCTION                                                | .12      |

| 3.1  | Supporting Documentation                                   |          |

| 3.2  | Total-ACE in Simple System RT (SSRT) Mode                  |          |

| 3.3  | Test Components                                            |          |

| 3.4  | Transceiverless "Compatible" Version of Total-ACE          |          |

| 3.5  | Transceivers                                               |          |

| 3.6  | Built-In Isolation Transformers                            |          |

| 3.7  | Register and Memory Addressing                             |          |

| 3.8  | Internal Registers                                         |          |

|      |                                                            |          |

| 4 N  | ION-TEST REGISTER FUNCTION SUMMARY                         | .32      |

| 4.1  | Interrupt Mask Registers #1 and #2                         | .32      |

| 4.2  | Configuration Registers #1 and #2                          | .32      |

| 4.3  | Start/Reset Register                                       | .32      |

| 4.4  | BC/RT Command Stack Register                               | .32      |

| 4.5  | BC Instruction List Pointer Register                       |          |

| 4.6  | BC Control Word/RT Subaddress Control Word Register        | .32      |

| 4.7  | Time Tag Register                                          |          |

| 4.8  | Interrupt Status Registers #1 and #2                       | .33      |

| 4.9  | Configuration Registers #3, #4, and #5                     | .33      |

| 4.10 | RT/Monitor Data Stack Address Register                     | .33      |

| 4.11 | BC Frame Time Remaining Register                           | .34      |

| 4.12 | BC Time Remaining to Next Message Register                 | .34      |

| 4.13 | BC Frame Time / RT Last Command / MT Trigger Word Register | .34      |

|      | BC Initial Instruction List Point Register                 |          |

| 4.15 | RT Status Word Register and BIT Word Registers             | .34      |

| 4.16 | Configuration Registers #6 and #7                          | .34      |

| 4.17 | BC Condition Code Register                                 | .35      |

| 4.18 | BC General Purpose Flag Register                           | .35      |

|      | BIT Test Status Register                                   |          |

|      | BC General Purpose Queue Pointer                           |          |

| 4.21 | RT/MT Interrupt Status Queue Pointer                       | .35      |

|      |                                                            | <b>.</b> |

|      | SUS CONTROLLER (BC) ARCHITECTURE                           |          |

| 5.1  | Enhanced BC Mode: Message Sequence Control                 | .37      |

| 5.2      | OP Codes                                                           | 38  |

|----------|--------------------------------------------------------------------|-----|

| 5.3      | BC Message Sequence Control                                        | 45  |

| 5.4      | Execute and Flip Operation                                         | 45  |

| 5.5      | General Purpose Queue                                              | 48  |

|          |                                                                    |     |

|          | EMOTE TERMINAL (RT) ARCHITECTURE                                   |     |

| 6.1      | RT Memory Organization                                             |     |

| 6.2      | RT Memory Management                                               |     |

| 6.3      | Single Buffered Mode                                               |     |

| 6.4      | SUBADDRESS DOUBLE BUFFERING MODE                                   |     |

| 6.5      | CIRCULAR BUFFER MODE                                               |     |

| 6.6      | GLOBAL CIRCULAR BUFFER                                             |     |

| 6.7      | RT DESCRIPTOR STACK                                                | 56  |

| 6.8      | RT INTERRUPTS                                                      |     |

| 6.9      | RT COMMAND ILLEGALIZATION                                          |     |

| 6.10     | BUSY BIT                                                           | 61  |

|          | RT ADDRESS                                                         |     |

| 6.12     | RT BUILT-IN-TEST (BIT) WORD                                        | 62  |

| 6.13     | RT AUTO-BOOT OPTION                                                | 62  |

| 6.14     | OTHER RT FEATURES                                                  | 62  |

|          |                                                                    |     |

|          |                                                                    | -   |

| 7.1      | WORD MONITOR MODE                                                  |     |

| 7.2      | WORD MONITOR MEMORY MAP                                            |     |

| 7.3      | WORD MONITOR TRIGGER                                               |     |

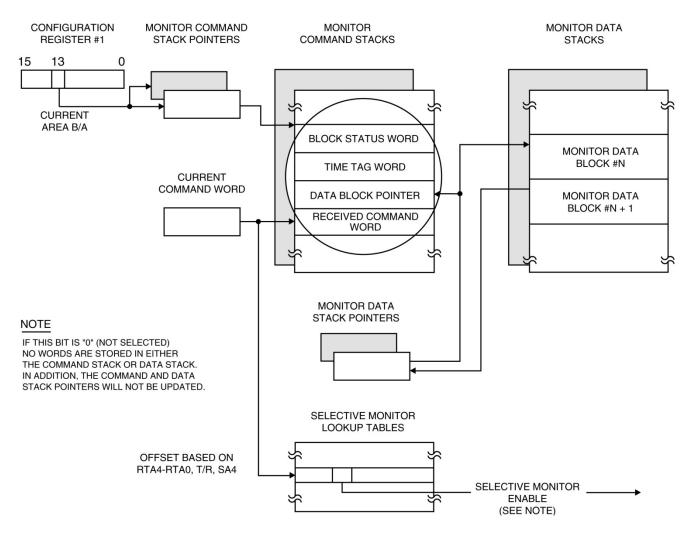

| 7.4      | SELECTIVE MESSAGE MONITOR MODE                                     |     |

| 7.5      | MONITOR SELECTION FUNCTION                                         |     |

| 7.6      | SELECTIVE MESSAGE MONITOR MEMORY ORGANIZATION                      |     |

| 7.7      | MONITOR INTERRUPTS                                                 |     |

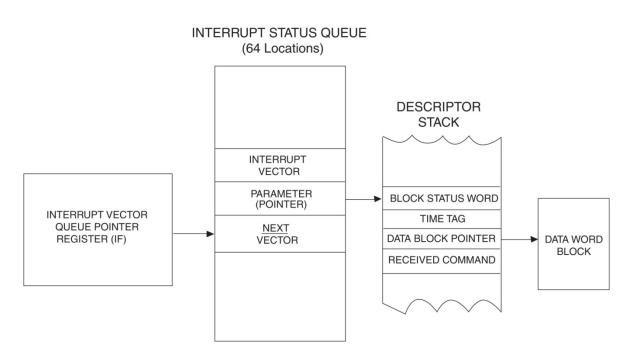

| 7.8      | INTERRUPT STATUS QUEUE                                             | 68  |

| 8 M      | IISCELLANEOUS                                                      | 70  |

|          |                                                                    |     |

| 8.1      | CLOCK INPUT                                                        |     |

| 8.2      |                                                                    |     |

| 8.3      |                                                                    |     |

| 8.4      |                                                                    |     |

| 8.5      | BUILT-IN TEST                                                      |     |

| 8.6      |                                                                    |     |

| 8.7      | RELOCATABLE MEMORY MANAGEMENT LOCATIONS                            |     |

| 8.8      |                                                                    |     |

| 8.9      | +3.3 VOLT INTERFACE TO MIL-STD-1553 BUS                            |     |

|          | THERMAL MANAGEMENT FOR TOTAL-ACE (312-BALL BGA PACKAGE)            |     |

| 8.11     | Ball Grid Array Package - Signal Descriptions by Functional Groups | 87  |

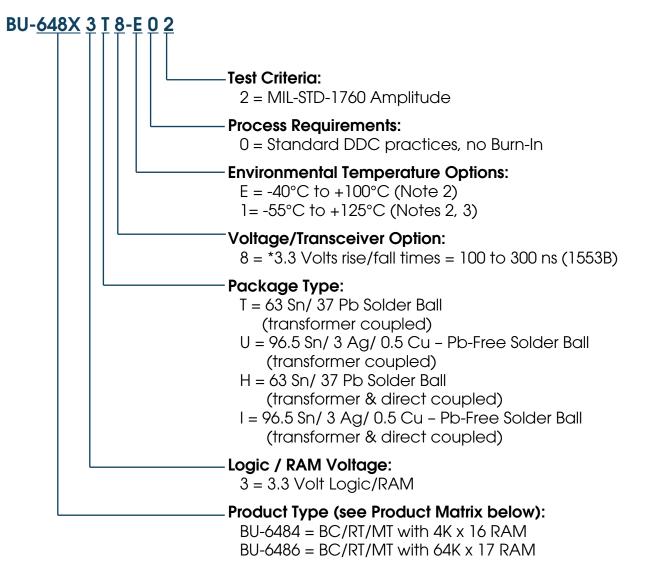

| <u> </u> | RDERING INFORMATION                                                | 109 |

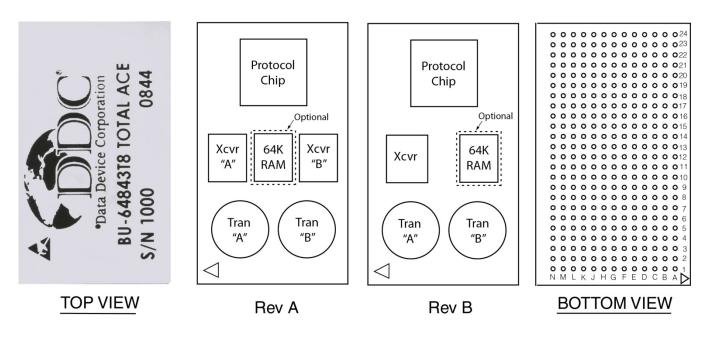

| Figure 1. BU-648X3X Total-ACE                                       | 4   |

|---------------------------------------------------------------------|-----|

| Figure 2. BU-64843T Total-ACE Architecture                          | 5   |

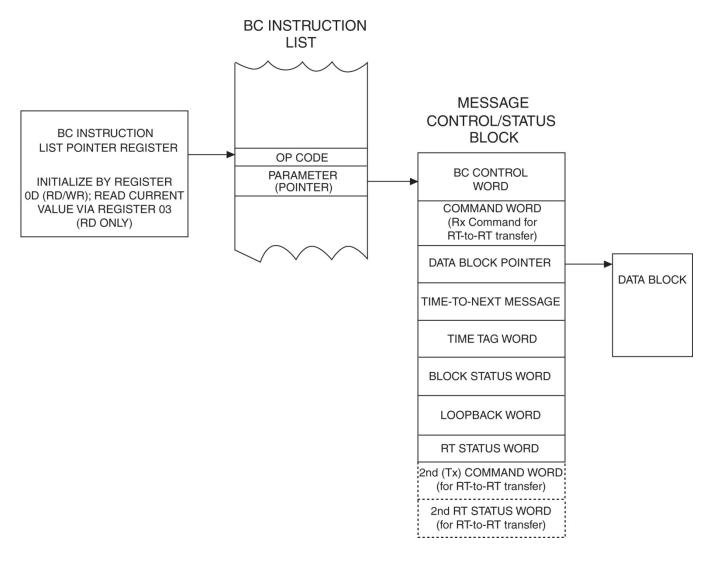

| Figure 3. BC Message Sequence Control                               | 36  |

| Figure 4. BC OP Code Format                                         | 38  |

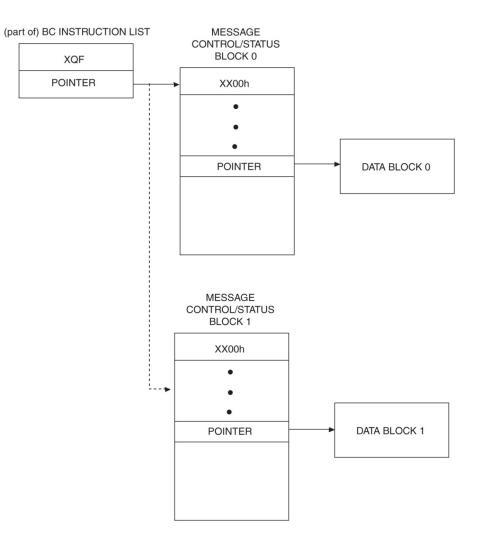

| Figure 5. EXECUTE and FLIP (XQF) Operation                          | 47  |

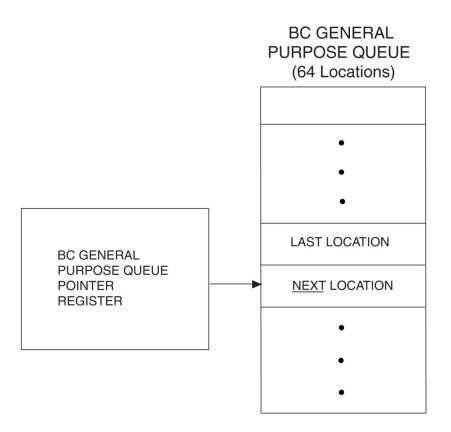

| Figure 6. BC General Purpose Queue                                  | 48  |

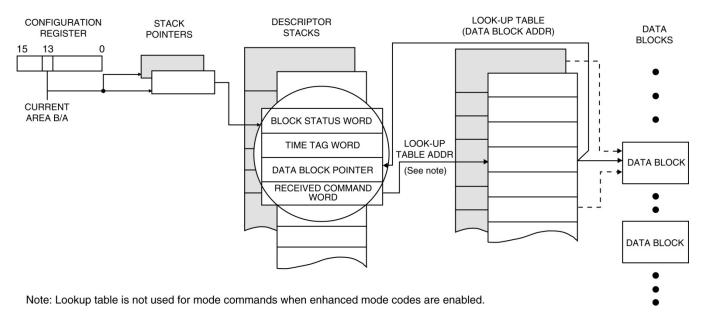

| Figure 7. RT Single Buffered Mode                                   | 53  |

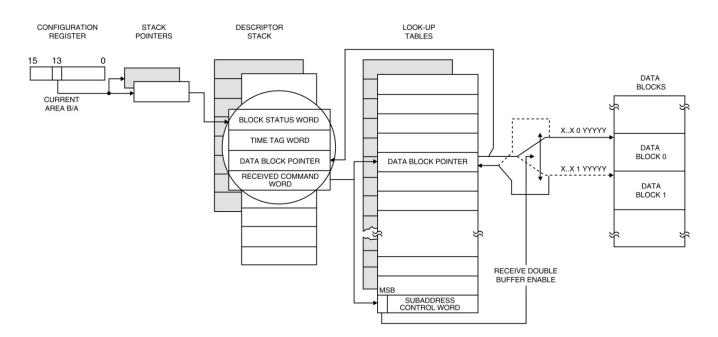

| Figure 8. RT Double Buffered Mode                                   | 54  |

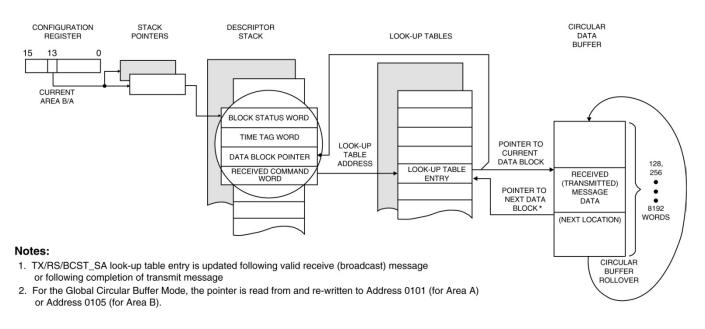

| Figure 9. RT Circular Buffered Mode                                 | 55  |

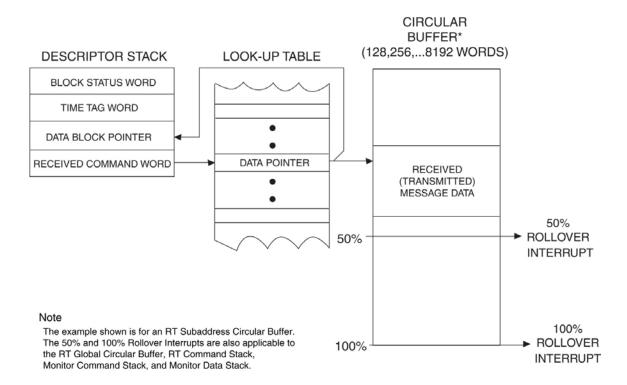

| Figure 10. 50% and 100% Rollover Interrupts                         | 59  |

| Figure 11. RT (and Monitor) Interrupt Status Queue                  | 59  |

| Figure 12. Selective Message Monitor Memory Management              | 69  |

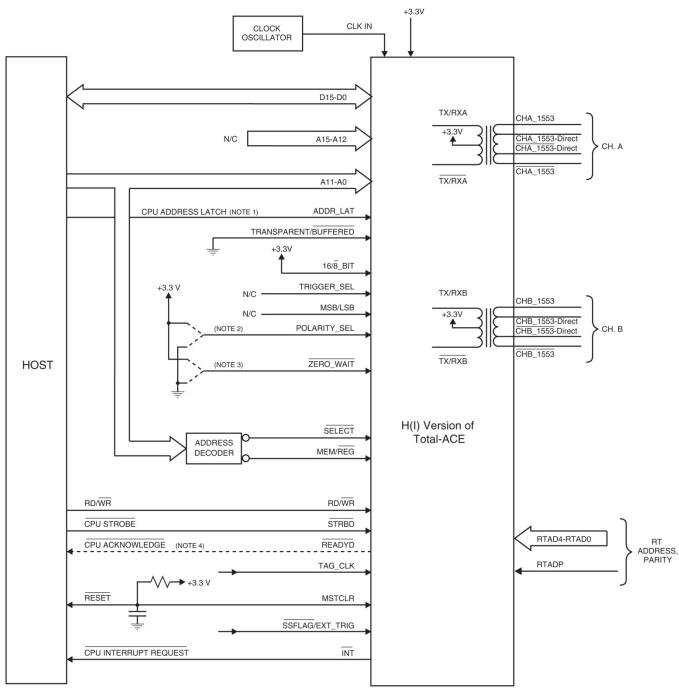

| Figure 13. Host Processor Interface – 16-Bit Buffered Configuration | 75  |

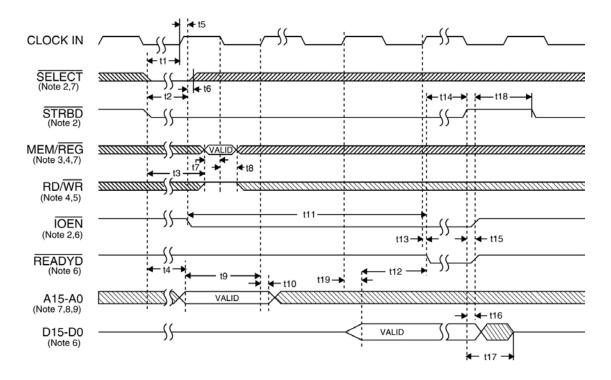

| Figure 14. CPU Reading RAM/Register (16-BIT Buffered, Nonzero Wait) | 76  |

| Figure 15. CPU Writing RAM/Register (16-BIT Buffered, Nonzero Wait) | 79  |

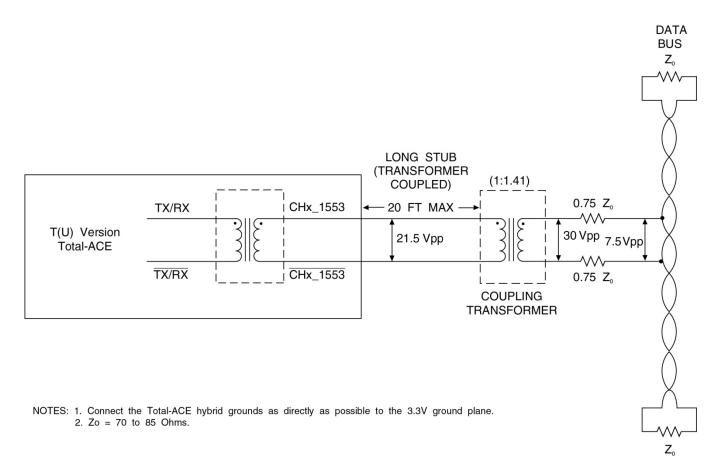

| Figure 16. T(U) Version Total-ACE Interface to MIL-STD-1553 Bus     | 82  |

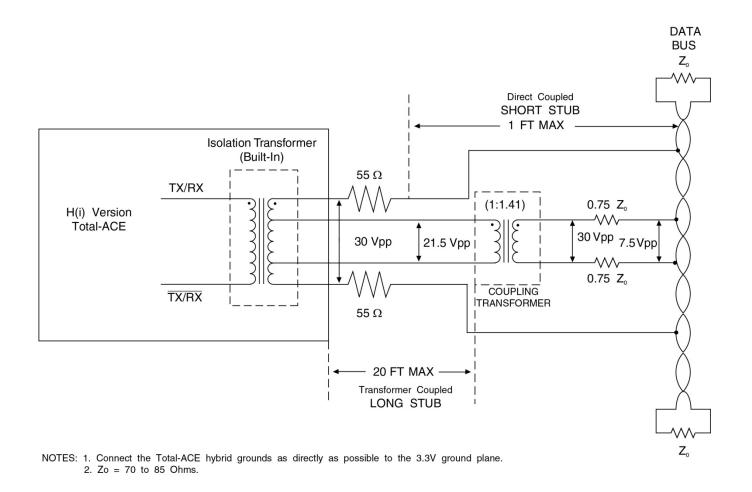

| Figure 17. H(I) Version Total-ACE Interface to MIL-STD-1553 Bus     | 83  |

| Figure 18. Ball Locations for Total-ACE (312-Ball BGA Package)      | 86  |

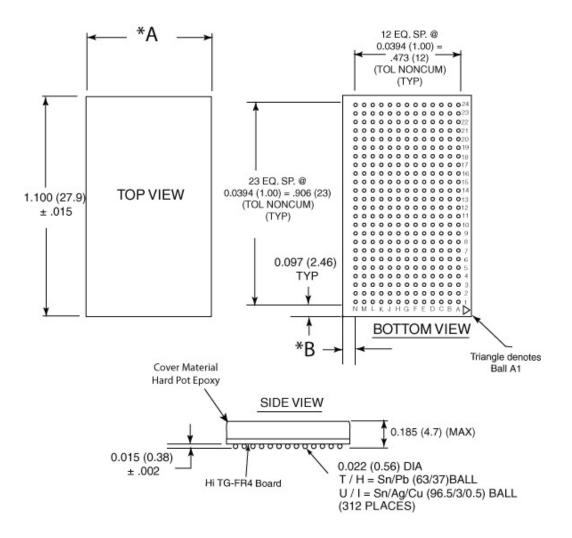

| Figure 19. Mechanical Outline Drawing for Total-ACE BGA Packages    | 107 |

| Table 1. BU-64843T Specification Table                                                    | 6    |

|-------------------------------------------------------------------------------------------|------|

| Table 2. Address Mapping                                                                  | 15   |

| Table 3. Interrupt Mask Register #1 (Read/Write 00H)                                      | 17   |

| Table 4. Configuration Register #1 (Read/Write 01H)                                       |      |

| Table 5. Configuration Register #2 (Read/Write 02H)                                       | 19   |

| Table 6. Start/Reset Register (Write 03H)                                                 |      |

| Table 7. BC/RT Command Stack Pointer Reg.(Read 03H)                                       | 19   |

| Table 8. BC Control Word Register (Read/Write 04H)                                        | 20   |

| Table 9. RT Subaddress Control Word (Read/Write 04H)                                      |      |

| Table 10. Time Tag Register. (Read/Write 05H)                                             |      |

| Table 11. Interrupt Status Register #1 (Read 06H)                                         | 21   |

| Table 12. Configuration Register #3 (Read/Write 07H)                                      | 21   |

| Table 13. Configuration Register #4 (Read/Write 08H)                                      | 22   |

| Table 14. Configuration Register #5 (Read/Write 09H)                                      | 22   |

| Table 15. RT/Monitor Data Stack Address Register (Read/Write 0AH)                         | 22   |

| Table 16. BC Frame Time Remaining Register (Read/Write 0BH)                               | 23   |

| Table 17. BC Frame Time Remaining Register (Read/Write 0CH)                               | 23   |

| Table 18. BC Frame Time/RT Last Command/MT Trigger Register (Read/Write 0DH)              | 23   |

| Table 19. RT Status Word Register (Read/Write 0EH)                                        | 23   |

| Table 20. RT BIT Word Register (Read/Write 0FH)                                           | 24   |

| Table 21. Configuration Register #6 (Read/Write 18H)                                      | 24   |

| Table 22. Configuration Register #7 (Read/Write 19H)                                      | 25   |

| Table 23. BC Condition Register (Read 1BH)                                                | 25   |

| Table 24. BC General Purpose Flag Register (Write 1BH)                                    | 26   |

| Table 25. BIT Test Status Flag Register (Read 1CH)                                        | 26   |

| Table 26. Interrupt Mask Register #2 (Read/Write 1DH)                                     | 27   |

| Table 27. Interrupt Status Register #2 (Read 1EH)                                         |      |

| Table 28. BC General Purpose Queue Pointer Register RT, MT Interrupt Status Queue Pointer | nter |

| Register (Read/Write 1FH)                                                                 |      |

| Table 29. BC Mode Block Status Word                                                       | 28   |

| Table 30. RT Mode Block Status Word                                                       | 29   |

| Table 31. 1553 Command Word                                                               |      |

| Table 32. Word Monitor Identification Word                                                | 30   |

| Table 33. Message Monitor Mode Block Status Word                                          | 30   |

| Table 34. RT/Monitor Interrupt Status Word (For Interrupt Status Queue)                   | 31   |

| Table 35. 1553B Status Word                                                               | 31   |

| Table 36. BC Operations for Message Sequence Control                                      |      |

| Table 37. BC Condition Codes                                                              |      |

| Table 38. Typical RT Memory Map (Shown for 4K RAM)                                        | 50   |

| Table 39. RT Look-up Tables                                                               | 51   |

| Table 40. RT Subaddress Control Word – Memory Management Options                          | 52   |

| Table 41. Illegalization Table Memory Map                                                 |      |

| Table 42. RT BIT Word                                                                     |      |

| Table 43. Typical Word Monitor Memory Map                                                 |      |

|                                                                                           |      |

| Table 44. RT BIT Word                                                             | 66    |

|-----------------------------------------------------------------------------------|-------|

| Table 45. Typical Selective Message Monitor Memory Map (shown for 4K RAM for "Mon | nitor |

| only" mode)                                                                       | 68    |

| Table 46. Power and Ground                                                        | 87    |

| Table 47. 1553 Stub Connection                                                    | 87    |

| Table 48. Mandatory Additional Connections & Interface to External Transceiver    | 88    |

| Table 49. Data Bus                                                                | 89    |

| Table 50. Processor Address Bus                                                   | 90    |

| Table 51. Processor Interface Control                                             | 91    |

| Table 52. RT Address                                                              | 95    |

| Table 53. Miscellaneous                                                           |       |

| Table 54. No User Connections                                                     | 97    |

| Table 55. Total-ACE With 4K RAM (BU-6484X) All Versions Pinout                    |       |

| Table 56. Total-ACE With 64K RAM (BU-6486X) All Versions Pinout                   | 102   |

| Table 57. Total-ACE BU-64843T8-600 (BGA Package) "Daisy Chain" Mechanical Sam     | ple   |

| Connections                                                                       | 106   |

#### 1 PREFACE

This data sheet uses typographical conventions to assist the reader in understanding the content. This section will define the text formatting used in the rest of the data sheet.

#### 1.1 Text Usage

- **BOLD**–indicates important information and table, figure, and chapter references.

- BOLD ITALIC-designates DDC Part Numbers.

- Courier New-indicates code examples.

- <...> indicates user-entered text or commands.

#### **1.2 Special Handling and Cautions**

Warnings: Turn off power to the computer hardware and unplug from wall.

Ensure that standard ESD precautions are followed. As a minimum, one hand should be grounded to the power supply in order to equalize the static potential.

Do not store disks in environments exposed to excessive heat, magnetic fields or radiation.

#### 1.3 Trademarks

All trademarks are the property of their respective owners.

#### 1.4 What is included in this data sheet?

This data sheet contains a complete description of component.

#### 1.5 Technical Support

In the event that problems arise beyond the scope of this data sheet, you can contact DDC by the following:

US Toll Free Technical Support: 1-800-DDC-5757, ext. 7771

Outside of the US Technical Support: 1-631-567-5600, ext. 7771

Fax: 1-631-567-5758 to the attention of DATA BUS Applications

DDC Website: www.ddc-web.com/ContactUs/TechSupport.aspx

Please note that the latest revisions of Software and Documentation are available for download at DDC's Web Site, <u>www.ddc-web.com</u>.

#### 2 OVERVIEW

The Total-ACE is a complete and compact solution to MIL-STD-1553 applications. With a footprint of just 0.6 (transformer-coupled version) or 0.7 (transformer & direct coupled version) inches by 1.10 inches, it is the world's first MIL-STD-1553 terminal, including the isolation transformers, fully integrated into a single BGA package. The device is powered entirely by +3.3 volts.

Ideal for extended temperature range applications where PC board space is at a premium, the Total-ACE is available in a 312-ball (24 x 13 matrix) BGA package, and is rated for -40°C to +100°C operation at case.

The Total-ACE is software and architecturally compatible with DDC's Enhanced Mini-ACE series of devices. It integrates dual transceivers, dual transformers, protocol engine and either 4K or 64K words of internal RAM. The Total-ACE's flexible processor interface allows direct connection with little or no glue logic to a variety of 8, 16 and 32-bit processors.

The advanced architecture is key to the Total-ACE series' high performance. The advanced bus controller architecture gives the Total-ACE a high degree of flexibility and autonomy. This creates advantages in a number of areas: improving message scheduling control, minimizing host overhead for asynchronous message insertion, facilitating bulk data transfers and double buffering, message retry and bus switching strategies, and data logging and fault reporting. In addition, its remote terminal architecture provides flexibility in meeting all common MIL-STD-1553 protocols. RT data buffering and interrupt options offer support for synchronous and asynchronous messaging, ensure data sample consistency, and support bulk data transfers. The Total-Ace's Monitor mode includes filtering based on RT Address and Subaddress, and provides true message monitoring.

#### 2.1 Features

- World's First, Fully Integrated, MIL-STD-1553 Terminal Solution, including Isolation Transformers

- Small Package 312 Ball BGA (1.1 in x 0.6 in, or 1.1 in x 0.7 in)

- Fully Compatible with Enhanced Mini-ACE<sup>®</sup> Software and Architecture

- Generic 8 or 16-bit Processor Interface

- Available in Full Military Temperature Range: -55°C to +125°C

- DO-254 Certifiable

- +3.3 Volt Only

- 4K x 16 or 64K x 17 RAM

- 0.185" Max Height

- Compliance with MIL-STD-1553A/B Notice 2, STANAG-3838, and MIL-STD-1760

- Highly Autonomous BC Architecture

- Built-In Message Sequence Controller with 20-Instruction Set

- Flexible RT Buffering with Single, Double, and Circular Buffering

- Selective Message Monitor with Filtering

- 50% Rollover Interrupts for Stacks and Circular Buffers

- Software and Register Compatible to ACE and Enhanced Mini-ACE devices

- Optional RT-Only Operation for Safety-Critical Applications

- Applications Include:

- Mission Computers

- Digital Data Recorders

- LRU's

- Radios/Modems

- Displays

- Ground Vehicles

- Commercial Aerospace

- Radar Systems/Situational Awareness

Figure 1. BU-648X3X Total-ACE

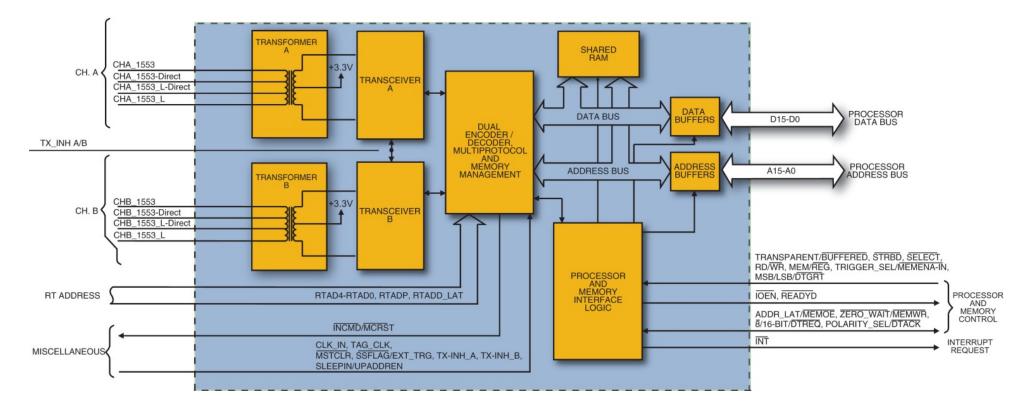

Figure 2. BU-64843T Total-ACE Architecture

| Table 1. BU-64843T Specification Table                       |      |     |      |       |  |

|--------------------------------------------------------------|------|-----|------|-------|--|

| PARAMETER                                                    | MIN  | ТҮР | MAX  | UNITS |  |

| ABSOLUTE MAXIMUM RATING                                      |      |     |      |       |  |

| Supply Voltage (Note 11)                                     |      |     |      |       |  |

| • BU-64843X8-XX2                                             |      |     |      |       |  |

| Logic +3.3 V                                                 | -0.3 |     | 6.0  | V     |  |

| • BU-64863X8-XX2                                             |      |     |      |       |  |

| Logic +3.3V                                                  | -0.3 |     | 4.1  | V     |  |

| <ul> <li>Transceivers +3.3V (not during transmit)</li> </ul> | -0.3 |     | 6.0  | V     |  |

| <ul> <li>Transceivers +3.3V (during transmit)</li> </ul>     | -0.3 |     | 4.5  | V     |  |

| Logic                                                        |      |     |      |       |  |

| +3.3V Logic Input Range                                      | -0.3 |     | 6.0  | V     |  |

| POWER SUPPLY REQUIREMENTS                                    |      |     |      |       |  |

| Voltages/Tolerances (Note 11)                                |      |     |      |       |  |

| • Logic +3.3V                                                | 3.00 | 3.3 | 3.60 | V     |  |

| • Transceivers +3.3V                                         | 3.14 | 3.3 | 3.46 | V     |  |

| Current Drain(Total Hybrid) (Note 13)                        |      |     |      |       |  |

| BU-64843X8-E02 Rev A                                         |      |     |      |       |  |

| <ul> <li>Idle w/transceiver SLEEPIN enabled</li> </ul>       |      | 32  | 48   | mA    |  |

| <ul> <li>Idle w/transceiver SLEEPIN disabled</li> </ul>      |      | 81  | 117  | mA    |  |

| <ul> <li>25% Transmitter Duty Cycle</li> </ul>               |      | 255 | 309  | mA    |  |

| <ul> <li>50% Transmitter Duty Cycle</li> </ul>               |      | 428 | 517  | mA    |  |

| 100% Transmitter Duty Cycle                                  |      | 776 | 931  | mA    |  |

| BU-64863H/i8-E02 Rev A                                       |      |     |      |       |  |

| <ul> <li>Idle w/transceiver SLEEPIN enabled</li> </ul>       |      | 34  | 51   | mA    |  |

| <ul> <li>Idle w/transceiver SLEEPIN disabled</li> </ul>      |      | 83  | 120  | mA    |  |

| <ul> <li>25% Transmitter Duty Cycle</li> </ul>               |      | 257 | 311  | mA    |  |

| <ul> <li>50% Transmitter Duty Cycle</li> </ul>               |      | 431 | 521  | mA    |  |

| 100% Transmitter Duty Cycle                                  |      | 781 | 937  | mA    |  |

| BU-64843X8-E02 Rev B, BU-64843X8-102                         |      |     |      |       |  |

| • Idle                                                       |      | 51  | 73   | mA    |  |

| <ul> <li>25% Transmitter Duty Cycle</li> </ul>               |      | 197 | 219  | mA    |  |

| <ul> <li>50% Transmitter Duty Cycle</li> </ul>               |      | 367 | 381  | mA    |  |

| 100% Transmitter Duty Cycle                                  |      | 685 | 703  | mA    |  |

| BU-64863T/U8-E02, BU-64863H/i8-E02 Rev B,                    |      |     |      |       |  |

| BU-64863X8-102                                               |      |     |      |       |  |

| • Idle                                                       |      | 53  | 76   | mA    |  |

| <ul> <li>25% Transmitter Duty Cycle</li> </ul>               |      | 199 | 221  | mA    |  |

| <ul> <li>50% Transmitter Duty Cycle</li> </ul>               |      | 370 | 385  | mA    |  |

| 100% Transmitter Duty Cycle                                  |      | 690 | 709  | mA    |  |

| Table 1. BU-64843T Specification Table                  |       |       |       |       |  |

|---------------------------------------------------------|-------|-------|-------|-------|--|

| PARAMETER                                               | MIN   | ТҮР   | MAX   | UNITS |  |

| POWER DISSIPATION                                       |       |       |       |       |  |

| TOTAL HYBRID(Note 13 & 14)<br>BU-64843X8-E02 Rev A      |       |       |       |       |  |

| Idle w/transceiver SLEEPIN enabled                      |       | 0.106 | 0.158 | W     |  |

| Idle w/transceiver SLEEPIN disabled                     |       | 0.267 | 0.386 | W     |  |

| <ul> <li>25% Transmitter Duty Cycle</li> </ul>          |       | 0.546 | 0.724 | W     |  |

| <ul> <li>50% Transmitter Duty Cycle</li> </ul>          |       | 0.821 | 1.116 | W     |  |

| 100% Transmitter Duty Cycle                             |       | 1.378 | 1.890 | W     |  |

| BU-64863H/i8-E02 Rev A                                  |       |       |       |       |  |

| <ul> <li>Idle w/transceiver SLEEPIN enabled</li> </ul>  |       | 0.112 | 0.168 | W     |  |

| <ul> <li>Idle w/transceiver SLEEPIN disabled</li> </ul> |       | 0.274 | 0.396 | W     |  |

| <ul> <li>25% Transmitter Duty Cycle</li> </ul>          |       | 0.552 | 0.732 | W     |  |

| 50% Transmitter Duty Cycle                              |       | 0.831 | 1.128 | W     |  |

| 100% Transmitter Duty Cycle                             |       | 1.394 | 1.910 | W     |  |

| BU-64843X8-E02 Rev B, BU-64843X8-102                    |       |       |       |       |  |

| • Idle                                                  |       | 0.170 | 0.269 | W     |  |

| 25% Transmitter Duty Cycle                              |       | 0.170 | 0.347 | Ŵ     |  |

| 50% Transmitter Duty Cycle                              |       | 0.381 | 0.509 | Ŵ     |  |

| 100% Transmitter Duty Cycle                             |       | 0.514 | 0.683 | W     |  |

| BU-64863T/U8-E02, BU-64863H/i8-E02 Rev B,               |       |       |       |       |  |

| BU-64863X8-102                                          |       |       |       |       |  |

| • Idle                                                  |       | 0.177 | 0.279 | W     |  |

| 25% Transmitter Duty Cycle                              |       | 0.177 | 0.355 | Ŵ     |  |

| 50% Transmitter Duty Cycle                              |       | 0.391 | 0.521 | Ŵ     |  |

| 100% Transmitter Duty Cycle                             |       | 0.530 | 0.703 | Ŵ     |  |

| ACTIVE TRANSCEIVER (HOTTEST DIE)                        |       |       |       |       |  |

| BU-64843X8-E02 Rev A                                    |       |       |       |       |  |

| <ul> <li>100% Transmitter Duty Cycle</li> </ul>         |       | 1.103 | 1.494 | W     |  |

| BU-64863H/i8-E02 Rev A                                  |       |       |       |       |  |

| <ul> <li>100% Transmitter Duty Cycle</li> </ul>         |       | 1.117 | 1.512 | W     |  |

| BU-64863T/U8-E02, BU-648x3H/i8-E02 Rev B,               |       |       |       |       |  |

| BU-648X3X8-102                                          |       |       |       |       |  |

| 100% Transmitter Duty Cycle                             |       | 0.420 | 0.540 | W     |  |

| RECEIVER                                                |       |       |       |       |  |

| Differential Input Impedance (Note 1 – 6)               |       |       |       |       |  |

| +3.3V Transformer Coupled                               | 1.0   |       |       | kΩ    |  |

| +3.3V Direct Coupled                                    | 2.0   |       |       | kΩ    |  |

| Threshold Voltage                                       |       |       |       |       |  |

| Transformer Coupled, Measured on Stub                   | 0.200 |       | 0.860 | Vp-р  |  |

| Direct Coupled, Measured on Stub                        | 0.280 |       | 1.20  | Vp-p  |  |

| Common-Mode Voltage                                     |       |       | ±10   | Vpeak |  |

| Table 1. BU-64843T Specification Table                                            |                |      |                |       |  |

|-----------------------------------------------------------------------------------|----------------|------|----------------|-------|--|

| PARAMETER                                                                         | MIN            | TYP  | MAX            | UNITS |  |

| TRANSMITTER                                                                       |                |      |                |       |  |

| Differential Output Voltage                                                       |                |      |                |       |  |

| <ul> <li>Direct Coupled Across 35Ω,<br/>Measured on Bus</li> </ul>                | 6              | 7.2  | 9.0            | Vp-р  |  |

| <ul> <li>Transformer Coupled Across 70Ω,<br/>Measured on Bus (Note 12)</li> </ul> | 20             | 21.5 | 27             | Vp-р  |  |

| Output Noise, Differential                                                        |                |      | 14             | mVRMS |  |

| Output Offset Voltage, Transfomer Coupled Across $70\Omega$                       | -250           |      | 250            | mVp   |  |

| Rise/Fall Time                                                                    | -250           | 150  | 300            | nsec  |  |

|                                                                                   | 100            | 100  | 300            | 11360 |  |

| LOGIC                                                                             |                |      |                |       |  |

|                                                                                   | 2.1            |      |                | V     |  |

| All signals except CLK_IN<br>CLK_IN                                               | 2.1<br>0.8•Vcc |      |                | V     |  |

| GER_IN                                                                            | 0.0-000        |      |                | v     |  |

|                                                                                   |                |      | 0.7            | V     |  |

| All signals except CLK_IN                                                         |                |      | 0.7<br>0.2•Vcc | V     |  |

| CLK_IN                                                                            |                |      | 0.2•VCC        | v     |  |

| Schmidt Hysteresis                                                                |                |      |                |       |  |

| All signals except CLK_IN                                                         | 0.4            |      |                | V     |  |

| CLK_IN                                                                            | 0.8            |      |                | V     |  |

| I <sub>IH</sub> , I <sub>IL</sub>                                                 |                |      |                |       |  |

| All signrals except CLK_IN                                                        |                |      |                |       |  |

| $I_{\rm IH} (V_{\rm cc} = 3.6 V, V_{\rm IN} = 2.5 V)$                             | -100           | -32  | -10            | μΑ    |  |

| $I_{_{\rm IL}} (V_{_{\rm CC}} = 3.6V, V_{_{\rm IN}} = 0.0V)$                      | -340           | -50  | -20            | μΑ    |  |

|                                                                                   |                |      |                |       |  |

| CLK_IN                                                                            | -10            |      | 10             | μA    |  |

| l <sub>in</sub><br>l <sub>ic</sub>                                                | -10            |      | 10             | μΑ    |  |

| ΊL                                                                                |                |      |                | P. 1  |  |

| $V_{_{ m OH}} (V_{_{ m CC}} = 3.0 V, V_{_{ m IH}} = 2.7 V,$                       |                |      |                |       |  |

| $(V_{IL} = 0.2V, I_{OH} = max)$                                                   | 2.4            |      |                | V     |  |

| $V_{_{OL}}$ ( $V_{_{CC}}$ = 3.0V, $V_{_{IH}}$ = 2.7V,                             |                |      |                |       |  |

| $(V_{IL} = 0.2V, I_{OH} = max)$                                                   |                |      | 0.5            | V     |  |

| IOL (VCC = 3.0V)                                                                  | 2.2            |      |                | mA    |  |

| IOH (VCC = 3.0V)                                                                  |                |      | -2.2           | mA    |  |

| CI (Input Capacitance)                                                            |                | 50   |                | pF    |  |

| CIO (Bidirectional signal input capacitance)                                      |                | 50   |                | pF    |  |

| Table 1. BU-64843T Specification Table                |        |            |              |       |  |

|-------------------------------------------------------|--------|------------|--------------|-------|--|

| PARAMETER                                             | MIN    | ТҮР        | MAX          | UNITS |  |

| CLOCK INPUT                                           |        |            |              |       |  |

| Frequency                                             |        |            |              |       |  |

| Nominal Values                                        |        |            |              |       |  |

| - Default Mode                                        |        | 16.0       |              | MHz   |  |

| - Option                                              |        | 12.0       |              | MHz   |  |

| - Option                                              |        | 10.0       |              | MHz   |  |

| - Option                                              |        | 20.0       |              | MHz   |  |

| Long Term Tolerance                                   |        |            |              |       |  |

| 1553A Compliance                                      | -0.01  |            | 0.01         | %     |  |

| 1553B Compliance                                      | -0.10  |            | 0.10         | %     |  |

| Short Term Tolerance, 1 second                        |        |            |              |       |  |

| 1553A Compliance                                      | -0.001 |            | 0.001        | %     |  |

| 1553B Compliance                                      | -0.01  |            | 0.01         | %     |  |

| Duty Cycle                                            | 40     |            | 60           | %     |  |

| 15553 MESSAGE TIMING                                  |        |            |              |       |  |

| Completion of CPU Write (BC Start)-to-Start of        |        |            |              |       |  |

| First Message for Non-enhanced BC Mode                | 2.5    |            |              | μs    |  |

| BC Intermessage Gap (Note 7)                          |        |            |              |       |  |

| Non-enhanced (Mini-ACE compatible) BC                 |        |            |              |       |  |

| mode                                                  |        | 9.5        |              | μs    |  |

| Enhanced BC mode (Note 8)                             |        | 10 to 10.5 |              | μs    |  |

| BC/RT/MT Response Timeout (Note 9)                    |        |            |              |       |  |

| • 18.5 nominal                                        | 17.5   | 18.0       | 19.5         | μs    |  |

| • 22.5 nominal                                        | 21.5   | 22.5       | 23.5         | μs    |  |

| • 50.5 nominal                                        | 49.5   | 50.5       | 20.0<br>51.5 |       |  |

|                                                       | 49.5   | 129.5      | 131          | μs    |  |

| • 128.0 nominal                                       | 121    | 129.0      | 131          | μs    |  |

| RT Response Time (mid-parity to mid-sync)             | 4      |            | 7            | μs    |  |

| (Note 10)                                             |        |            |              |       |  |

| Transmitter Watchdog Timeout                          |        | 660.5      |              | μs    |  |

| THERMAL                                               |        |            |              |       |  |

| TOTAL-ACE BGA                                         |        |            |              |       |  |

| 312-ball BGA Package                                  |        |            |              |       |  |

| (See Thermal Management section 8.10)                 |        |            |              |       |  |

| Active Transceiver (Hottest Die)                      |        |            |              |       |  |

| BU-648X3T/U8 Transformer Coupled                      |        |            |              |       |  |

| Single-Tap Versions                                   |        |            |              |       |  |

| • Junction-to-Ambient ( $\theta_{JA}$ via simulation) |        |            |              |       |  |

| - Per JESD 51-2 standard at 25°C                      |        |            |              |       |  |

| $\theta_{JA}$ in Still Air                            |        | 37.7       |              | °C/W  |  |

| Table 1. BU-64843T Specification Table                         |     |              |      |              |  |

|----------------------------------------------------------------|-----|--------------|------|--------------|--|

| PARAMETER                                                      | MIN | ТҮР          | MAX  | UNITS        |  |

| THERMAL (con't)                                                |     |              |      |              |  |

| - Per JESD 51-6 standard at 25°C                               |     |              |      |              |  |

| θ <sub>JA</sub> @1M/S                                          |     | 30.5         |      | °C/W         |  |

| θ <sub>JA</sub> @2M/S                                          |     | 28.3<br>27.2 |      | °C/W<br>°C/W |  |

| θ <sub>JA</sub> @3M/S                                          |     | 21.2         |      | 0/11         |  |

| • Junction-to-Case ( $\theta_{Jc}$ via simulation)             |     |              |      |              |  |

| - Per JESD 51-12 standard at 25°C                              |     | 18.9         |      | °C/W         |  |

| θ <sub>JC</sub>                                                |     | 10.5         |      | 0/11         |  |

| • Junction-to-Board ( $\theta_{JB}$ via simulation)            |     |              |      |              |  |

| - Per JESD 51-2 standard at 25°C                               |     | 25.4         |      | °C/W         |  |

| $\Theta_{\sf JB}$                                              |     | 20.4         |      | 0/11         |  |

| BU-648X3H/i8 Direct &Transformer Coupled<br>Dual-Tap Versions  |     |              |      |              |  |

| • Junction-to-Ambient ( $\theta_{JA}$ via simulation)          |     |              |      |              |  |

| - Per JESD 51-2 standard at 25°C                               |     | 07.0         |      | 0000         |  |

| $\theta_{_{JA}}$ in Still Air                                  |     | 37.8         |      | °C/W         |  |

| - Per JESD 51-6 standard at 25°C                               |     | 31.4         |      | °C/W         |  |

| θ <sub>JA</sub> @1M/S<br>θ_ @2M/S                              |     | 29.8         |      | °C/W         |  |

| θ <sub>JA</sub> @2M/S<br>θ <sub>JA</sub> @3M/S                 |     | 29.0         |      | °C/W         |  |

| • Junction-to-Case ( $\theta_{jc}$ via simulation)             |     |              |      |              |  |

| - Per JESD 51-12 standard at 25°C                              |     |              |      |              |  |

| $\theta_{\sf JC}$                                              |     | 26.2         |      | °C/W         |  |

| • Junction-to-Board ( $\theta_{_{JB}}$ via simulation)         |     |              |      |              |  |

| - Per JESD 51-2 standard at 25°C                               |     |              |      |              |  |

| $\theta_{\sf JB}$                                              |     | 26.5         |      | °C/W         |  |

| ALL PACKAGES                                                   |     |              |      |              |  |

| Operating Case Temperature                                     |     |              |      |              |  |

| - EXX                                                          | -40 |              | +100 | °C           |  |

| - 1XX (Note 15)                                                | -55 |              | +125 | °C           |  |

| Operating Junction Temperature                                 |     |              |      |              |  |

| - Transceiver                                                  | -55 |              | +150 | °C           |  |

| - Protocol                                                     | -55 |              | +135 | °C           |  |

| - Memory                                                       | -55 |              | +140 | °C           |  |

| Storage Temperature                                            | -65 |              | +150 | °C           |  |

| SOLDERING/MOUNTING                                             |     |              |      |              |  |

| 312-BALL BGA PACKAGE                                           |     |              |      |              |  |

| Maximum Peak Body Temperature                                  |     |              | 260  | °C           |  |

| The reflow profile detailed in IPC/JEDEC                       |     |              |      |              |  |

| J-STD-020 is applicable for both leaded and lead-free products |     |              |      |              |  |

| (Refer to DDC's Application Note #A/N-49 "BGA User's           |     |              |      |              |  |

| Guide" for additional important mounting information.)         |     |              |      |              |  |

| Table 1. BU-64843T Specification Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                |       |                 |      |       |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-------|-----------------|------|-------|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PARAMETER                                      | MIN   | ТҮР             | MAX  | UNITS |  |

| PHYSICAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CHARACTERISTICS                                |       |                 |      |       |  |

| Package Bo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | dy Size                                        |       |                 |      |       |  |

| 312-ball BA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                |       |                 |      |       |  |

| • BU-6484                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 43T(U)8                                        | 1.1   | 00 x 0.600 x 0  | .185 | in.   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                | (2    | 27.9 x 15.2 x 4 | .7)  | (mm)  |  |

| • BU-648                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <3H(i)8                                        | 1.1   | 00 x 0.700 x 0  | .185 | in.   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                | (2    | 27.9 x 17.8 x 4 | .7)  | (mm)  |  |

| Total-ACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                |       |                 |      |       |  |

| <ul> <li>Moisture</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | e Sensitivity Level                            |       | MSL-3           |      |       |  |

| <ul> <li>Electros</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | tatic Discharge Sensitivity                    |       | ESD Class 0     |      |       |  |

| Weight                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                |       |                 |      |       |  |

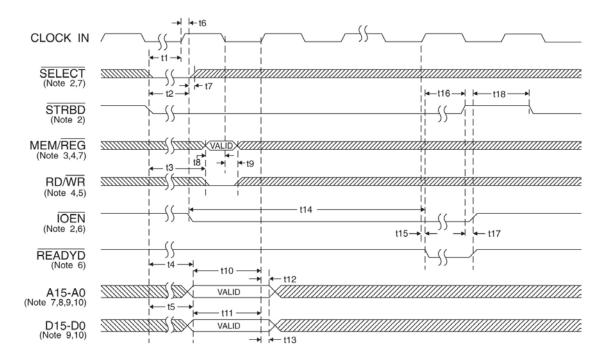

| 312-ball BG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | A                                              | 0.167 |                 |      | oz.   |  |