# Enhanced Miniature Advanced Communications Engine User's Guide

Model: BU-6186X

### Volume 2 - Hardware Reference

DDC's Enhanced Mini-ACE family of MIL-STD-1553 terminals provide complete interfaces between a host processor and 1553 bus. These terminals integrate a dual transceiver, protocol logic, and 4K or 64K words of RAM.

#### Enhanced Mini-ACE Family:

- Enhanced Mini-ACE^{\tiny (B)}

- Micro-ACE<sup>®</sup>

- Mini-ACE<sup>®</sup> Mark3

- Micro-ACE<sup>®</sup>-TE

- Total-ACE®

For more information: www.ddc-web.com/EMA

# DDC's Data Networking Solutions

# MIL-STD-1553 | ARINC 429 | Fibre Channel

As the leading global supplier of data bus components, cards, and software solutions for the military, commercial, and aerospace markets, DDC's data bus networking solutions encompass the full range of data interface protocols from MIL-STD-1553 and ARINC 429 to USB, and Fibre Channel, for applications utilizing a spectrum of form-factors including PMC, PCI, Compact PCI, PC/104, ISA, and VME/VXI.

DDC has developed its line of high-speed Fibre Channel and Extended 1553 products to support the real-time processing of field-critical data networking netween sensors, compute notes, data storage displays, and weapons for air, sea, and ground military vehicles.

Whether employed in increased bandwidth, high-speed serial communications, or traditional avionics and ground support applications, DDC's data solutions fufill the expanse of military requirements including reliability, determinism, low CPU utilization, real-time performance, and ruggedness within harsh environments. Out use of in-house intellectual property ensures superior multi-generational support, independent of the life cycles of commercial devices. Moreover, we maintain software compatibility between product generations to protect our customers' investments in software development, system testing, and end-product qualification.

#### \_ MIL-STD-1553 \_

DDC provides an assortment of quality MIL-STD-1553 commercial, military, and COTS grade cards and components to meet your data conversion and data interface needs. DDC supplies MIL-STD-1553 board level products in a variety of form factors including AMC, USB, PCI, cPCI, PCI-104, PCMCIA, PMC, PC/104, PC/104-Plus, VME/VXI, and ISAbus cards. Our 1553 data bus board solutions are integral elements of military, aerospace, and industrial applications. Our extensive line of military and space grade components provide MIL-STD-1553 interface solutions for microprocessors, PCI buses, and simple systems. Our 1553 data bus solutions are designed into a global network of aircraft, helicopter, and missle programs.

#### \_ ARINC 429

DDC also has a wide assortment of quality ARINC-429 commercial, military, and COTS grade cards and components, which will meet your data conversion and data interface needs. DDC supplies ARINC-429 board level products in a variety of form factors including AMC, USB, PCI, PMC, PCI-104, PC/104 Plus, and PCMCIA boards. DDC's ARINC 429 components ensure the accurate and reliable transfer of flight-critical data. Our 429 interfaces support data bus development, validation, and the transfer of flight-critical data aboard commercial aerospace platforms.

#### \_ Fibre Channel \_

DDC has developed its line of high-speed Fibre Channel network access controllers and switches to support the real-time processing demands of field-critical data networking between sensors, computer nodes, data storage, displays, and weapons, for air, sea, and ground military vehicles. Fibre Channel's architecture is optimized to meet the performance, reliability, and demanding environmental requirements of embedded, real time, military applications, and designed to endure the multi-decade life cycle demands of military/aerospace programs.

## ENHANCED MINIATURE ADVANCED COMMUNICATIONS ENGINE (ENHANCED MINI-ACE<sup>®</sup> SERIES) USER'S GUIDE VOLUME 2 – HARDWARE REFERENCE

# MN-6186X-002

The information provided in this Hardware Manual is belived to be accurate; however, no responsibility is assumed by Data Device Corporation for its use, and no license or rights are granted by implication or otherwise connection therewith.

Specifications are subject to change without notice. Please visit our Web site at <u>http://www.ddc-web.com/</u> for the latest information.

All rights reserved. No part of this Hardware Manual may be reproduced or transmitted in any form or by any mean, electronic, mechanical photocopying recording, or otherwise, without the prior written permission of Data Device Corporation.

> 105 Wilbur Place Bohemia, New York 11716-2426 Tel: (631) 567-5600, Fax: (631) 567-7358 World Wide Web - <u>http://www.ddc-web.com</u>

For Technical Support - 1-800-DDC-5757 ext. 7771 United Kingdom - Tel: +44-(0)1635-811140, Fax: +44-(0)1635-32264 France - Tel: +33-(0)1-41-16-3424, Fax: +33-(0)1-41-16-3425 Germany Tel: +49-(0)89-15 00 12-11, Fax: +49-(0)89-15 00 12-22 Japan - Tel: +81-(0)3-3814-7688, Fax: +81-(0)3-3814-7689 Asia - Tel: +65-6489-4801

© 2000, 2005 Data Device Corp.

| Revision | Date    | Pages                                  | Description                                                                                                                                                                                                              |

|----------|---------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| А        | 3/2003  | All                                    | Reformatted                                                                                                                                                                                                              |

| В        | 8/2004  | All                                    | Major Revision, See MarCom for Markup                                                                                                                                                                                    |

| A        | 8/2005  | All                                    | Major Revision, Volume 2 now a stand alone Manual returning to an A revision.                                                                                                                                            |

| В        | 1/2007  | All                                    | Updated Figures 12, 41, and 42<br>Updated Tables 17 & 18<br>Volume 3 (Appendices) added to Volume 2, with<br>Appendix E intentionally left blank                                                                         |

| С        | 6/2007  | All                                    | Updated Tables 20, 21, 32 and 33<br>Moved footnote referencing Table 22 and Figure 46<br>under Fig 46 to Fig 45 referencing Tables 20 and 21<br>and Figures 45 and 46.<br>Removed Southeast and West coast contact info. |

| D        | 11/2007 | 54                                     | T12 description corrected.                                                                                                                                                                                               |

| E        | 2/2008  | 156 – 182                              | Removed outline drawings, pinouts, and ordering information, as these details are maintained in the datasheet.                                                                                                           |

| F        | 12/2008 | Various                                | Addition of the AceXtreme product line.                                                                                                                                                                                  |

| G        | 7/2011  | 4, 13, 15, 19, 21,<br>22, 23, 154, 160 | Figure 2 title change, text edits on pages 13, 19 and 21, added Figure 6, updated Figures 4, 9 and 10, updated Tables 41 and 42                                                                                          |

| н        | 8/2012  | All                                    | Updated all images to a clearer format, new template applied to document.                                                                                                                                                |

| J        | 7/2016  | 31,32,34                               | Updated section 9.2 and figure 15.                                                                                                                                                                                       |

|          |         |                                        |                                                                                                                                                                                                                          |

|          |         |                                        |                                                                                                                                                                                                                          |

|          |         |                                        |                                                                                                                                                                                                                          |

|          |         |                                        |                                                                                                                                                                                                                          |

|          |         |                                        |                                                                                                                                                                                                                          |

| 1.1                                                                                                                           | REFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

|                                                                                                                               | Text Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                                       |

| 1.2                                                                                                                           | Special Handling and Cautions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                                       |

| 1.3                                                                                                                           | Trademarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                         |

| 1.4                                                                                                                           | What is included in this manual?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                                                                                       |

| 1.5                                                                                                                           | Technical Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2                                                                                       |

| 2 0                                                                                                                           | VERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3                                                                                       |

| ~ <b>-</b>                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -                                                                                       |

| 3 D                                                                                                                           | EVICE SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | /                                                                                       |

| 4 F                                                                                                                           | UNCTIONAL OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8                                                                                       |

|                                                                                                                               | Transceivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                         |

|                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                         |

| 5 S                                                                                                                           | IGNAL DESCRIPTIONS BY FUNCTIONAL GROUPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 11                                                                                      |

| 6 +                                                                                                                           | 5.0V TRANSCEIVER INTERFACE TO A MIL-STD-1553 BUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12                                                                                      |

| 6.1                                                                                                                           | +5.0 Volt Isolation Transformers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 14                                                                                      |

| -                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 45                                                                                      |

| <b>7 +</b>                                                                                                                    | 3.3V TRANSCEIVER INTERFACE TO A MIL-STD-1553 BUS<br>+3.3 Volt Isolation Transformers                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                         |

| 1.1                                                                                                                           | +3.3 Volt Isolation Transformers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 18                                                                                      |

| 8 T                                                                                                                           | HERMAL MANAGEMENT FOR MICRO-ACE AND MIRCO-ACE-TE (BGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                         |

| PAC                                                                                                                           | (AGE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 19                                                                                      |

| 8.1                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                         |

| 0.1                                                                                                                           | Power Supply and PC Board Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 21                                                                                      |

| 8.2                                                                                                                           | Power Supply and PC Board Considerations<br>Simplified Equivalent Circuit of Transceiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                         |

| -                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 26                                                                                      |

| 8.2                                                                                                                           | Simplified Equivalent Circuit of Transceiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 26<br>27                                                                                |

| 8.2<br>8.3                                                                                                                    | Simplified Equivalent Circuit of Transceiver<br>Isolation Transformer Interface to System Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 26<br>27<br>27                                                                          |

| 8.2<br>8.3<br>8.4<br>8.5                                                                                                      | Simplified Equivalent Circuit of Transceiver<br>Isolation Transformer Interface to System Connector<br>Simulated Bus (Lab Bench) Interconnections<br>Logic Compatibility                                                                                                                                                                                                                                                                                                                                                                                          | 26<br>27<br>27<br>30                                                                    |

| 8.2<br>8.3<br>8.4<br>8.5<br><b>9 H</b>                                                                                        | Simplified Equivalent Circuit of Transceiver<br>Isolation Transformer Interface to System Connector<br>Simulated Bus (Lab Bench) Interconnections<br>Logic Compatibility                                                                                                                                                                                                                                                                                                                                                                                          | 26<br>27<br>27<br>30<br><b>31</b>                                                       |

| 8.2<br>8.3<br>8.4<br>8.5<br><b>9 H</b><br>9.1                                                                                 | Simplified Equivalent Circuit of Transceiver<br>Isolation Transformer Interface to System Connector<br>Simulated Bus (Lab Bench) Interconnections<br>Logic Compatibility<br>OST PROCESSOR AND MEMORY INTERFACE<br>Address Mapping: Words vs. Bytes                                                                                                                                                                                                                                                                                                                | 26<br>27<br>27<br>30<br><b>31</b><br>31                                                 |

| 8.2<br>8.3<br>8.4<br>8.5<br><b>9 H</b><br>9.1<br>9.2                                                                          | Simplified Equivalent Circuit of Transceiver<br>Isolation Transformer Interface to System Connector<br>Simulated Bus (Lab Bench) Interconnections<br>Logic Compatibility<br>OST PROCESSOR AND MEMORY INTERFACE<br>Address Mapping: Words vs. Bytes<br>16-Bit Buffered Mode                                                                                                                                                                                                                                                                                        | 26<br>27<br>30<br><b>31</b><br>31                                                       |

| 8.2<br>8.3<br>8.4<br>8.5<br><b>9 H</b><br>9.1<br>9.2<br>9.3                                                                   | Simplified Equivalent Circuit of Transceiver<br>Isolation Transformer Interface to System Connector<br>Simulated Bus (Lab Bench) Interconnections<br>Logic Compatibility<br>OST PROCESSOR AND MEMORY INTERFACE<br>Address Mapping: Words vs. Bytes<br>16-Bit Buffered Mode<br>Zero Wait Configuration                                                                                                                                                                                                                                                             | 26<br>27<br>30<br><b>31</b><br>31<br>31                                                 |

| 8.2<br>8.3<br>8.4<br>8.5<br><b>9 H</b><br>9.1<br>9.2<br>9.3<br>9.4                                                            | Simplified Equivalent Circuit of Transceiver<br>Isolation Transformer Interface to System Connector<br>Simulated Bus (Lab Bench) Interconnections<br>Logic Compatibility<br>OST PROCESSOR AND MEMORY INTERFACE<br>Address Mapping: Words vs. Bytes<br>16-Bit Buffered Mode<br>Zero Wait Configuration<br>16-Bit Transparent Mode                                                                                                                                                                                                                                  | 26<br>27<br>30<br><b>31</b><br>31<br>31<br>33<br>35                                     |

| 8.2<br>8.3<br>8.4<br>8.5<br><b>9 H</b><br>9.1<br>9.2<br>9.3<br>9.4<br>9.5                                                     | Simplified Equivalent Circuit of Transceiver<br>Isolation Transformer Interface to System Connector<br>Simulated Bus (Lab Bench) Interconnections<br>Logic Compatibility<br><b>IOST PROCESSOR AND MEMORY INTERFACE.</b><br>Address Mapping: Words vs. Bytes<br>16-Bit Buffered Mode<br>Zero Wait Configuration<br>16-Bit Transparent Mode<br>16-Bit Dual Port RAM Interface                                                                                                                                                                                       | 26<br>27<br>30<br><b>31</b><br>31<br>31<br>33<br>35<br>38                               |

| 8.2<br>8.3<br>8.4<br>8.5<br><b>9 H</b><br>9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6                                              | Simplified Equivalent Circuit of Transceiver<br>Isolation Transformer Interface to System Connector<br>Simulated Bus (Lab Bench) Interconnections<br>Logic Compatibility<br>OST PROCESSOR AND MEMORY INTERFACE<br>Address Mapping: Words vs. Bytes<br>16-Bit Buffered Mode<br>Zero Wait Configuration<br>16-Bit Transparent Mode<br>16-Bit Dual Port RAM Interface<br>16-Bit DMA Mode                                                                                                                                                                             | 26<br>27<br>30<br><b>31</b><br>31<br>33<br>35<br>38<br>40                               |

| 8.2<br>8.3<br>8.4<br>8.5<br><b>9 H</b><br>9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7                                       | Simplified Equivalent Circuit of Transceiver<br>Isolation Transformer Interface to System Connector<br>Simulated Bus (Lab Bench) Interconnections<br>Logic Compatibility<br><b>OST PROCESSOR AND MEMORY INTERFACE.</b><br>Address Mapping: Words vs. Bytes<br>16-Bit Buffered Mode<br>Zero Wait Configuration<br>16-Bit Transparent Mode<br>16-Bit Dual Port RAM Interface<br>16-Bit DMA Mode<br>Handshake Timeout                                                                                                                                                | 26<br>27<br>30<br><b>31</b><br>31<br>33<br>35<br>38<br>40<br>41                         |

| 8.2<br>8.3<br>8.4<br>8.5<br><b>9 H</b><br>9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8                                | Simplified Equivalent Circuit of Transceiver<br>Isolation Transformer Interface to System Connector<br>Simulated Bus (Lab Bench) Interconnections<br>Logic Compatibility<br><b>IOST PROCESSOR AND MEMORY INTERFACE.</b><br>Address Mapping: Words vs. Bytes<br>16-Bit Buffered Mode<br>Zero Wait Configuration<br>16-Bit Transparent Mode<br>16-Bit Dual Port RAM Interface<br>16-Bit DMA Mode<br>Handshake Timeout<br>8-Bit Buffered Mode                                                                                                                        | 26<br>27<br>30<br>31<br>31<br>33<br>35<br>38<br>38<br>40<br>41<br>45                    |

| 8.2<br>8.3<br>8.4<br>8.5<br><b>9 H</b><br>9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8<br>9.9                         | Simplified Equivalent Circuit of Transceiver.<br>Isolation Transformer Interface to System Connector.<br>Simulated Bus (Lab Bench) Interconnections.<br>Logic Compatibility.<br><b>OST PROCESSOR AND MEMORY INTERFACE.</b><br>Address Mapping: Words vs. Bytes.<br>16-Bit Buffered Mode .<br>Zero Wait Configuration .<br>16-Bit Transparent Mode<br>16-Bit Dual Port RAM Interface .<br>16-Bit DMA Mode .<br>Handshake Timeout                                                                                                                                   | 26<br>27<br>30<br>31<br>31<br>31<br>33<br>35<br>38<br>40<br>41<br>45<br>49              |

| 8.2<br>8.3<br>8.4<br>8.5<br><b>9 H</b><br>9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8<br>9.9<br>9.10                 | Simplified Equivalent Circuit of Transceiver.<br>Isolation Transformer Interface to System Connector.<br>Simulated Bus (Lab Bench) Interconnections.<br>Logic Compatibility.<br><b>OST PROCESSOR AND MEMORY INTERFACE.</b><br>Address Mapping: Words vs. Bytes.<br>16-Bit Buffered Mode.<br>Zero Wait Configuration<br>16-Bit Transparent Mode.<br>16-Bit Dual Port RAM Interface<br>16-Bit DUal Port RAM Interface.<br>16-Bit DMA Mode.<br>Handshake Timeout.<br>8-Bit Buffered Mode<br>8-Bit Zero Wait Mode<br>Control Logic.                                   | 26<br>27<br>30<br>31<br>31<br>33<br>35<br>38<br>35<br>38<br>40<br>41<br>45<br>49<br>52  |

| 8.2<br>8.3<br>8.4<br>8.5<br><b>9 H</b><br>9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8<br>9.9<br>9.10<br>9.11         | Simplified Equivalent Circuit of Transceiver.<br>Isolation Transformer Interface to System Connector.<br>Simulated Bus (Lab Bench) Interconnections.<br>Logic Compatibility.<br><b>OST PROCESSOR AND MEMORY INTERFACE.</b><br>Address Mapping: Words vs. Bytes.<br>16-Bit Buffered Mode .<br>Zero Wait Configuration .<br>16-Bit Transparent Mode.<br>16-Bit Dual Port RAM Interface .<br>16-Bit DUAl Port RAM Interface .<br>16-Bit DMA Mode .<br>Handshake Timeout .<br>8-Bit Buffered Mode .<br>8-Bit Zero Wait Mode .<br>Control Logic .<br>Interrupt Logic . | 26<br>27<br>30<br>31<br>31<br>33<br>35<br>38<br>40<br>41<br>45<br>49<br>52              |

| 8.2<br>8.3<br>8.4<br>8.5<br><b>9 H</b><br>9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8<br>9.9<br>9.10<br>9.11<br>9.12 | Simplified Equivalent Circuit of Transceiver.<br>Isolation Transformer Interface to System Connector.<br>Simulated Bus (Lab Bench) Interconnections.<br>Logic Compatibility.<br><b>OST PROCESSOR AND MEMORY INTERFACE.</b><br>Address Mapping: Words vs. Bytes.<br>16-Bit Buffered Mode.<br>Zero Wait Configuration<br>16-Bit Transparent Mode.<br>16-Bit Dual Port RAM Interface<br>16-Bit DUal Port RAM Interface.<br>16-Bit DMA Mode.<br>Handshake Timeout.<br>8-Bit Buffered Mode<br>8-Bit Zero Wait Mode<br>Control Logic.                                   | 26<br>27<br>30<br><b>31</b><br>31<br>33<br>35<br>38<br>40<br>41<br>45<br>49<br>52<br>52 |

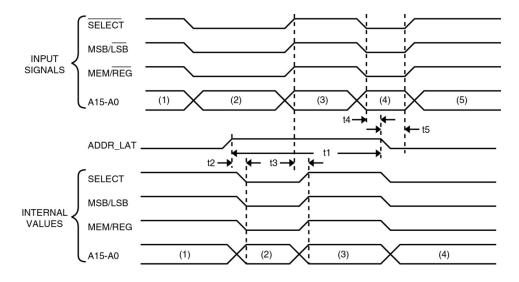

| 9.15 Address Latch Timing                                                                                                                                                                                                                             |                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| 9.16 Clock Input Considerations                                                                                                                                                                                                                       |                                                                     |

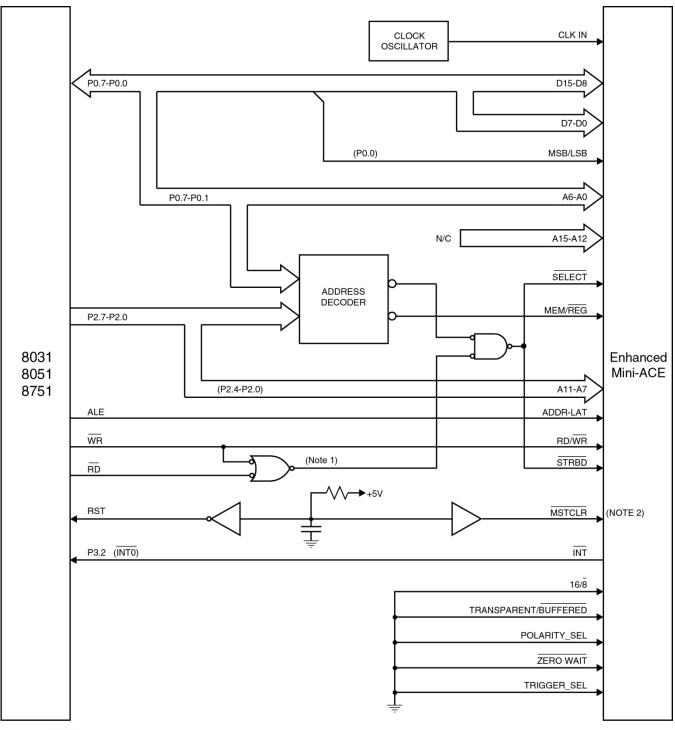

| 9.17 Sample Interfaces                                                                                                                                                                                                                                |                                                                     |

|                                                                                                                                                                                                                                                       |                                                                     |

| 10 DETAILED DESCRIPTION OF 1553 MESSAGE SEQUEI                                                                                                                                                                                                        |                                                                     |

| 10.1 General RAM Transfer Timing                                                                                                                                                                                                                      |                                                                     |

| 10.2 Single Word Read and Write Cycles                                                                                                                                                                                                                |                                                                     |

| 10.3 SOM/EOM Burst Read/Write Timing                                                                                                                                                                                                                  |                                                                     |

| 10.4 BC Operation                                                                                                                                                                                                                                     |                                                                     |

| 10.5 RT Operation                                                                                                                                                                                                                                     |                                                                     |

| 10.6 Message MT Operation                                                                                                                                                                                                                             | 141                                                                 |

| 10.7 Word MT Operation                                                                                                                                                                                                                                | 151                                                                 |

|                                                                                                                                                                                                                                                       | 450                                                                 |

| 11 APPENDIX A: ISOLATION TRANSFORMERS                                                                                                                                                                                                                 |                                                                     |

| 11.1 ISOLATION TRANSFORMERS FOR USE WITH DDC +5.0 TERMINALS                                                                                                                                                                                           |                                                                     |

|                                                                                                                                                                                                                                                       |                                                                     |

|                                                                                                                                                                                                                                                       |                                                                     |

| 11.2 ISOLATION TRANSFORMERS FOR USE WITH DDC +3.3                                                                                                                                                                                                     | VOLT MIL-STD-1553                                                   |

|                                                                                                                                                                                                                                                       | VOLT MIL-STD-1553                                                   |

| 11.2 ISOLATION TRANSFORMERS FOR USE WITH DDC +3.3                                                                                                                                                                                                     | VOLT MIL-STD-1553<br>159                                            |

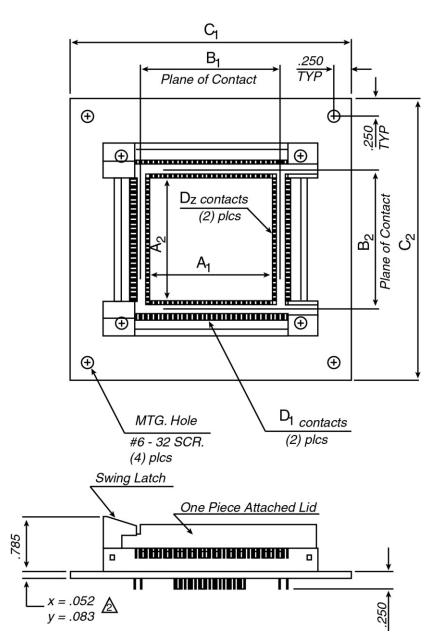

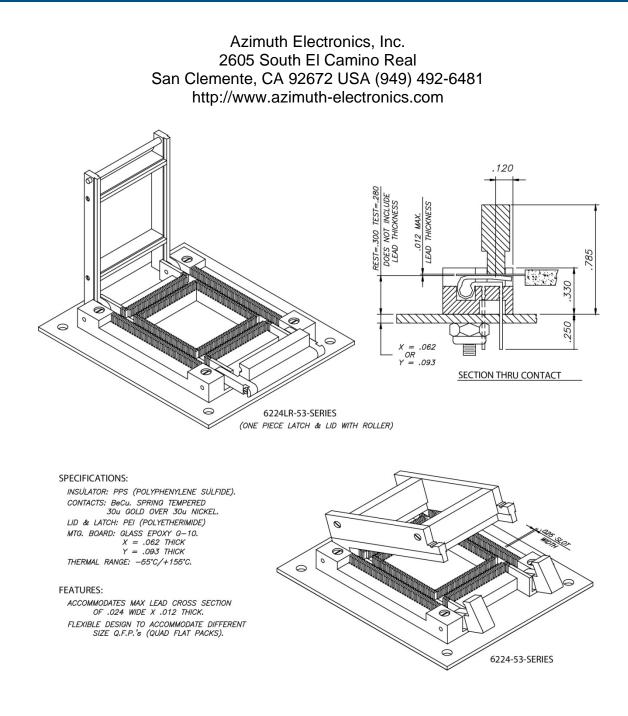

| <ul> <li>11.2 ISOLATION TRANSFORMERS FOR USE WITH DDC +3.3 TERMINALS</li> <li>12 APPENDIX B: BREADBOARDING SOCKETS</li> </ul>                                                                                                                         | VOLT MIL-STD-1553<br>159<br><b>162</b>                              |

| 11.2 ISOLATION TRANSFORMERS FOR USE WITH DDC +3.3<br>TERMINALS                                                                                                                                                                                        | VOLT MIL-STD-1553<br>159<br><b>162</b>                              |

| <ul> <li>11.2 ISOLATION TRANSFORMERS FOR USE WITH DDC +3.3 TERMINALS</li> <li>12 APPENDIX B: BREADBOARDING SOCKETS</li> <li>13 APPENDIX C: DESC DRAWING PART NUMBERS</li> </ul>                                                                       | VOLT MIL-STD-1553<br>159<br><b>162</b><br><b>164</b>                |

| <ul> <li>11.2 ISOLATION TRANSFORMERS FOR USE WITH DDC +3.3 TERMINALS</li> <li>12 APPENDIX B: BREADBOARDING SOCKETS</li> <li>13 APPENDIX C: DESC DRAWING PART NUMBERS</li> <li>14 APPENDIX D : ISSUE INVOLVING USE OF EXECUTE A</li> </ul>             | VOLT MIL-STD-1553<br>159<br>162<br>                                 |

| <ul> <li>11.2 ISOLATION TRANSFORMERS FOR USE WITH DDC +3.3 TERMINALS</li> <li>12 APPENDIX B: BREADBOARDING SOCKETS</li> <li>13 APPENDIX C: DESC DRAWING PART NUMBERS</li> </ul>                                                                       | VOLT MIL-STD-1553<br>159<br>162<br>                                 |

| <ul> <li>11.2 ISOLATION TRANSFORMERS FOR USE WITH DDC +3.3 TERMINALS</li> <li>12 APPENDIX B: BREADBOARDING SOCKETS</li> <li>13 APPENDIX C: DESC DRAWING PART NUMBERS</li> <li>14 APPENDIX D : ISSUE INVOLVING USE OF EXECUTE A</li> </ul>             | VOLT MIL-STD-1553<br>159<br>162<br>164<br>.ND FLIP "XGF " BC<br>168 |

| <ul> <li>11.2 ISOLATION TRANSFORMERS FOR USE WITH DDC +3.3 TERMINALS.</li> <li>12 APPENDIX B: BREADBOARDING SOCKETS</li> <li>13 APPENDIX C: DESC DRAWING PART NUMBERS</li> <li>14 APPENDIX D : ISSUE INVOLVING USE OF EXECUTE A INSTRUCTION</li></ul> | VOLT MIL-STD-1553<br>                                               |

| <ul> <li>11.2 ISOLATION TRANSFORMERS FOR USE WITH DDC +3.3 TERMINALS.</li> <li>12 APPENDIX B: BREADBOARDING SOCKETS</li> <li>13 APPENDIX C: DESC DRAWING PART NUMBERS</li> <li>14 APPENDIX D : ISSUE INVOLVING USE OF EXECUTE A INSTRUCTION</li></ul> | VOLT MIL-STD-1553<br>                                               |

| <ul> <li>11.2 ISOLATION TRANSFORMERS FOR USE WITH DDC +3.3 TERMINALS.</li> <li>12 APPENDIX B: BREADBOARDING SOCKETS</li> <li>13 APPENDIX C: DESC DRAWING PART NUMBERS</li> <li>14 APPENDIX D : ISSUE INVOLVING USE OF EXECUTE A INSTRUCTION</li></ul> | VOLT MIL-STD-1553<br>                                               |

| Figure 1. Enhanced Mini-ACE/Micro-ACE Series Block Diagram              |                        |

|-------------------------------------------------------------------------|------------------------|

| Figure 2. Mini-ACE Mark3 and Micro-ACE-TE Block Diagram                 | 5                      |

| Figure 3. Total-ACE Block Diagram                                       | 6                      |

| Figure 4. Enhanced Mini-ACE Series Interface to 1553 Bus (+5.0V Trans   | sceivers [X3/4] & MIL- |

| STD-1553 Trim shown)                                                    |                        |

| Figure 5. Enhanced Mini-ACE Series Interface to 1553 Bus (+3.3V Trans   | sceivers [X8/9] & MIL- |

| STD-1553 Trim shown)                                                    |                        |

| Figure 6. Enhanced Mini-ACE Series Interface to 1553 Bus (+3.3V Trans   | sceivers [XC/D] &      |

| MIL-STD-1553 Trim shown)                                                |                        |

| Figure 7. Total-ACE Series Interface to 1553 Bus (+3.3V Transceivers [2 | (8] & MIL-STD-1553     |

| Trim shown)                                                             |                        |

| Figure 8. Ball Locations for Micro-ACE-TE and Micro-ACE (BGA Package    | jes)20                 |

| Figure 9. Ball Locations for Total-ACE (BGA Package)                    |                        |

| Figure 10. P.C. Board Layout Example: X3/4/C/D Transceiver              |                        |

| Figure 11. P.C. Board Layout Example: X8/9 Transceiver                  |                        |

| Figure 12. Power/Ground Current Distribution for +5V Transceivers (X3/  | 4 Option)26            |

| Figure 13. Simplified Equivalent Circuit of Enhanced Mini-ACE Terminal  | 26                     |

| Figure 14. Simulated Bus Interconnections                               |                        |

| Figure 15. Interconnection Diagram for 16-Bit Buffered Mode             |                        |

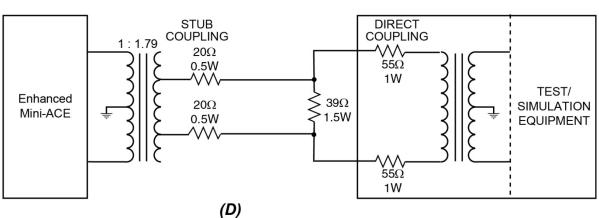

| Figure 16. Interconnection Diagram for 16-Bit Transparent Mode          |                        |

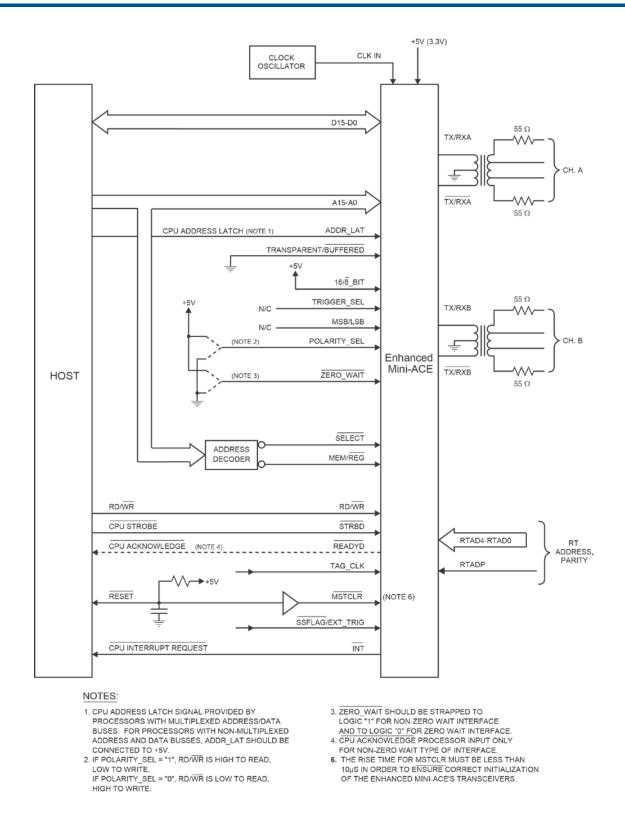

| Figure 17. Interconnection Diagram for 16-Bit Dual Port RAM Mode        |                        |

| Figure 18. Interconnection Diagram for 16-Bit DMA Mode                  |                        |

| Figure 19. 16-Bit DMA with External Logic to Reduce CPU Access Time     | 44                     |

| Figure 20. Interconnection Diagram for 8-Bit Buffered Mode              |                        |

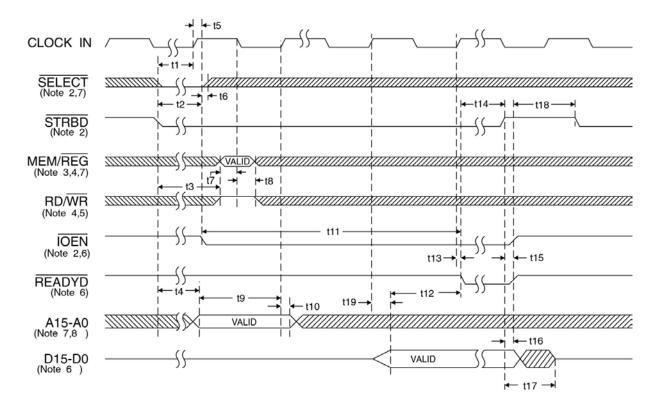

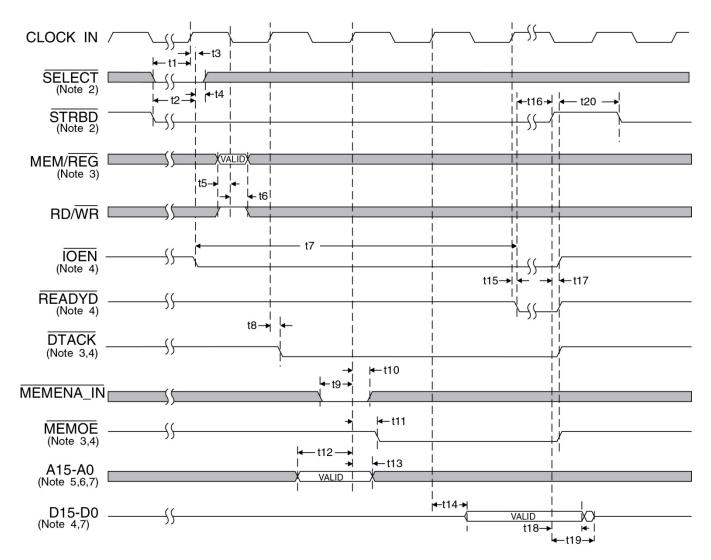

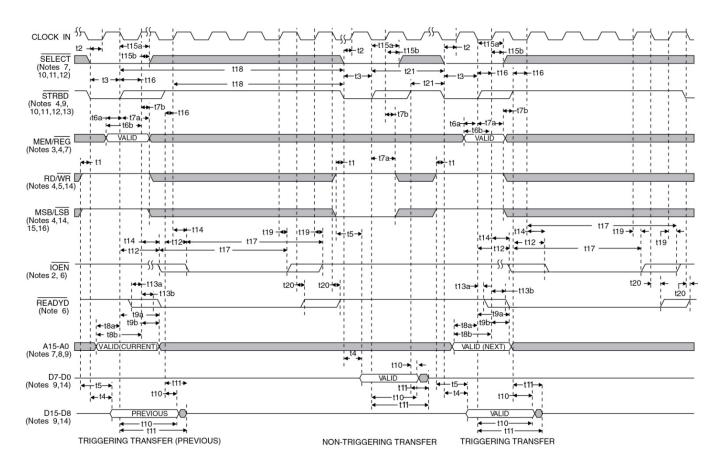

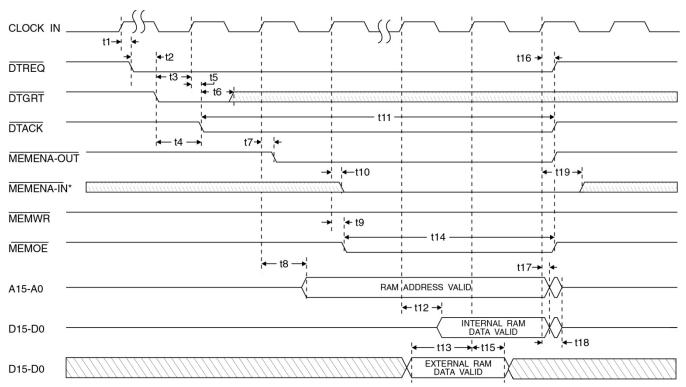

| Figure 21. CPU Reading RAM/Registers (16-Bit, Buffered, Nonzero Wai     | t)56                   |

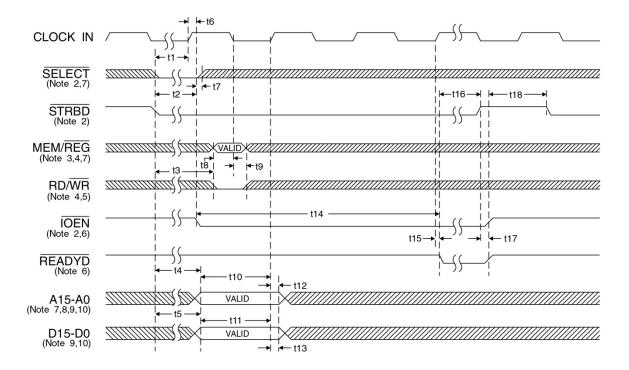

| Figure 22. CPU Writing RAM/Registers (16-Bit, Buffered, Nonzero Wait)   | 60                     |

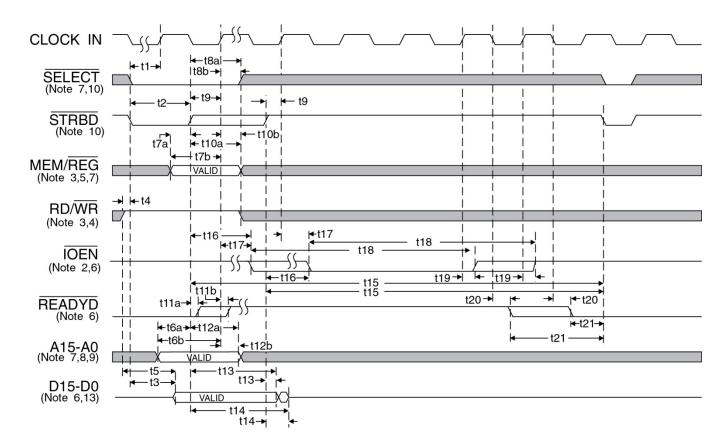

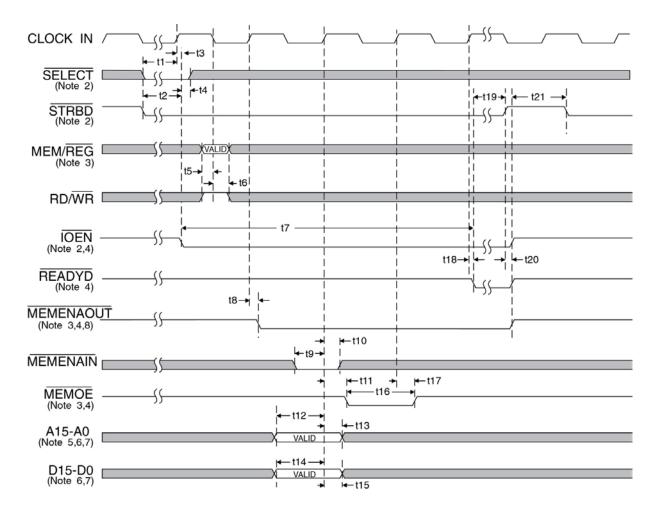

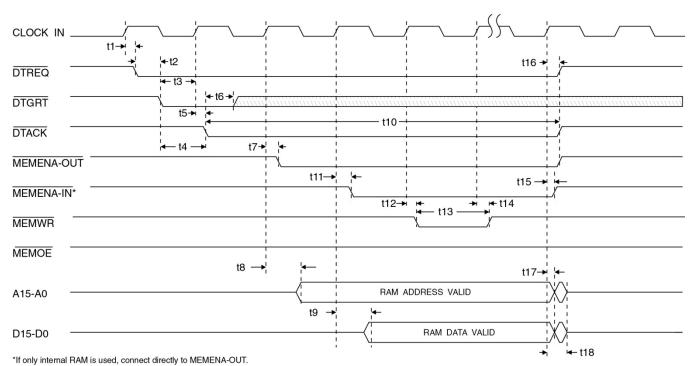

| Figure 23. CPU Reading RAM/Registers (16-Bit, Buffered, Zero Wait)      | 64                     |

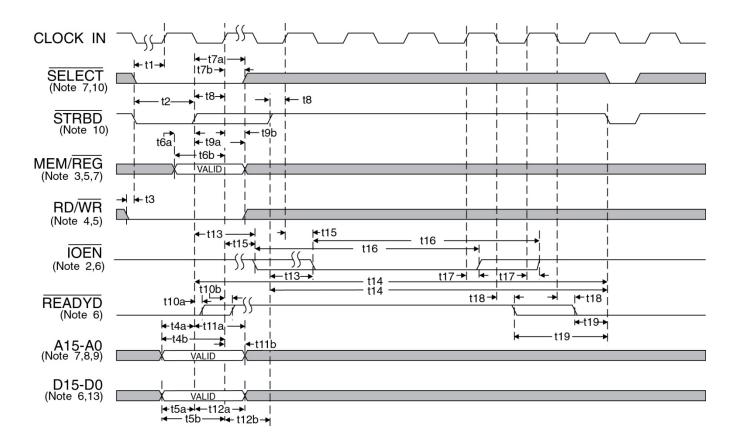

| Figure 24. CPU Writing RAM/Registers (16-Bit, Buffered, Zero Wait)      |                        |

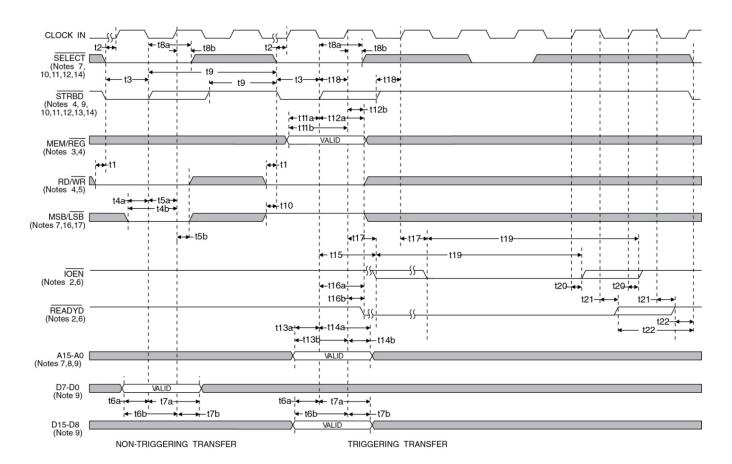

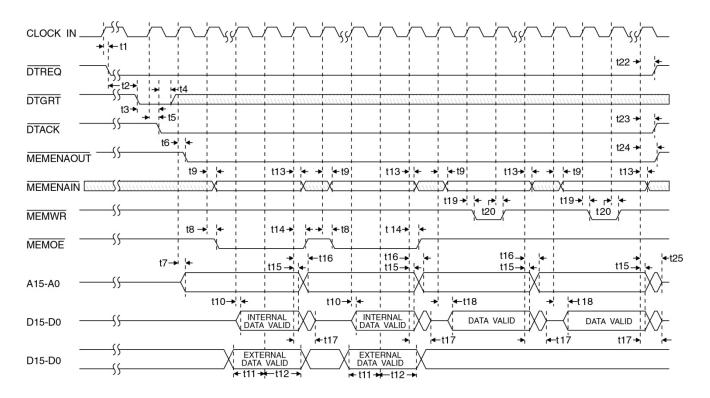

| Figure 25. CPU Reading RAM/Registers (Transparent Mode)                 |                        |

| Figure 26. CPU Writing RAM/Registers (Transparent Mode)                 | 75                     |

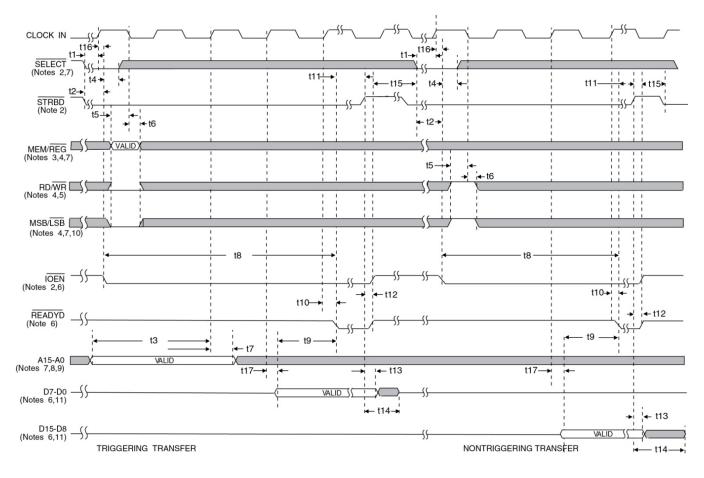

| Figure 27. CPU Reading RAM/Registers (8-Bit, Nonzero Wait)              |                        |

| Figure 28. CPU Writing RAM/Registers (8-Bit, Nonzero Wait)              |                        |

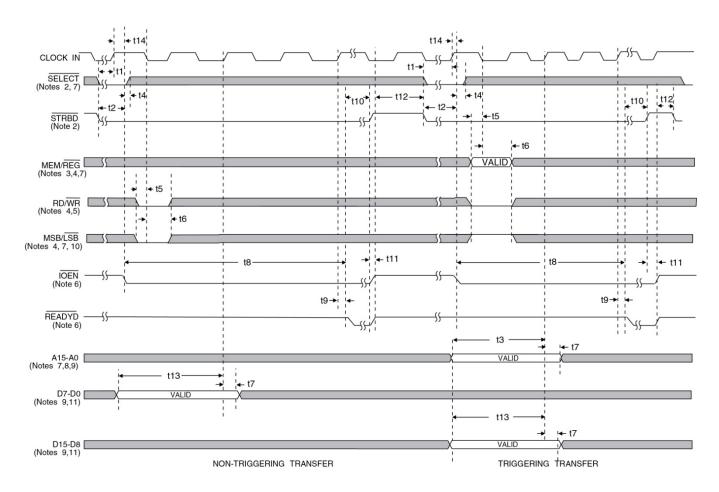

| Figure 29. CPU Reading RAM/Registers (8-Bit, Zero Wait)                 |                        |

| Figure 30. CPU Writing RAM/Registers (8-Bit, Zero Wait)                 |                        |

| Figure 31. Address Latch Timing                                         |                        |

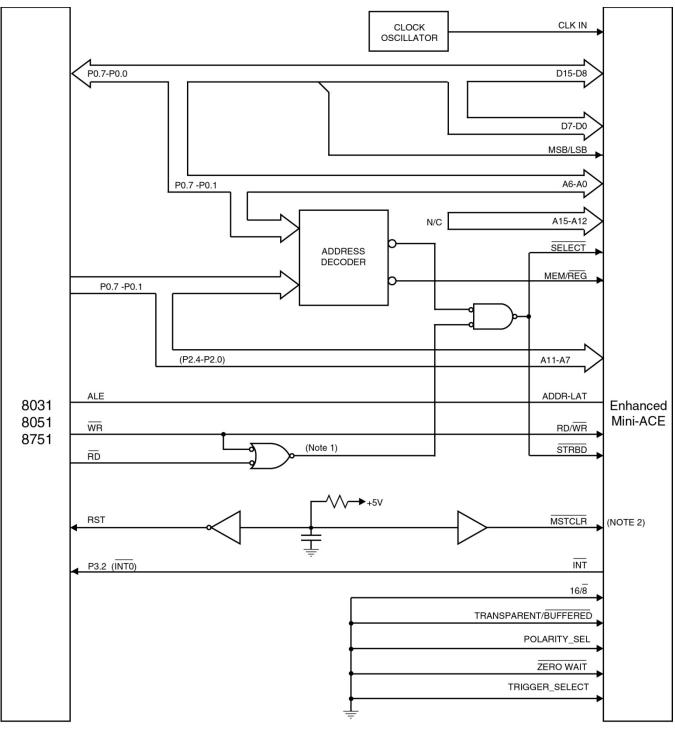

| Figure 32. Intel 8051-to-Enhanced Mini-ACE Interface                    |                        |

| Figure 33. ADSP-2101-to- ACE Interface                                  |                        |

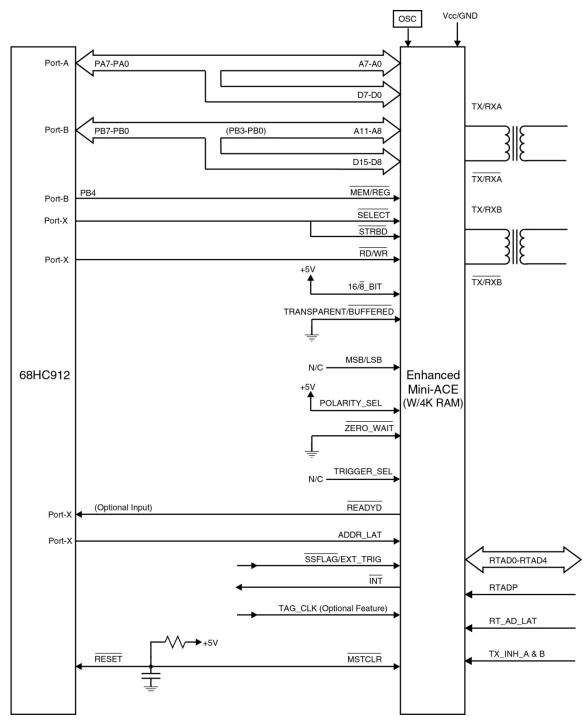

| Figure 34. Motorola 68HC912-to-Enhanced Mini-ACE Interface              |                        |

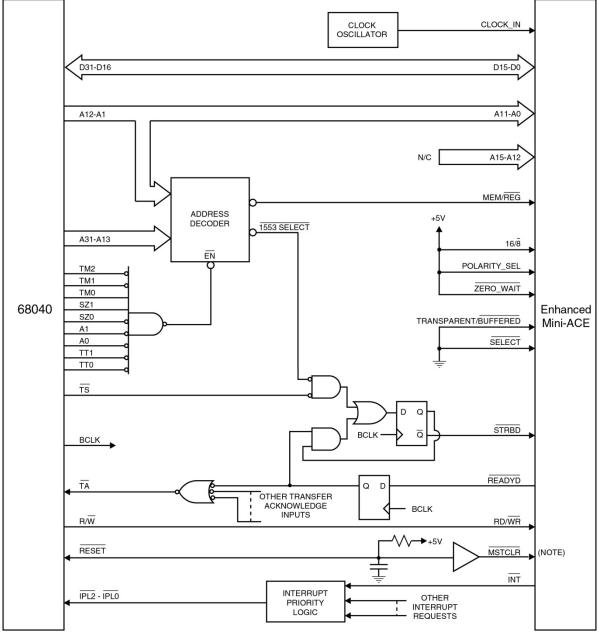

| Figure 35. Motorola 68040-to-Enhanced Mini-ACE Interface                |                        |

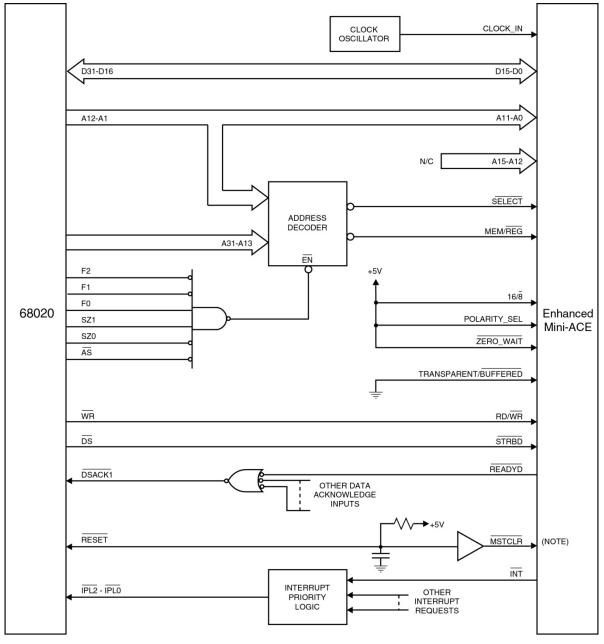

| Figure 36. Motorola 68020-to-Enhanced Mini-ACE Interface                |                        |

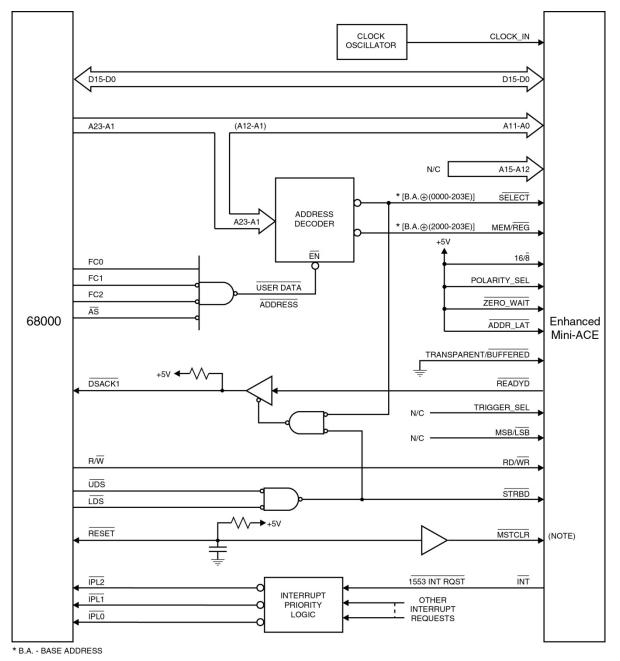

| Figure 37. Motorola 68000-to-Enhanced Mini-ACE Interface                |                        |

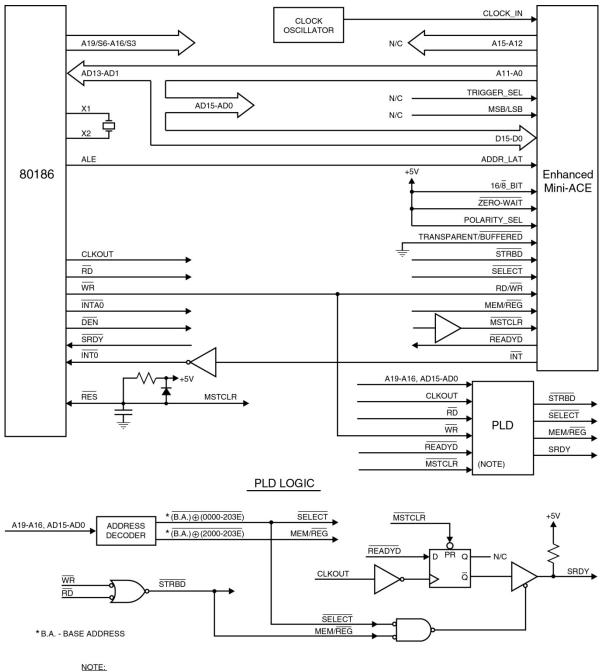

| Figure 38. INTEL 80186-to-Enhanced Mini-ACE Interface                   |                        |

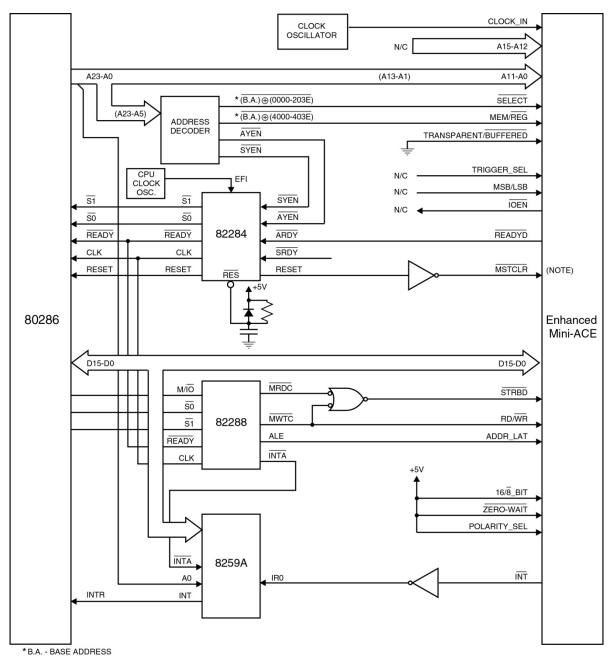

| Figure 39. INTEL 80286-to-Enhanced Mini-ACE Interface                   |                        |

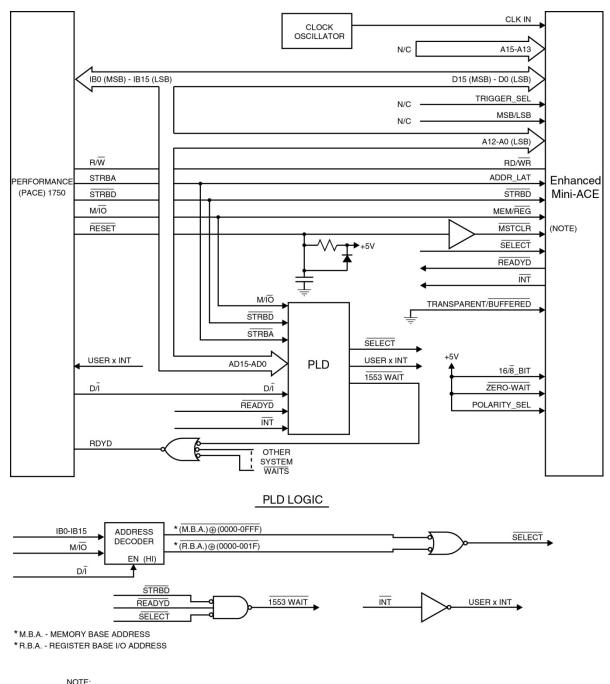

| Figure 40. Performance (PACE) 1750-to-Enhanced Mini-ACE Interface .     |                        |

|                                                                         |                        |

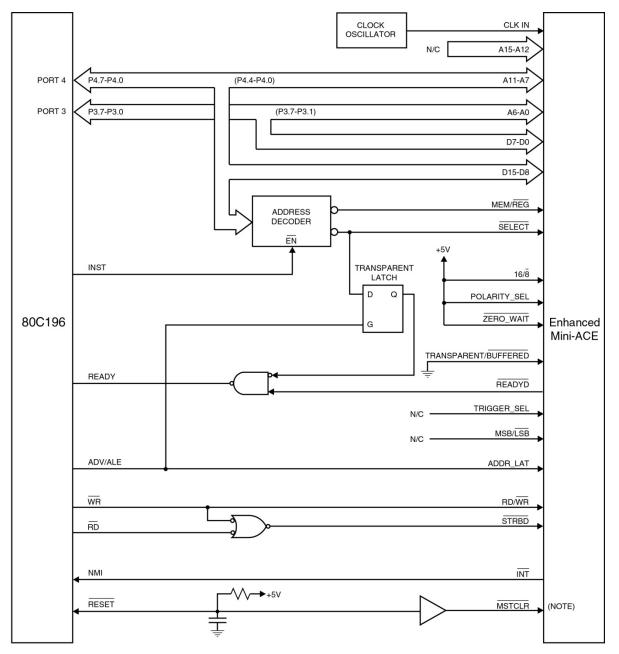

| Figure 41. INTEL 80C196-to-Enhanced Mini-ACE Interface                | 103 |

|-----------------------------------------------------------------------|-----|

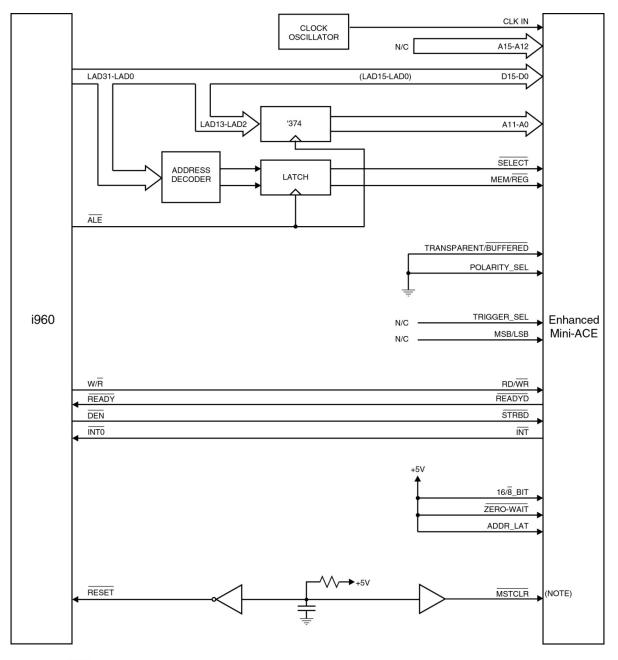

| Figure 42. INTEL i960-to-Enhanced Mini-ACE Interface                  | 104 |

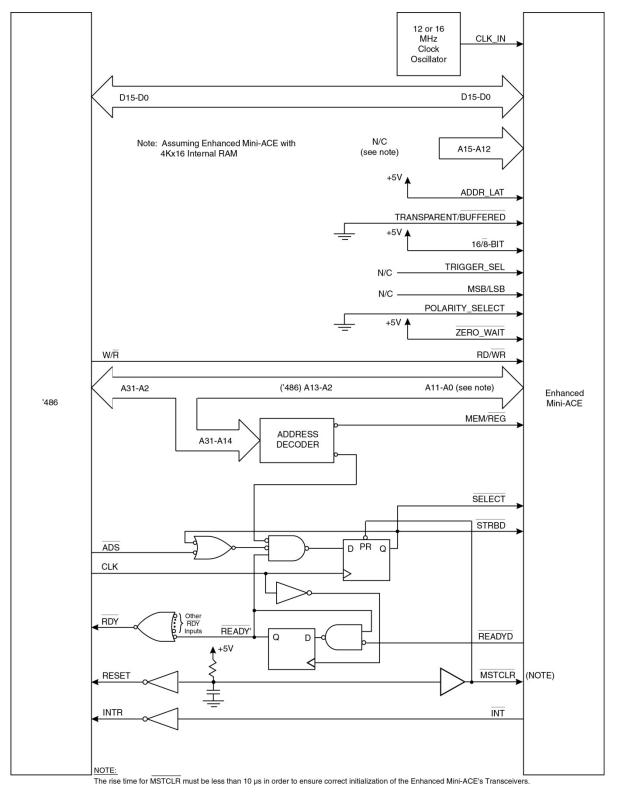

| Figure 43. INTEL 80486-to-Enhanced Mini-ACE Interface                 | 105 |

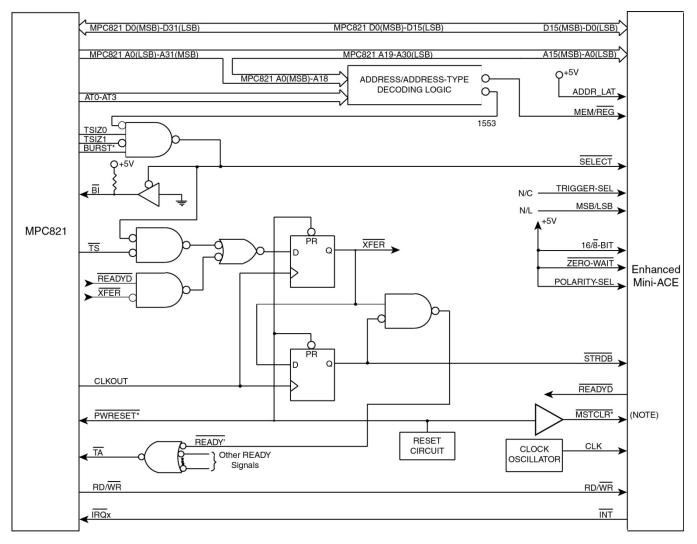

| Figure 44. Motorola MPC821-to-Enhanced Mini-ACE Interface             | 106 |

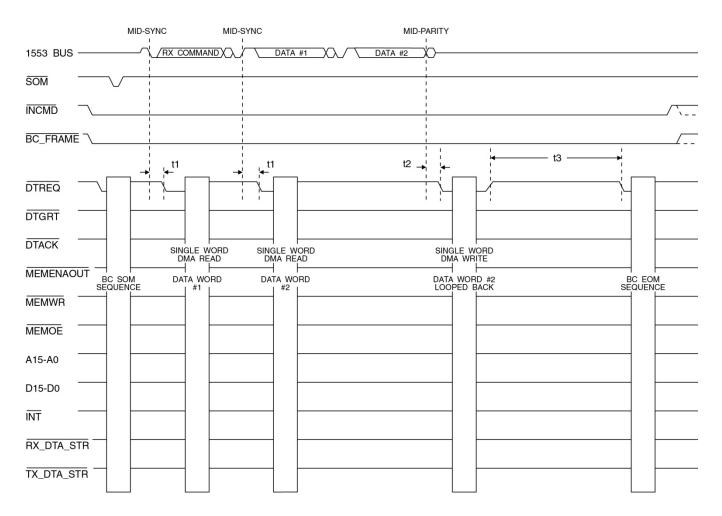

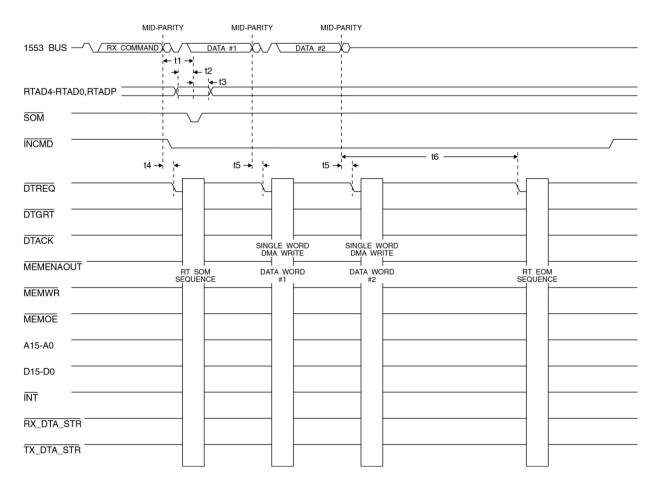

| Figure 45. Enhanced Mini-ACE Single Word DMA Read (Transparent Mode)  | 110 |

| Figure 46. Enhanced Mini-ACE Single Word DMA Write (Transparent Mode) | 113 |

| Figure 47. BC/RT/MT SOM/EOM Burst Read/Write Timing                   | 115 |

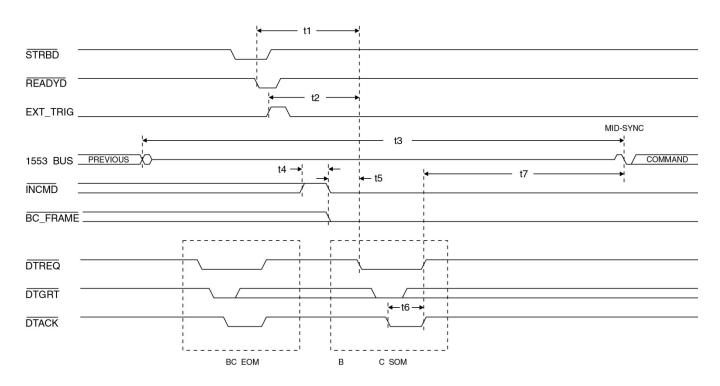

| Figure 48. BC Mode Receive Message Timing Sequence                    | 118 |

| Figure 49. BC Mode Transmit Message Timing Sequence                   | 120 |

| Figure 50. BC Mode Broadcast Message Timing Sequence                  | 122 |

| Figure 51. BC Mode Start Timing                                       | 124 |

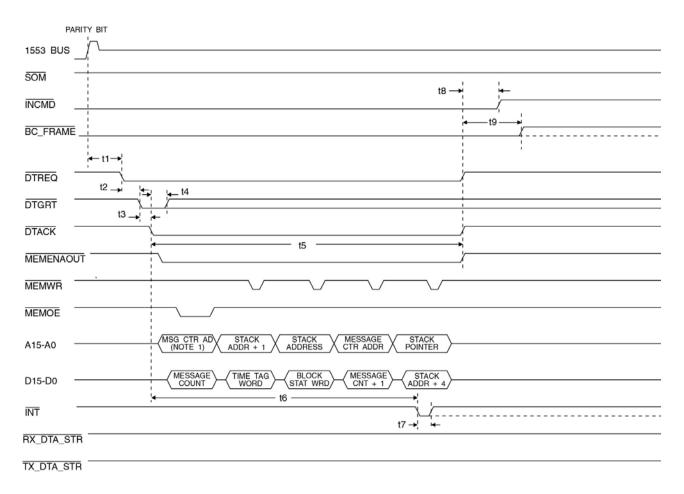

| Figure 52. BC Start of Message (SOM) Sequence Timing                  | 126 |

| Figure 53. BC End of Message (EOM) Sequence Timing                    | 128 |

| Figure 54. BC Retry Timing                                            |     |

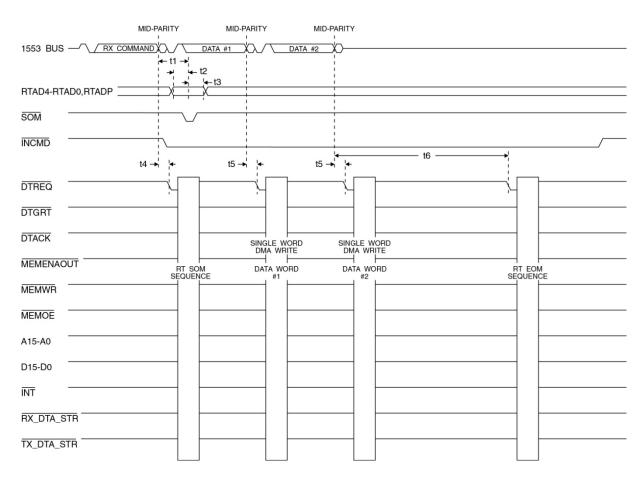

| Figure 55. RT Receive Message Timing                                  | 133 |

| Figure 56. RT Transmit Message Timing                                 | 135 |

| Figure 57. RT Broadcast Receive Message Timing                        | 136 |

| Figure 58. RT Start of Message (SOM) Timing                           | 138 |

| Figure 59. RT End of Message (EOM) Timing                             |     |

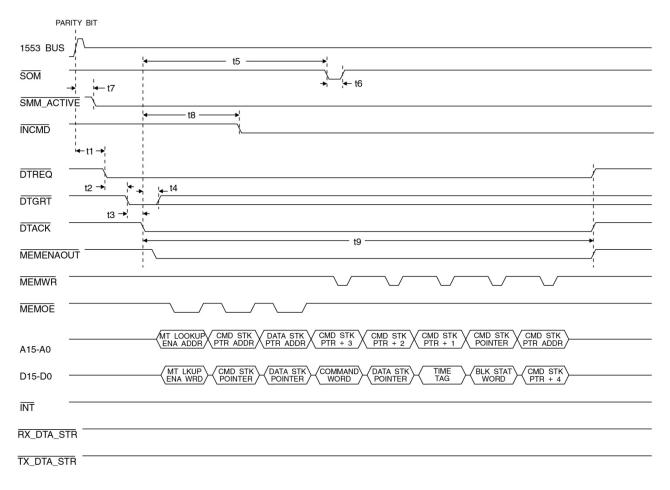

| Figure 60. Message MT Receive Message Timing                          | 142 |

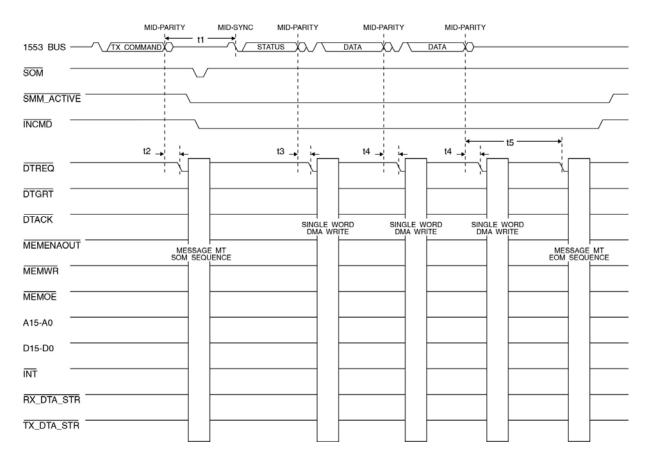

| Figure 61. Message MT Transmit Message Timing                         | 143 |

| Figure 62. Message MT Broadcast Receive Message Timing                |     |

| Figure 63. Message MT Command Not Selected Timing                     |     |

| Figure 64. Message MT Start of Message (SOM) Timing                   |     |

| Figure 65. Message MT End of Message (EOM) Timing                     |     |

| Figure 66. Word MT Start Timing                                       |     |

| Figure 67. Word MT Received Word Write Cycle Timing                   | 155 |

| Table 1.  | Operation Of Address and Data Buffers For 16-Bit Interfaces      | 35  |

|-----------|------------------------------------------------------------------|-----|

| Table 2.  | Summary of 8-Bit Operation (Nonzero Wait Mode)                   | 48  |

| Table 3.  | Minimum Required Delay Times                                     | 50  |

| Table 4.  | Summary of 8-Bit Operation (Zero Wait Mode)                      | 51  |

| Table 5.  | CPU Reading RAM/Registers (16-Bit, Buffered, Non-Zero Wait Mode) | 54  |

| Table 6.  | CPU Writing RAM/Registers (16-Bit, Buffered, Nonzero Wait Mode)  | 58  |

| Table 7.  | CPU Reading RAM/Registers (16-Bit, Buffered, Zero Wait Mode)     | 62  |

| Table 8.  | CPU Writing RAM/Registers (16-Bit, Buffered, Zero Wait Mode)     | 66  |

| Table 9.  | CPU Reading RAM/Registers (Transparent Mode)                     | 70  |

| Table 10. |                                                                  |     |

| Table 11. | CPU Reading RAM/Registers (8-Bit NonZero Wait Mode)              | 77  |

| Table 12. | $\mathbf{U}$                                                     |     |

| Table 13. | CPU Reading RAM/Registers (8-Bit, Zero Wait Mode)                | 83  |

| Table 14. | $\mathbf{U}$                                                     |     |

| Table 15. |                                                                  | 91  |

| Table 16. |                                                                  |     |

| Table 17. | 5 ( 1 )                                                          |     |

| Table 18. | <b>o</b> ( <b>i</b> )                                            |     |

| Table 19. | 6                                                                |     |

| Table 20. | 5 5 1                                                            |     |

| Table 21. |                                                                  |     |

| Table 22. | BC Mode Broadcast Message Timing Sequence                        | 121 |

| Table 23. |                                                                  |     |

| Table 24. |                                                                  |     |

| Table 25. |                                                                  |     |

| Table 26. | , .                                                              |     |

| Table 27. |                                                                  |     |

| Table 28. | 6 6                                                              |     |

| Table 29. | 0 0                                                              |     |

| Table 30. | 0 0                                                              |     |

| Table 31. | 0 0                                                              |     |

| Table 32. | <b>o o o</b>                                                     |     |

| Table 33. | 0 0 0                                                            |     |

| Table 34. | 0 0 0                                                            |     |

| Table 35. | 0                                                                |     |

| Table 36. | 0 0 0                                                            |     |

| Table 37. | 5 5 5                                                            |     |

| Table 38. |                                                                  |     |

| Table 39. |                                                                  | 154 |

| Table 40. |                                                                  |     |

| Table 41. |                                                                  |     |

| Optic     | ons                                                              | 160 |

|           |                                                                  |     |

| Table 42. | Enhanced Mini-ACE B  | U-61743/61745 RT, | and | BU-61843/61845/61864/61865 |    |

|-----------|----------------------|-------------------|-----|----------------------------|----|

| BC/R      | F/MT DESC Drawing Pa | art Numbers       |     | 1                          | 64 |

## 1 PREFACE

This manual uses typographical conventions to assist the reader in understanding the content. This section will define the text formatting used in the rest of the manual

### 1.1 Text Usage

- **BOLD**–indicates important information and table, figure, and chapter references.

- **BOLD ITALIC**-designates DDC Part Numbers.

- Courier New-indicates code examples.

- <...> indicates user-entered text or commands.

### **1.2 Special Handling and Cautions**

The *Enhanced Mini-ACE Series* uses state-of-the-art components, and proper care should be used to ensure that the device will not be damaged by Electrical Static Discharge (ESD), physical shock, or improper power surges and that precautions are taken to avoid electrocution.

Warnings: Turn off power to the computer hardware and unplug from wall.

NEVER insert or remove card with power turned on.

Ensure that standard ESD precautions are followed. As a minimum, one hand should be grounded to the power supply in order to equalize the static potential.

Do not store disks in environments exposed to excessive heat, magnetic fields or radiation.

### 1.3 Trademarks

All trademarks are the property of their respective owners.

### 1.4 What is included in this manual?

This manual contains a complete description of hardware installation and use.

### 1.5 Technical Support

In the event that problems arise beyond the scope of this manual, you can contact DDC by the following:

US Toll Free Technical Support: 1-800-DDC-5757, ext. 7771

Outside of the US Technical Support: 1-631-567-5600, ext. 7771

Fax: 1-631-567-5758 to the attention of DATA BUS Applications

DDC Website: www.ddc-web.com/ContactUs/TechSupport.aspx

Please note that the latest revisions of Software and Documentation are available for download at DDC's Web Site, <u>www.ddc-web.com</u>.

# 2 OVERVIEW

All references throughout this document to the "Enhanced Mini-ACE" shall be interpreted to include Enhanced Mini-ACE, Micro-ACE, Mini-ACE Mark3, Micro-ACE TE, and Total-ACE products. Any specific references to a unique series of components (i.e. Micro-ACE only) will utilize the component part number (i.e. BU-61740B, BU-61840B/61860B etc.).

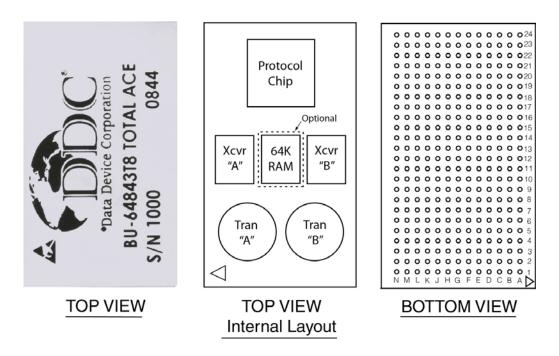

The Enhanced Mini-ACE family (Enhanced Mini-ACE, Micro-ACE, Mini-ACE Mark 3, Micro-ACE TE, Total-ACE) of MIL-STD-1553 terminals provides complete interfaces between a host processor and a 1553 bus. All these terminals integrate dual transceiver, protocol logic, and 4K words or 64K words of RAM. Additionally, the Total-ACE integrates the isolation transformer(s) as well. The BC/RT/MT versions with 64K words of RAM include built-in RAM parity checking.

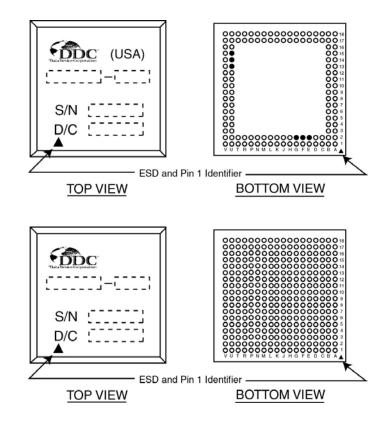

The Enhanced Mini-ACE is packaged in a choice of a 1.0-inch square Flat Pack or Gull Wing package, or a 0.815-inch square BGA package (Micro-ACE). The Mini-ACE Mark 3 is packaged in a choice of a 0.890-inch Flat Pack or Gull Wing package, or a 0.815-inch square BGA package (Micro-ACE-TE). The Total-ACE is packaged in a 1.100-inch x 0.600-inch rectangular, plastic BGA.

The Flat Pack or Gull Wing packaged Enhanced Mini-ACE provides footprint compatibility with the previous generation Mini-ACE (Plus) terminal.

All members of the Enhanced Mini-ACE series (Enhanced Mini-ACE, Micro-ACE, Mini-ACE Mark3, Micro-ACE-TE, and Total-ACE) provide software compatibility with the previous generation Mini-ACE (Plus) terminals, and the older ACE series.

The Enhanced Mini-ACE and Micro-ACE are powered by a choice 5V, or 5V/3.3V (3.3V logic). Multiprotocol support of MIL-STD-1553A/B and STANAG 3838, including versions incorporating McAir compatible transmitters, is provided. There is a choice of 10, 12, 16, or 20 MHz clocks.

The Mini-ACE Mark3 and Micro-ACE-TE are powered by a choice of 3.3V/5V (logic), and 3.3V/5V (transceivers). (Certain combination restrictions apply. See datasheet for full ordering information). Multiprotocol support of MIL-STD-1553A/B and STANAG 3838, including versions incorporating McAir compatible transmitters, is provided. There is a choice of 10, 12, 16, or 20 MHz clocks.

The Total-ACE is an all 3.3V device (logic & transceivers) with integrated isolation transformers. (Certain combination restrictions apply. See datasheet for full ordering information). Multiprotocol support of MIL-STD-1553A/B and STANAG 3838, is provided. There is a choice of 10, 12, 16, or 20 MHz clocks.

BC features include a built-in engine, with a set of 20 instructions. This provides an autonomous means of implementing multi-frame message scheduling, message retry schemes, data double buffering, asynchronous message insertion, and reporting to the host CPU. The Enhanced Mini-ACE incorporates a fully autonomous built-in selftest, which provides comprehensive testing of the internal protocol logic and/or RAM.

The Enhanced Mini-ACE RT offers the same choices of subaddress buffering as ACE and Mini-ACE (Plus), along with a global circular buffering option, 50% rollover interrupt for circular buffers, an interrupt status queue, and an "Auto-boot" option to support MIL-STD-1760.

The Enhanced Mini-ACE terminals provide the same flexibility in host interface configurations as the Mini-ACE (Plus) terminals, and the older ACE series along with a reduction in the host processor's worst-case holdoff time.

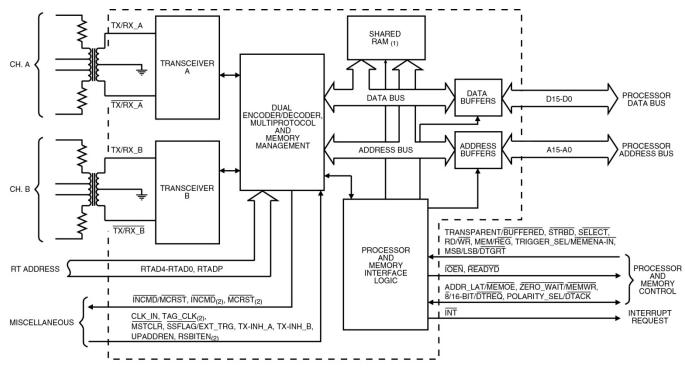

NOTE 1: See Ordering Information for Available Memory Options. NOTE 2: Indicates signals brought out only on µ-ACE (BGA package) version.

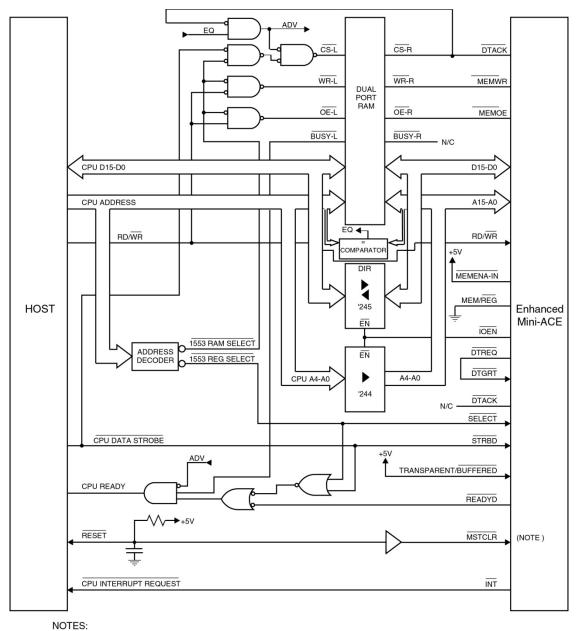

### Figure 1. Enhanced Mini-ACE/Micro-ACE Series Block Diagram

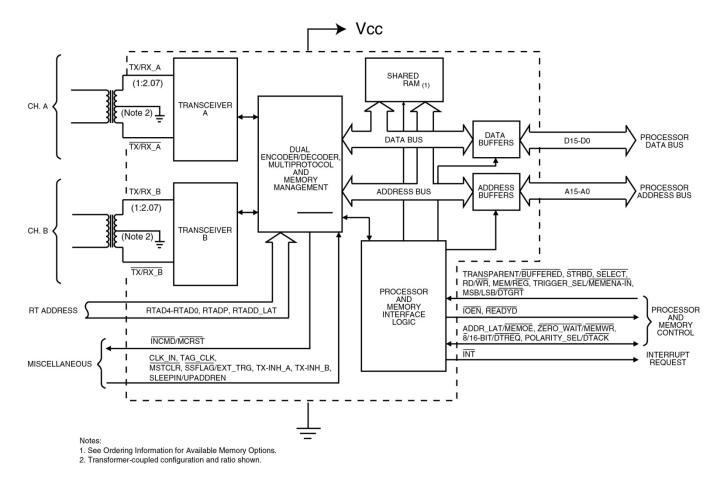

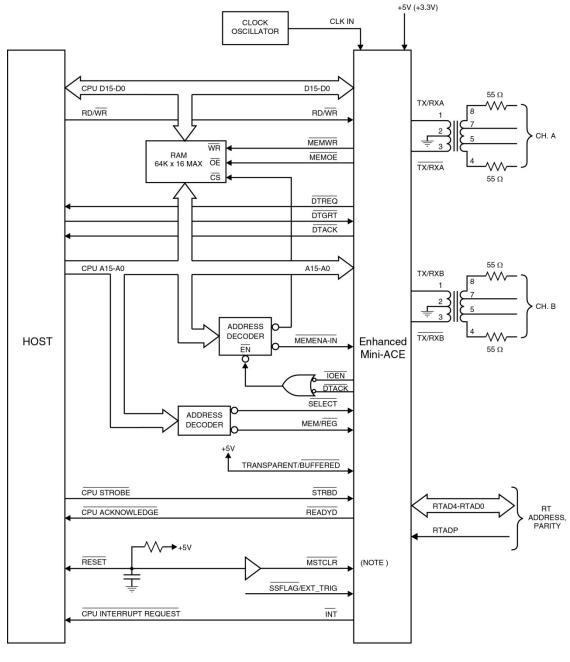

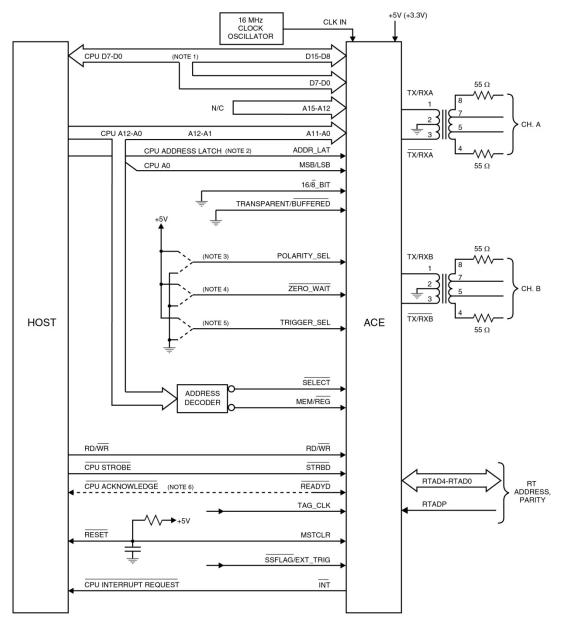

# Figure 2. Mini-ACE Mark3 and Micro-ACE-TE Block Diagram (shown with X8/9 Transceiver Option)

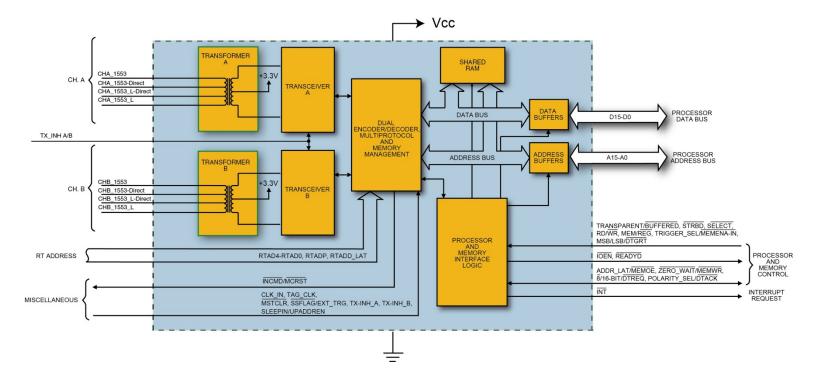

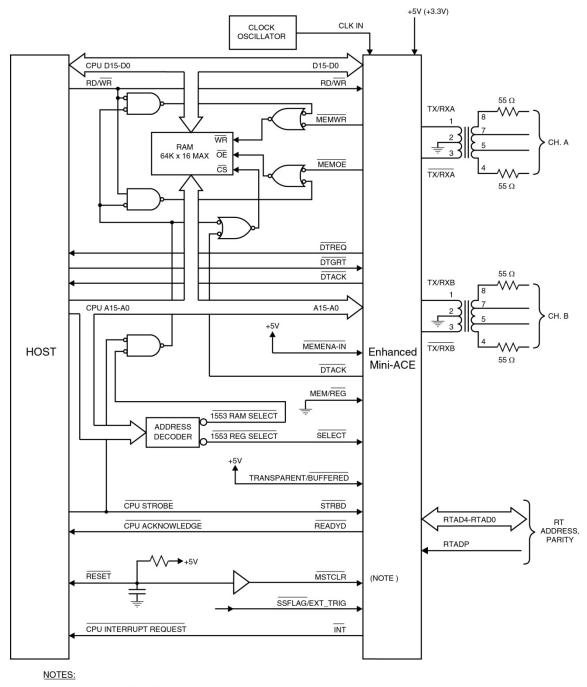

Figure 3. Total-ACE Block Diagram

# **3 DEVICE SPECIFICATIONS**

The Latest Device Specifications for the Enhanced Mini-Ace/Micro-Ace and Mini-ACE Mark3/Micro-ACE TE, and Total-ACE are available at <a href="http://www.ddc-web.com">http://www.ddc-web.com</a>:

For the latest Enhanced Mini-ACE/Micro-ACE information see BU-6174X/6184X/6186X Data Sheet

For the latest Mini-ACE Mark3/Micro-ACE-TE information see BU-6474X/6484X/6486X Data Sheet

For the latest Total-ACE information see BU-64843T Data Sheet

# 4 FUNCTIONAL OVERVIEW

The BU-61743/61745 RT, and BU-61843/61845/61864/61865 BC/RT/MT Enhanced Mini-ACE (BU-61740B RT, and BU-61840B/61860B BC/RT/MT Micro-ACE), BU-64743/64745 RT, and BU-64843/64845/64863 BC/RT/MT Mini-ACE Mark3 (BU-64840B/64843B/64860B/64863B BC/RT/MT Micro-ACE-TE) family of MIL-STD-1553 terminals comprise a complete integrated interface between a host processor and a MIL-STD-1553 bus.

The BU-61743/61745 RT, and BU-61843/61845/61864/61865 BC/RT/MT Enhanced Mini-ACE are packaged in a 1.0 inch square ceramic flat-pack package providing footprint (with four pin differences) compatibility with previous generation Mini-ACE terminals. The BU-64743/64745 RT, and BU-64843/64845/64863 BC/RT/MT Mini-ACE Mark3 are packaged in a 0.890 inch square ceramic flat-pack package.

The BU-61740B RT, and BU-61840B/61860B BC/RT/MT Micro-ACE and BU-64840B/64843B/64860B/64863B BC/RT/MT Micro-ACE-TE are packaged in a 0.815 inch square BGA package.

The Enhanced Mini-ACE series of hybrids provides software compatibility with the previous generation Mini-ACE terminals, as well as software compatibility with the older ACE series.

The Enhanced Mini-ACE RT provides complete multi-protocol support of MIL-STD-1553A/B/McAir and STANAG 3838. All versions integrate dual transceiver; along with protocol, host interface, memory management logic; and a minimum of 4K words of RAM. In addition, the BU-61864/61865/61860B/64863/64860B/64863B BC/RT/MT terminals include 64K words of internal RAM, with built-in parity checking.

The Enhanced Mini-ACE series includes 5V or 3.3V, voltage source transceivers for improved line driving capability, with options for MIL-STD-1760 and McAir compatibility. As a means of reducing power consumption, there are versions for which the logic is powered by 3.3V, rather than 5V. To provide further flexibility, the Enhanced Mini-ACE may operate with a choice of 10, 12, 16, or 20 MHz clock inputs.

One of the salient new features of the Enhanced Mini-ACE is its enhanced bus controller architecture. The Enhanced BC's highly autonomous message sequence control engine provides a means for offloading the host processor for implementing minor and major frame timing control; asynchronous message insertion; data block double buffering; bulk data transfers; and retry and bus switching strategy. For the purpose of performing messaging to the host processor, the Enhanced BC mode includes a General Purpose Queue, along with user-defined interrupts.

The Enhanced Mini-ACE is the latest device group in the ACE family. The term "enhanced" has also been used in earlier versions of the family to describe new features introduced at each stage. For backward compatibility reasons, the same terms and options have been maintained in the Enhanced Mini-ACE. The user will be aware of Enhanced Mode, set by bit 15 of Configuration Register (CR) # 3 along with the following optional features from earlier families:

| Enhanced RT Memory Management     | CR#2 Bit #1  |

|-----------------------------------|--------------|

| Enhanced RT Interrupt Handling    | CR#2 Bit #15 |

| Enhanced Mode Code Handling       | CR#3 Bit #0  |

| Enhanced Mode Enable              | CR#3 Bit #15 |

| Expanded BC Control Word Enable   | CR#4 Bit #12 |

| Plus for the latest devices:      |              |

| Enhanced BC                       | CR#6 Bit #15 |

| Enhanced Time Tag Synchronization | CR#7 Bit #2  |

| Enhanced BC Watchdog Timer Enable | CR#7 Bit #1  |

In many cases, the user may wish to enable most of these bits at initialization to have all available features active

A second major new feature of the Enhanced Mini-ACE is the incorporation of a fully autonomous built-in self-test. This test provides comprehensive testing of the internal protocol logic. A separate test verifies the operation of the internal RAM. Since the self-tests are fully autonomous, they eliminate the need for the host to write and read stimulus and response vectors.

The Enhanced Mini-ACE RT offers the same choices of single, double, and circular buffering for individual subaddresses as the ACE and Mini-ACE (Plus). New enhancements to the RT architecture include a global circular buffering option for multiple (or all) receive subaddresses, a 50% rollover interrupt for circular buffers, an interrupt status queue for logging up to 32 interrupt events, and an option to automatically initialize to RT mode with the busy bit set. The interrupt status queue and 50% rollover interrupt features are also included as improvements to the Enhanced Mini-ACE's monitor architecture.

To minimize board space and "glue" logic, the Enhanced Mini-ACE terminals provide the same wide choice of host interface configurations as the ACE and Mini-ACE (Plus). This includes support of shared RAM interfaces to 16-bit or 8-bit processors, memory or port type interfaces, and multiplexed or non-multiplexed address/data buses; plus a DMA interface configuration.

Hermetic, ceramic packaged, Enhanced Mini-ACE series terminals are available in versions operating over the full military temperature range of -55 to +125°C. Available screened to MIL-PRF-38534C, these terminals are ideal for military and industrial processor-to-1553 applications.

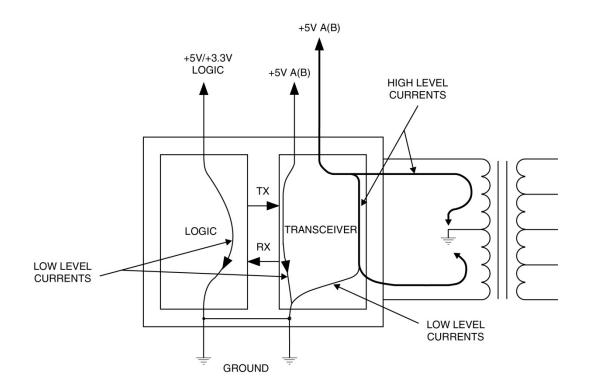

### 4.1 Transceivers

The transceivers in the Enhanced Mini-ACE series of terminals are fully monolithic, requiring only a +5 or +3.3 volt power input. The transmitters are voltage sources, which provide improved line driving capability over current sources. This serves to improve performance on long buses with many taps. The transmitters also offer an option that satisfies the MIL-STD-1760 requirement for a minimum of 20 volts peak-to-peak, transformer coupled output.

Besides eliminating the demand for an additional power supply, the use of a +5V or +3.3V-only transceivers requires the use of a step-up, rather than a step-down, isolation transformer. This provides the advantage of higher terminal input impedance than is possible for a 15 volt or 12 volt transmitter. As a result, there is a greater margin for the input impedance test, mandated for the 1553 validation test. This characteristic allows for longer cable lengths between a system connector and the isolation transformers of an embedded 1553 terminal.

To provide compatibility to McAir specs, the Enhanced Mini-ACE is available with an option for transmitters with increased rise and fall times.

The receiver sections of the Enhanced Mini-ACE are fully compliant with MIL-STD-1553B Notice 2 in terms of front end over voltage protection, threshold, common mode rejection, and word error rate.

## **5 SIGNAL DESCRIPTIONS BY FUNCTIONAL GROUPS**

For the latest Enhanced Mini-ACE/Micro-ACE information see BU-6174X/6184X/6186X Data Sheet

For the latest Mini-ACE Mark3/Micro-ACE-TE information see BU-6474X/6484X/6486X Data Sheet

For the latest Total-ACE information see BU-64843T Data Sheet

# 6 +5.0V TRANSCEIVER INTERFACE TO A MIL-STD-1553 BUS

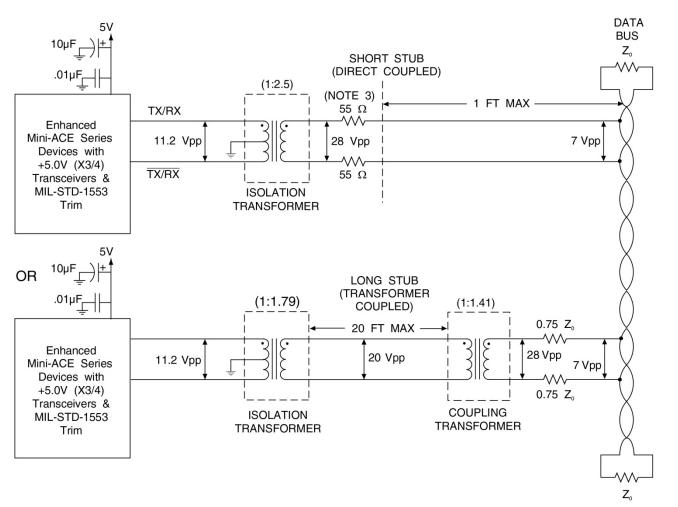

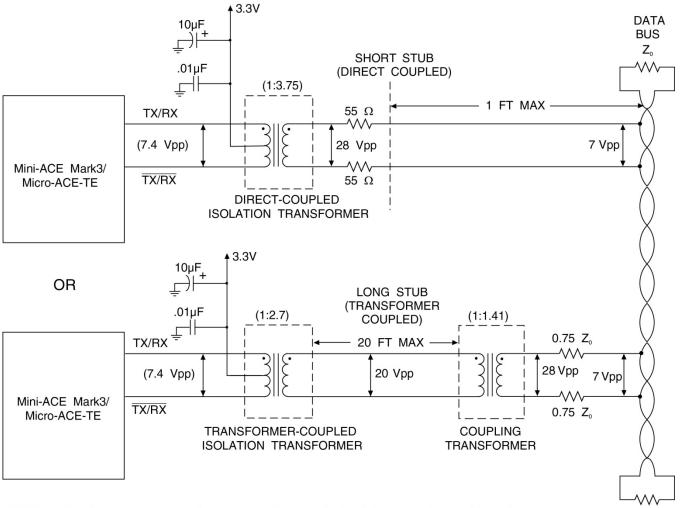

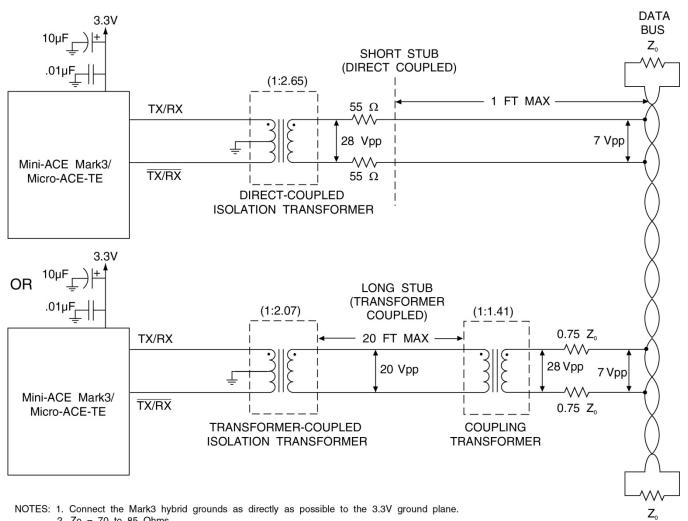

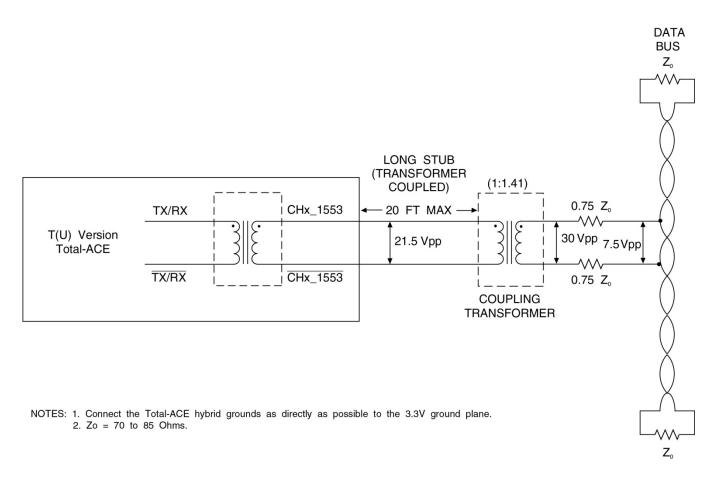

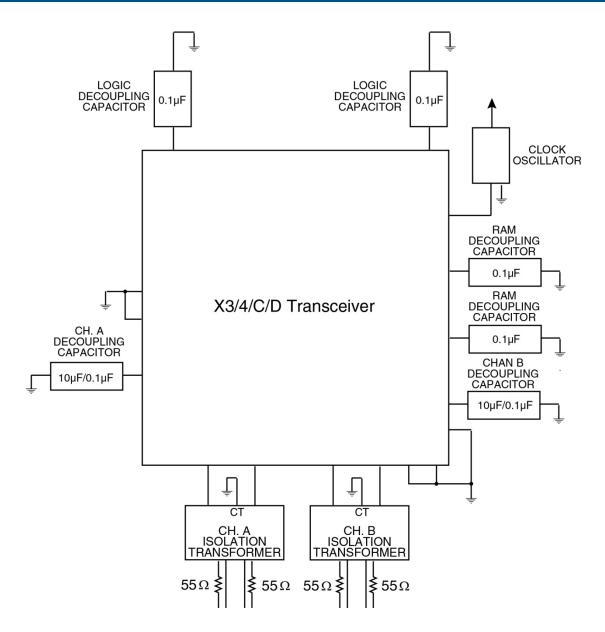

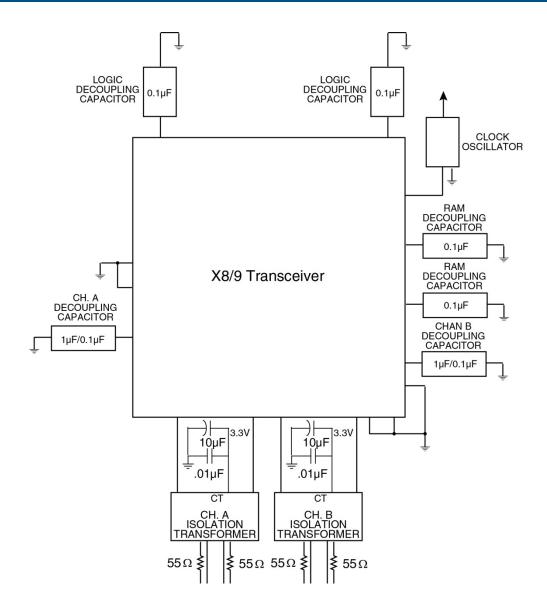

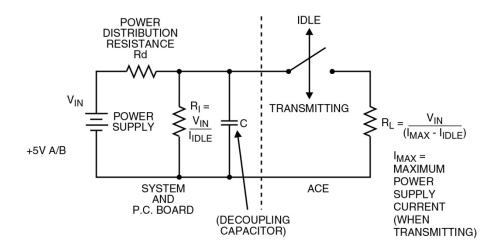

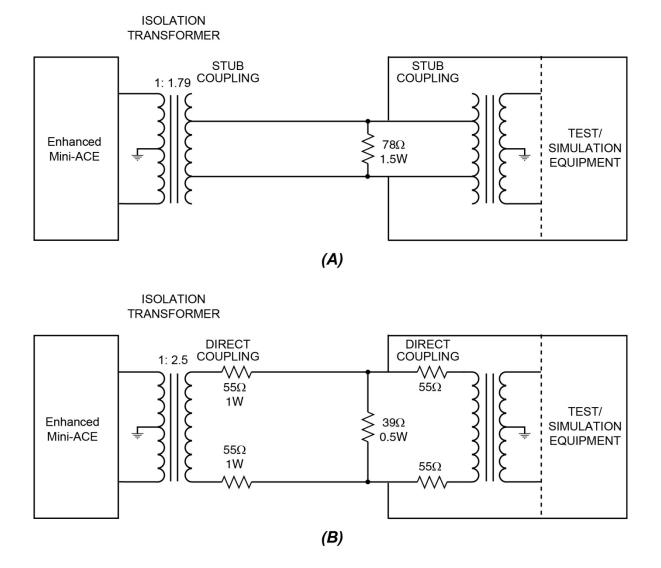

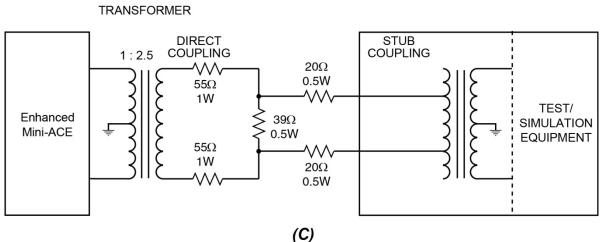

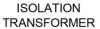

Figure 4 illustrates the interface between the various +5.0V transceiver versions of the Enhanced Mini-ACE series and a MIL-STD-1553 bus. Connections for both direct (short stub) and transformer (long stub) coupling, as well as the peak-to-peak "Nominal" voltage levels that appear at various points (when transmitting), are as indicated in the figure.

Please see for +5.0V isolation transformer limitations and recommendations.

In accordance with MIL-STD-1553B, the turns ratio of the coupling transformer is required to be 1.0 to 1.4. For both coupling configurations, isolation resistors are required to be in series with each leg connecting to the 1553 bus. In the case of direct coupling, the value of the coupling resister is 55 ohms. For direct coupling, the isolation resistors are located within the 1553 BC, RT, or Monitor terminal. In the case of transformer coupled, the resistors are 0.75  $Z_0$  in value and are located in the bus coupler, rather than the BC, RT, or Monitor terminal. The isolation resistors protect the bus against short circuit conditions in the transformers, stubs, or terminal components.

For most system applications, transformer (stub) coupling is preferred over direct coupling. Some of the advantages of transformer coupling are:

(1) Looking from the 1553 bus towards the stub, the effect of the 1.4 to 1.0 stepdown of the coupling transformer will be to **double** the impedance of the stub/terminal combination, as seen by the bus. Since the stub impedance decreases as a function of stub length due to distributed cable capacitance, this doubling effect serves to reduce the amount of impedance loading on the bus by individual terminals. For this reason, stub coupled terminals may be located up to 20 feet from the bus; the distance for direct coupled terminals is limited to 12 inches.

(2) Looking from the isolation transformer down the stub (towards the bus), the impedance seen is  $Z_0$ . Therefore, the characteristic impedance of the stub cabling (78 ohms nominal) matches the stub's load impedance, minimizing reflections back toward the transmitter.

(3) In a direct-coupled terminal, the main bus is not protected against a short circuit in the stub cabling. For the transformer coupled case, the bus is protected against such a fault.

(4) A transformer coupled terminal provides improved DC and common mode isolation over a direct-coupled terminal.

NOTE:  $Z_0 = 70$  TO 85 OHMS

#### Figure 4 Notes:

- 1. Shown for one or two redundant buses that interface to the Enhanced Mini-ACE.

- 2. Transmitted voltage level on 1553 bus is 6 Vp-p min, 7 Vp-p nominal, 9 Vp-p max.

- 3. Required tolerance on isolation resistors is 2%. Instantaneous power dissipation (when transmitted) is approximately 0.5W (typ), 0.8W (max).

### 6.1 +5.0 Volt Isolation Transformers