# BU-65170/61580 AND BU-61585 MIL-STD-1553A/B NOTICE 2 RT AND BC/RT/MT, ADVANCED COMMUNICATION ENGINE (ACE)

# **DESCRIPTION**

DDC's BU-65170, BU-61580 and BU-61585 Bus Controller / Remote Terminal / Monitor Terminal (BC/RT/MT) Advanced Communication Engine (ACE) terminals comprise a complete integrated interface between a host processor and a MIL-STD-1553 A and B or STANAG 3838 bus.

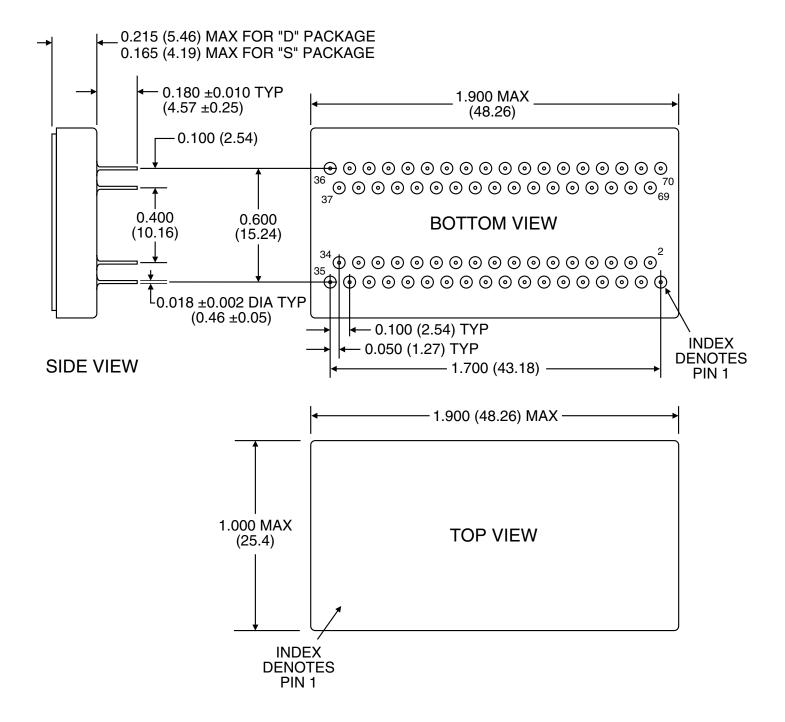

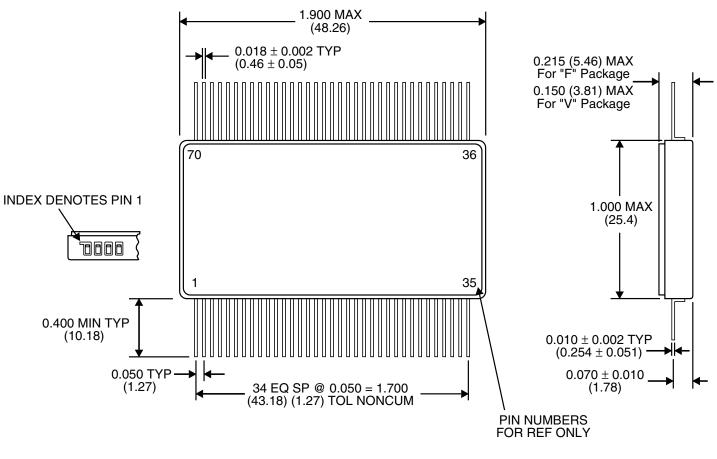

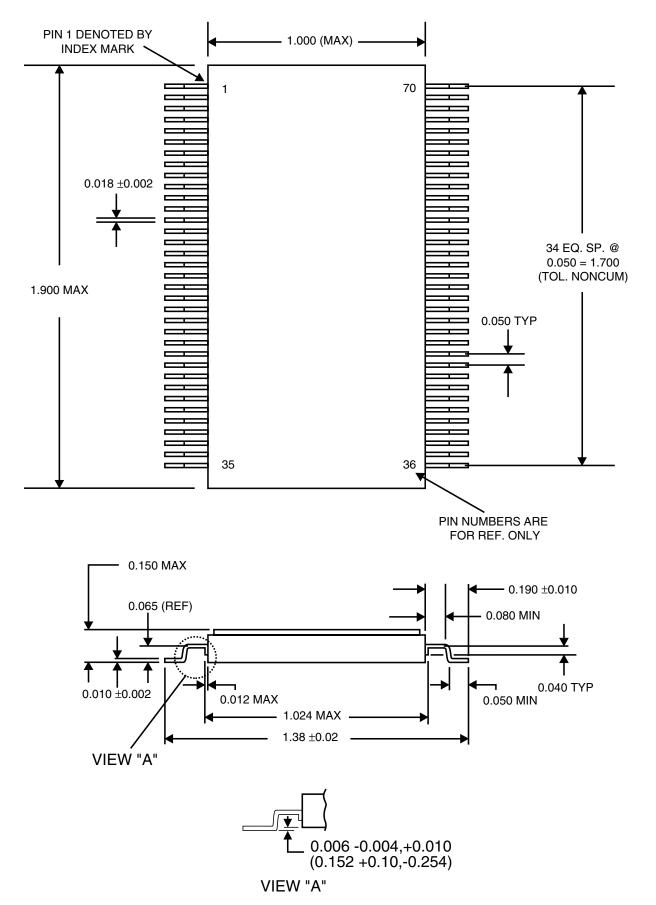

The ACE series is packaged in a 1.9 -square-inch, 70-pin, low-profile, cofired MultiChip Module (MCM) ceramic package that is well suited for applications with stringent height requirements.

The BU-61585 ACE integrates dual transceiver, protocol, memory management, processor interface logic, and a total of 12K words of RAM in a choice of DIP or flat pack packages. The BU-61585 requires +5 V power and either -15 V or -12 V power.

The BU-61585 internal RAM can be configured as 12K x 16 or 8K x 17. The 8K x 17 RAM feature provides capability for memory integrity checking by implementing RAM parity generation and verification on all accesses. To minimize board space and "glue" logic, the ACE provides ultimate flexibility in interfacing to a host processor and internal/ external RAM.

The advanced functional architecture of the ACE terminals provides software compatibility to DDC's Advanced Integrated Multiplexer (AIM) series hybrids, while incorporating a multiplicity of architectural enhancements. It allows flexible operation while off-loading the host processor, ensuring data sample consistency, and supports bulk data transfers. The ACE hybrids may be operated at either 12 or 16 MHz. Wire bond options allow for programmable RT address (hardwired is standard) and external transmitter inhibit inputs.

**Data Device Corporation** 105 Wilbur Place Bohemia, New York 11716 631-567-5600 Fax: 631-567-7358 Make sure the next Card you purchase

# **FEATURES**

- Fully Integrated MIL-STD-1553 Interface Terminal

- Flexible Processor/Memory Interface

- Standard 4K x 16 RAM and Optional 12K x 16 or 8K x 17 RAM Available

- Optional RAM Parity Generation/ Checking

- Automatic BC Retries

- Programmable BC Gap Times

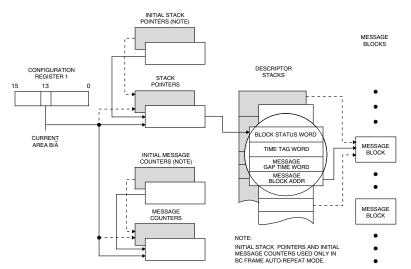

- BC Frame Auto-Repeat

- Flexible RT Data Buffering

- Programmable Illegalization

- Selective Message Monitor

- Simultaneous RT/Monitor Mode

FOR MORE INFORMATION CONTACT:

Technical Support: 1-800-DDC-5757 ext. 7771

All trademarks are the property of their respective owners. © 1992, 1999 Data Device Corporation

| TABLE 1. "ACE" SERIES SPECIFICATIONS                                                                               |                |     |               |              |  |

|--------------------------------------------------------------------------------------------------------------------|----------------|-----|---------------|--------------|--|

| PARAMETER                                                                                                          | MIN            | TYP | MAX           | UNITS        |  |

| ABSOLUTE MAXIMUM RATING Supply Voltage                                                                             |                |     |               |              |  |

| ■ Logic +5V                                                                                                        | -0.3           |     | 7.0           | V            |  |

| ■ Transceiver +5V                                                                                                  | -0.3           |     | 7.0           | V            |  |

| ■ -15V                                                                                                             | -18.0          |     | 0.3           | V            |  |

| ■ -12V                                                                                                             | -18.0          |     | 0.3           | V            |  |

| Logic ■ Voltage Input Range                                                                                        | -0.3           |     | Vcc+0.3       | l v          |  |

| MIL-STD-1553 Transceiver Signals                                                                                   | 0.0            |     | V0010.0       | '            |  |

| ■ BU-6XXXXY3/6                                                                                                     |                |     |               |              |  |

| Powered Input Range (Note 13)                                                                                      | -5V_XCVR - 0.3 |     | 5V_XCVR + 0.3 | V            |  |

| Unpowered Input Range                                                                                              | -1.5           |     | +1.5          | V            |  |

| RECEIVER                                                                                                           |                |     |               |              |  |

| Differential Input Resistance                                                                                      |                |     |               |              |  |

| ■ (BU-65170/61580/61585X1, BU-65170/61580/61585X2) (Notes 1-7)                                                     | 11<br>2.5      |     |               | kΩ<br>kΩ     |  |

| ■ (BU-65170/61580/61585X3, BU-65170/61580/61585X6) (Notes 1-7) Differential Input Capacitance                      | 2.5            |     |               | K22          |  |

| ■ (BU-65170/61580/61585X1, BU-65170/61580/61585X2) (Notes 1-7)                                                     |                | 10  |               | pF           |  |

| ■ (BU-65170/61580/61585X3, BU-65170/61580/61585X6) (Notes 1-7)                                                     |                | 5   |               | pF           |  |

| Threshold Voltage, Transformer Coupled, Measured on Stub                                                           | 0.200          |     | 0.860         | Vp-p         |  |

| Common Mode Voltage (Note 7)                                                                                       |                |     | 10            | Vpeak        |  |

| TRANSMITTER                                                                                                        |                |     |               |              |  |

| Differential Output Voltage                                                                                        |                |     |               |              |  |

| ■ Direct Coupled Across 35 Ω, Measured on Bus                                                                      | 6              | 7   | 9             | Vp-p         |  |

| ■ Transformer Coupled Across 70 Ω, Measured on Bus                                                                 | 00             |     | 0.7           |              |  |

| •(BU-65170/61580/61585X1)<br>•(BU-65170/61580/61585X2,X3, X6)                                                      | 20<br>18       |     | 27<br>27      | Vp-p<br>Vp-p |  |

| Output Noise, Differential (Direct Coupled)                                                                        |                |     | 10            | mVp-p, diff  |  |

| Output Offset Voltage, Transformer Coupled Across 70 ohms                                                          | -250           |     | 250           | mV           |  |

| Rise/Fall Time                                                                                                     | 100            | 150 | 300           | nsec         |  |

| LOGIC                                                                                                              |                |     |               |              |  |

| V <sub>IH</sub>                                                                                                    | 2.0            |     |               | V            |  |

| I V <sub>IL</sub>                                                                                                  |                |     | 0.8           | V            |  |

| I <sub>IH</sub> (Vcc=5.5V, V <sub>IN</sub> =Vcc)<br>  I <sub>IH</sub> (Vcc=5.5V, V <sub>IN</sub> =2.7V)            | -10            |     | 10            | μΑ           |  |

| I I (VCC=3.5 V, VIN=2.7 V)  ■ SSFLAG/EXT_TRIG                                                                      | -692           |     | -84           | μА           |  |

| ■ All Other Inputs                                                                                                 | -346           |     | -42           | μА           |  |

| I <sub>IL</sub> (Vcc=5.5V, V <sub>IN</sub> =0.4V)                                                                  |                |     |               |              |  |

| SSFLAG/EXT_TRIG                                                                                                    | -794           |     | -100          | μΑ           |  |

| ■ All Other Inputs  V <sub>OH</sub> (Vcc=4.5V, V <sub>IH</sub> =2.7V, V <sub>IL</sub> =0.2V, I <sub>OH</sub> =max) | -397<br>2.4    |     | -50           | μA<br>V      |  |

| V <sub>OL</sub> (Vcc=4.5V, V <sub>IH</sub> =2.7V, V <sub>IL</sub> =0.2V, I <sub>OL</sub> =max)                     | 2.4            |     | 0.4           | V            |  |

| I <sub>OL</sub>                                                                                                    |                |     |               |              |  |

| DTREQ/16/8, DTACK/POLARITY_SEL                                                                                     | 6.4            |     |               | mA           |  |

| ■ INCMD, INT MEMENA_OUT, READYD, IOEN, TXA, TXA,                                                                   | "              |     |               | ""           |  |

| TXB, TXB, TX_INH_OUT_A, TX_INH_OUT_B,                                                                              | 3.2            |     |               | mA           |  |

| OH<br>  ■ DB15-DB0, A15-A0, MEMOE/ADDR_LAT,                                                                        |                |     |               |              |  |

| MEMWR/ ZEROWAIT, DTREQ/16/8, DTACK/POLARITY_SEL                                                                    |                |     | -6.4          | mA           |  |

| ■ ĪNCMD, ĪNT, MEMENA_OUT, READYD, ĪOEN, TXA, TXA, TXB, TXB, TX INH_OUT_A, TX_INH_OUT_B,                            |                |     | -3.2          | mA           |  |

| C <sub>1</sub> (Input Capacitance)                                                                                 |                |     | 50            | pF           |  |

| C <sub>IO</sub> (Bi-directional signal input capacitance)                                                          |                |     | 50            | pF           |  |

|                                                                                                                    |                |     |               |              |  |

|                                                                                                                    |                |     |               |              |  |

| TABLE 1. "ACE" SERIES SPECIFICATIONS (CONTD)                |        |       |        |           |  |

|-------------------------------------------------------------|--------|-------|--------|-----------|--|

| PARAMETER                                                   | MIN    | TYP   | MAX    | UNITS     |  |

| POWER SUPPLY REQUIREMENTS                                   |        |       |        |           |  |

| Voltages/Tolerances                                         |        |       |        |           |  |

| ■ BU-65170/61580/61585X1                                    |        |       |        |           |  |

| • +5V (Logic)                                               | 4.5    | 5.0   | 5.5    | V         |  |

| • +5V (Ch. A, Ch. B)                                        | 4.5    | 5.0   | 5.5    | V         |  |

| • -15V (Ch. A, Ch. B)                                       | -15.75 | -15.0 | -14.25 | V         |  |

| ■ BU-65170/61580/61585X2                                    |        |       |        |           |  |

| • +5V (Logic)                                               | 4.5    | 5.0   | 5.5    | V         |  |

| • +5V (Ch. A, Ch. B)                                        | 4.5    | 5.0   | 5.5    | V         |  |

| • -12V (Ch. A, Ch. B)                                       | -12.6  | -12.0 | -11.4  | V         |  |

| ■ BU-65170/61580/61585X3, BU-65170/61580/61585X6            |        |       |        |           |  |

| • +5V (Logic)                                               | 4.5    | 5.0   | 5.5    | V         |  |

| • +5V (Ch. A, Ch. B)                                        | 4.75   | 5.0   | 5.25   | V         |  |

| Current Drain (Total Hybrid)                                |        |       | 0      |           |  |

| ■ BU-65170/61580X1                                          |        |       |        |           |  |

| • +5V (Logic, Ch. A, Ch. B)                                 |        | 95    | 190    | mA        |  |

| • -15V (Ch. A, Ch. B)                                       |        |       | 100    | 11173     |  |

| • Idle                                                      |        | 30    | 60     | mA        |  |

| • 25% Transmitter Duty Cycle                                |        | 68    | 108    | mA        |  |

| • 50% Transmitter Duty Cycle                                |        | 105   | 160    | mA        |  |

| 100% Transmitter Duty Cycle                                 |        | 180   | 255    | mA        |  |

| ■ BU-65170/61580X2                                          |        | 100   | 255    | 111/4     |  |

| • +5V (Logic, Ch. A, Ch. B)                                 |        | 95    | 190    | mA        |  |

| • -12V (Ch. A, Ch. B)                                       |        | 90    | 190    | IIIA      |  |

| • Idle                                                      |        | 30    | 60     | m 1       |  |

| • 25% Transmitter Duty Cycle                                |        | 80    | 120    | mA<br>m A |  |

| • 50% Transmitter Duty Cycle                                |        | 130   | 185    | mA<br>m A |  |

| 100% Transmitter Duty Cycle     100% Transmitter Duty Cycle |        | 230   | 305    | mA<br>mA  |  |

| ■ BU-65170/61580X3, BU-65170/61580X6                        |        | 230   | 305    | mA        |  |

| • +5V (Logic, Ch. A, Ch. B)                                 |        |       |        |           |  |

| • Idle                                                      |        | 116   | 100    | А         |  |

|                                                             |        | _     | 160    | mA        |  |

| • 25% Transmitter Duty Cycle                                |        | 222   | 265    | mA        |  |

| • 50% Transmitter Duty Cycle                                |        | 328   | 370    | mA        |  |

| • 100% Transmitter Duty Cycle                               |        | 540   | 580    | mA        |  |

| ■ BU-61585X1                                                |        | 105   | 040    |           |  |

| • +5V (Logic, Ch. A, Ch. B)                                 |        | 105   | 240    | mA        |  |

| • -15V (Ch. A, Ch. B)                                       |        | 00    |        |           |  |

| • Idle                                                      |        | 30    | 60     | mA        |  |

| • 25% Transmitter Duty Cycle                                |        | 68    | 108    | mA        |  |

| • 50% Transmitter Duty Cycle                                |        | 105   | 160    | mA        |  |

| • 100% Transmitter Duty Cycle                               |        | 180   | 255    | mA        |  |

| ■ BU-61585X2                                                |        |       |        |           |  |

| • +5V (Logic, Ch. A, Ch. B)                                 |        | 105   | 240    | mA        |  |

| • -12V (Ch. A, Ch. B)                                       |        | 22    |        | l .       |  |

| • Idle                                                      |        | 30    | 60     | mA        |  |

| 25% Transmitter Duty Cycle     50% Transmitter Duty Cycle   |        | 80    | 120    | mA        |  |

| • 50% Transmitter Duty Cycle                                |        | 130   | 185    | mA        |  |

| • 100% Transmitter Duty Cycle                               |        | 230   | 305    | mA        |  |

| ■ BU-61585X3, BU-61585X6                                    |        |       |        |           |  |

| • +5V (Logic, Ch. A, Ch. B)                                 |        |       |        |           |  |

| • Idle                                                      |        | 126   | 170    | mA        |  |

| • 25% Transmitter Duty Cycle                                |        | 232   | 275    | mA        |  |

| • 50% Transmitter Duty Cycle                                |        | 338   | 380    | mA        |  |

| 100% Transmitter Duty Cycle                                 |        | 550   | 590    | mA        |  |

|                                                             |        |       |        |           |  |

|                                                             |        |       |        |           |  |

|                                                             |        |       |        |           |  |

| TABLE 1. "ACE" SERIES SPECIFICATIONS (CONTD) |     |       |      |       |  |

|----------------------------------------------|-----|-------|------|-------|--|

| PARAMETER                                    | MIN | TYP   | MAX  | UNITS |  |

| POWER DISSIPATION                            |     |       |      |       |  |

| Total Hybrid                                 |     |       |      |       |  |

| ■ BU-65170/61580X1                           |     |       |      |       |  |

| • Idle                                       |     | 0.850 | 1.85 | W     |  |

| • 25% Transmitter Duty Cycle                 |     | 1.195 | 2.25 | W     |  |

| • 50% Transmitter Duty Cycle                 |     | 1.450 | 2.72 | W     |  |

| • 100% Transmitter Duty Cycle                |     | 1.975 | 3.52 | W     |  |

| ■ BU-65170/61580X2                           |     |       |      |       |  |

| • Idle                                       |     | 0.835 | 1.67 | W     |  |

| • 25% Transmitter Duty Cycle                 |     | 1.135 | 2.10 | W     |  |

| • 50% Transmitter Duty Cycle                 |     | 1.435 | 2.59 | W     |  |

| • 100% Transmitter Duty Cycle                |     | 2.035 | 3.46 | W     |  |

| ■ BU-65170/61580X3, BU-65170/61580X6         |     |       |      |       |  |

| • Idle                                       |     | 0.64  | 0.88 | l w   |  |

| • 25% Transmitter Duty Cycle                 |     | 0.93  | 1.11 | W     |  |

| • 50% Transmitter Duty Cycle                 |     | 1.22  | 1.33 | W     |  |

| • 100% Transmitter Duty Cycle                |     | 1.81  | 1.97 | l w   |  |

| ■ BU-61585X1                                 |     |       | _    |       |  |

| • Idle                                       |     | 0.900 | 2.10 | W     |  |

| 25% Transmitter Duty Cycle                   |     | 1.245 | 2.50 | W     |  |

| • 50% Transmitter Duty Cycle                 |     | 1.500 | 2.97 | W     |  |

| 100% Transmitter Duty Cycle                  |     | 2.025 | 3.77 | W     |  |

| ■ BU-61585X2                                 |     |       |      |       |  |

| • Idle                                       |     | 0.885 | 1.92 | W     |  |

| • 25% Transmitter Duty Cycle                 |     | 1.185 | 2.35 | W     |  |

| • 50% Transmitter Duty Cycle                 |     | 1.485 | 2.84 | W     |  |

| • 100% Transmitter Duty Cycle                |     | 2.085 | 3.71 | W     |  |

| ■ BU-61585X3, BU-61585X6                     |     |       |      |       |  |

| • Idle                                       |     | 0.69  | 0.93 | W     |  |

| • 25% Transmitter Duty Cycle                 |     | 0.98  | 1.16 | W     |  |

| • 50% Transmitter Duty Cycle                 |     | 1.27  | 1.38 | W     |  |

| • 100% Transmitter Duty Cycle                |     | 1.86  | 2.02 | W     |  |

| Hottest Die                                  |     |       |      |       |  |

| ■ BU-65170/61580X1                           |     |       |      |       |  |

| • Idle                                       |     | 0.335 | 0.68 | W     |  |

| • 25% Transmitter Duty Cycle                 |     | 0.600 | 1.06 | W     |  |

| • 50% Transmitter Duty Cycle                 |     | 0.860 | 1.45 | W     |  |

| • 100% Transmitter Duty Cycle                |     | 1.385 | 2.23 | W     |  |

| ■ BU-65170/61580X2                           |     |       |      | l     |  |

| • Idle                                       |     | 0.290 | 0.59 | W     |  |

| • 25% Transmitter Duty Cycle                 |     | 0.590 | 0.92 | W     |  |

| • 50% Transmitter Duty Cycle                 |     | 0.890 | 1.36 | W     |  |

| • 100% Transmitter Duty Cycle                |     | 1.490 | 2.16 | W     |  |

| ■ BU-65170/61580X3, BU-65170/61580X6         |     | 0.40  | 0.00 | l ,,, |  |

| • Idle                                       |     | 0.18  | 0.28 | W W   |  |

| • 25% Transmitter Duty Cycle                 |     | 0.42  | 0.51 | W W   |  |

| • 50% Transmitter Duty Cycle                 |     | 0.66  | 0.75 | W W   |  |

| • 100% Transmitter Duty Cycle                |     | 1.14  | 1.22 | W     |  |

| ■ BU-61585X1                                 |     | 0.005 | 0.00 | l ,,, |  |

| • Idle                                       |     | 0.335 | 0.68 | W     |  |

| • 25% Transmitter Duty Cycle                 |     | 0.600 | 1.06 | W W   |  |

| • 50% Transmitter Duty Cycle                 |     | 0.860 | 1.45 | W W   |  |

| • 100% Transmitter Duty Cycle                |     | 1.385 | 2.23 | W     |  |

| ■ BU-61585X2                                 |     | 0.000 | 0.50 | ١,,,  |  |

| • Idle                                       |     | 0.290 | 0.59 | W W   |  |

| • 25% Transmitter Duty Cycle                 |     | 0.590 | 0.92 | W W   |  |

| • 50% Transmitter Duty Cycle                 |     | 0.890 | 1.36 | W W   |  |

| • 100% Transmitter Duty Cycle                |     | 1.490 | 2.16 | W     |  |

| ■ BU-61585X3, BU-61585X6                     |     | 0.40  | 0.00 | l ,,, |  |

| • Idle                                       |     | 0.18  | 0.28 | W     |  |

| • 25% Transmitter Duty Cycle                 |     | 0.42  | 0.51 | W W   |  |

| • 50% Transmitter Duty Cycle                 |     | 0.66  | 0.75 | W     |  |

| • 100% Transmitter Duty Cycle                |     | 1.14  | 1.22 | W     |  |

|                                              |     |       |      |       |  |

|                                              |     |       | l    | I     |  |

| TABLE 1. "ACE" SERIES SPECIFICATIONS (CONTD)                                                                                                                                                                        |                                  |                                                              |                                  |                            |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--------------------------------------------------------------|----------------------------------|----------------------------|--|

| PARAMETER                                                                                                                                                                                                           | MIN                              | TYP                                                          | MAX                              | UNITS                      |  |

| CLOCK INPUT Frequency ■ Nominal Value (programmable) • Default Mode                                                                                                                                                 |                                  | 16.0                                                         |                                  | MHz                        |  |

| Software Programmable Option     Long Term Tolerance                                                                                                                                                                |                                  | 12.0                                                         | 0.04                             | MHz                        |  |

| • 1553A Mode • 1553B Mode ■ Short Term Tolerance, 1 second                                                                                                                                                          |                                  |                                                              | 0.01<br>0.1                      | %                          |  |

| 1553A Mode     1553B Mode     Duty Cycle                                                                                                                                                                            |                                  |                                                              | 0.001<br>0.01                    | %                          |  |

| • 16 MHz<br>• 12 MHz                                                                                                                                                                                                | 33<br>40                         |                                                              | 67<br>60                         | %<br>%                     |  |

| 1553 MESSAGE TIMING Completion of CPU Write (BC Start)-to-Start of Next Message BC Intermessage Gap (Note 8) BC/RT/MT Response Timeout (Note 9)                                                                     |                                  | 2.5<br>9.5                                                   |                                  | μ <b>s</b><br>μ <b>s</b>   |  |

| <ul> <li>18.5 nominal</li> <li>22.5 nominal</li> <li>50.5 nominal</li> <li>128.0 nominal</li> <li>RT Response Timeout (Note 11)</li> </ul>                                                                          | 17.5<br>21.5<br>49.5<br>127<br>4 | 18.5<br>22.5<br>50.5<br>129.5                                | 19.5<br>23.5<br>51.5<br>131<br>7 | μs<br>μs<br>μs<br>μs<br>μs |  |

| Transmitter Watchdog Timeout  THERMAL                                                                                                                                                                               |                                  | 668                                                          |                                  | μS                         |  |

| Thermal Resistance, Junction-to-Case, Hottest Die (θJC) ■ BU-65170/61580/61585X1, BU-65170/61580/61585X2 ■ BU-65170/61580/61585X3, BU-65170/61580/61585X6 Storage Temperature Lead Temperature (soldering, 10 sec.) | -65                              |                                                              | 6.99<br>6.8<br>150<br>+300       | °C/W<br>°C/W<br>°C<br>°C   |  |

| PHYSICAL CHARACTERISTICS Size ■ BU-65170/61580/61585 S                                                                                                                                                              |                                  | 1.9 X 1.0 X 0.16                                             |                                  | in.                        |  |

| ■ BU-65170/61580/61585 V                                                                                                                                                                                            |                                  | (48.3 x 25.4 x 4.1<br>1.9 X 1.0 X 0.15<br>(48.3 x 25.4 x 3.8 | 0                                | (mm)<br>in.<br>(mm)        |  |

| Weight ■ BU-65170/61580/61585 S/V                                                                                                                                                                                   |                                  | 0.6 (17) oz (                                                |                                  |                            |  |

Notes for Table 1: Notes 1 through 6 are applicable to the Receiver Differential Resistance and Differential Capacitance specifications:

- (1) Specifications include both transmitter and receiver (tied together internally).

- (2) Measurement of impedance is directly between pins TX/RX A(B) and TX/RX A(B) of the BU-65170/61580XX hybrid.

- (3) Assuming the connection of all power and ground inputs to the hybrid.

- (4) The specifications are applicable for both unpowered and powered conditions.

- (5) The specifications assume a 2 volt rms balanced, differential, sinusoidal input. The applicable frequency range is 75 kHz to 1 MHz.

- (6) Minimum resistance and Typical capacitance parameters are guaranteed, but not tested, over the operating range.

- (7) Assumes a common mode voltage within the frequency range of dc to 2MHz, applied to pins of the isolation transformer on the stub side (either direct or transformer coupled), referenced to hybrid ground. Use a DDC recommended transformer or other transformer that provides an equivalent minimum CMRR.

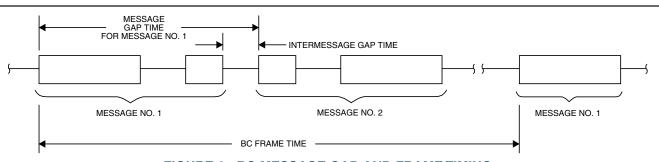

- (8) Typical value for minimum intermessage gap time. Under software control, may be lengthened to (65,535µs minus message time), in increments of 1µs.

- (9) Software programmable (4 options). Includes RT-to-RT Timeout (Mid-Parity of Transmit Command to Mid-Sync of Transmitting RT Status).

- (10) For both +5V logic and transceiver. +5V for channels A and B.

- (11) Measured from mid-parity crossing of Command Word to mid-sync crossing of RT's Status Word.

- (12) Specifications for BU-65171, BU-61581, and BU-61586 are identical to the specifications for the BU-65170, BU-61580, and BU-61585 respectively.

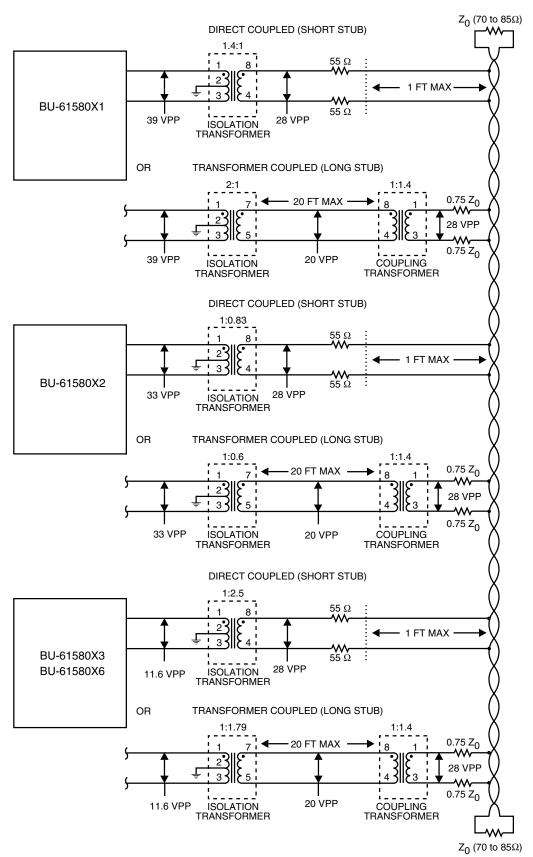

- (13) Assuming the use of isolation transformers with the turns ratios shown in Figure 18 and in the absence of common mode signal on the 1553 stub, this equates to a nominal stub voltage of 38 Volts<sub>PK-to-PK</sub> transformer-coupled, or 53 Volts<sub>PK-to-PK</sub> direct-coupled.

#### INTRODUCTION

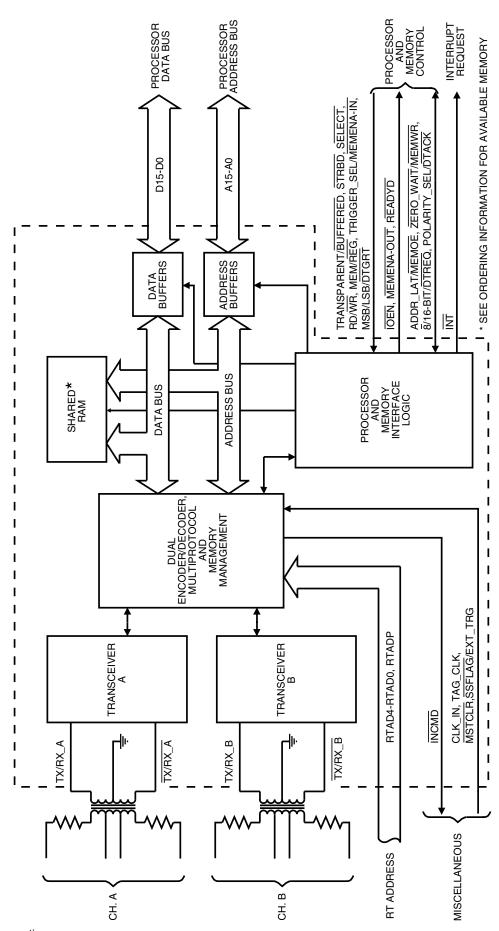

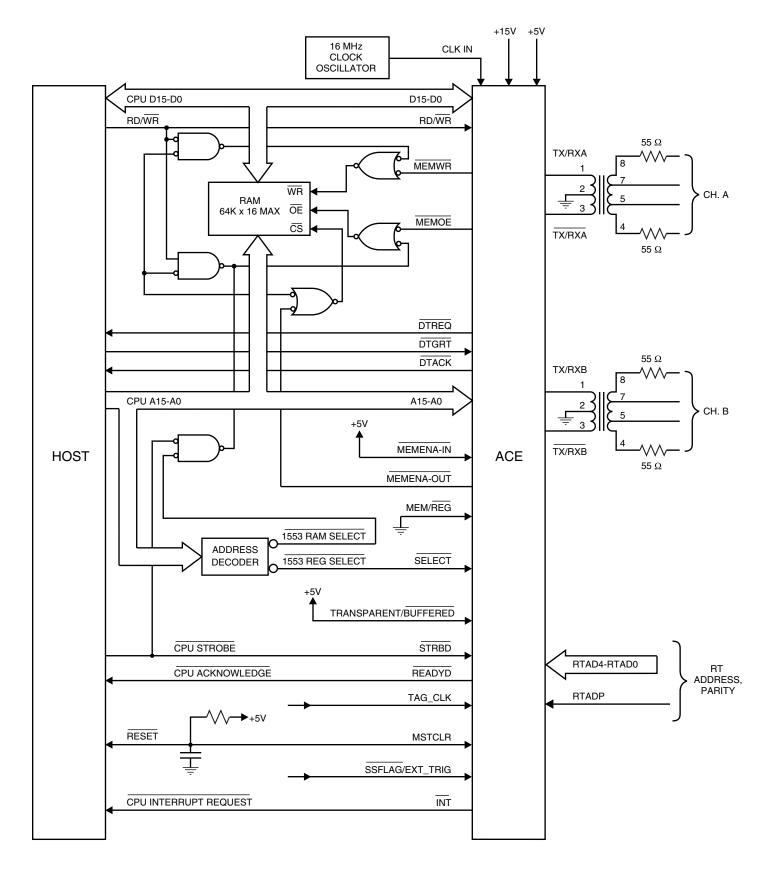

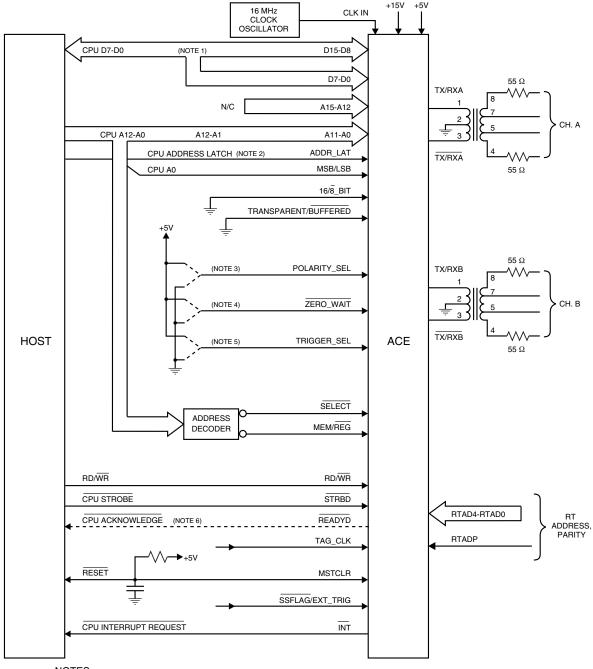

DDC's ACE series of Integrated BC/RT/MT hybrids provide a complete, flexible interface between a microprocessor and a MIL-STD-1553A, B Notice 2, McAir, or STANAG 3838 bus, implementing Bus Controller, Remote Terminal (RT) and Monitor Terminal (MT) modes. Packaged in a single 1.9-square-inch, 70-pin DIP or surface mountable flatpack or J-lead package, the ACE series contains dual low-power transceivers and encoder/decoders, complete BC/RT/MT multi-protocol logic, memory management and interrupt logic, 4K x 16 of shared static RAM and a direct, buffered interface to a host processor bus.

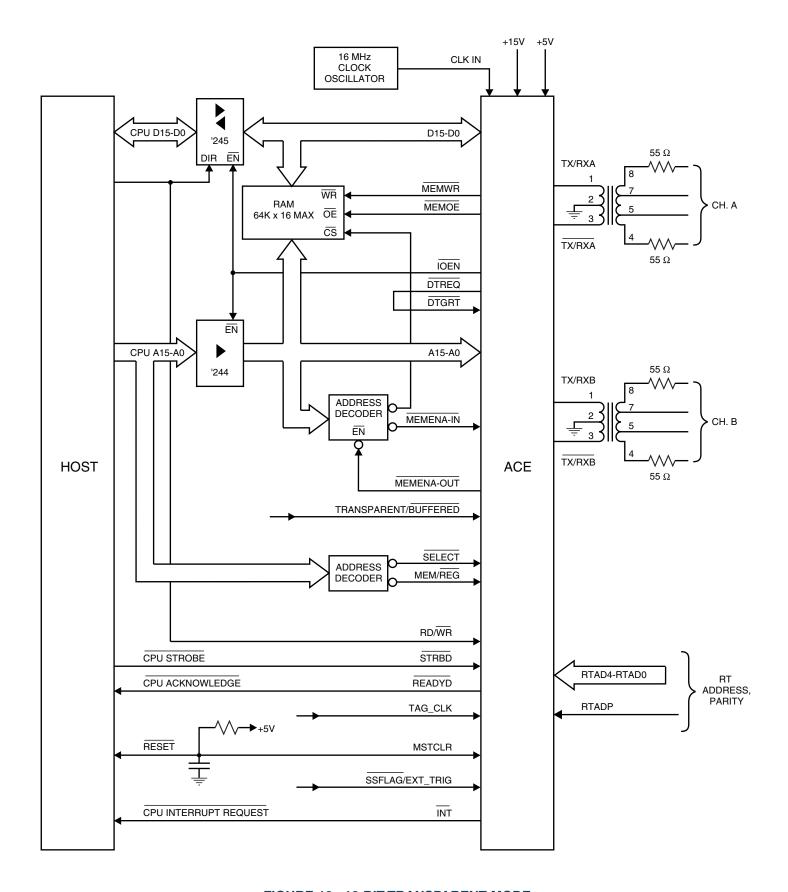

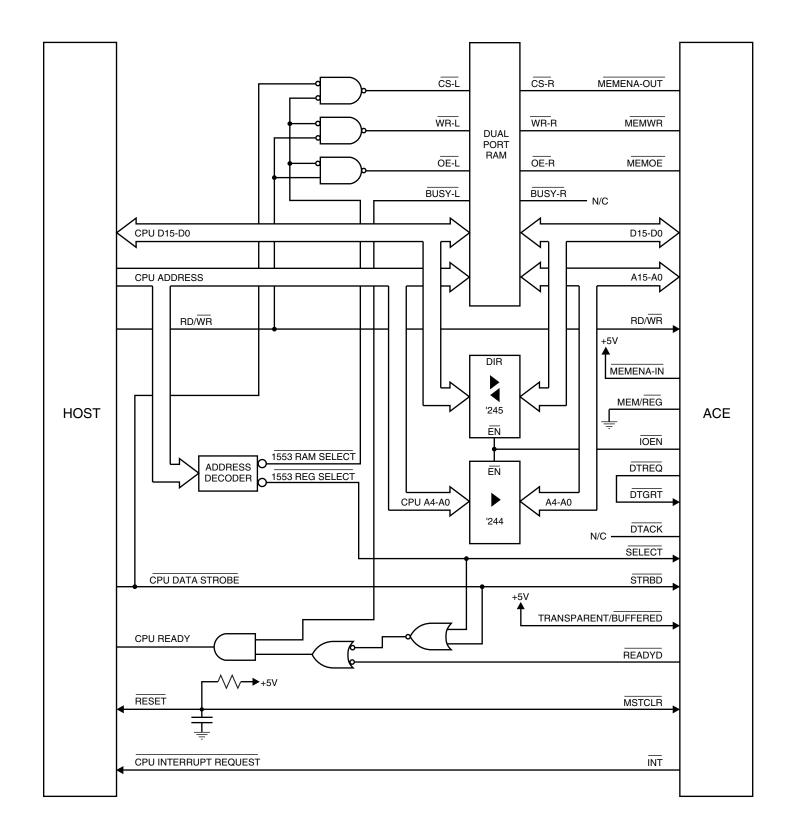

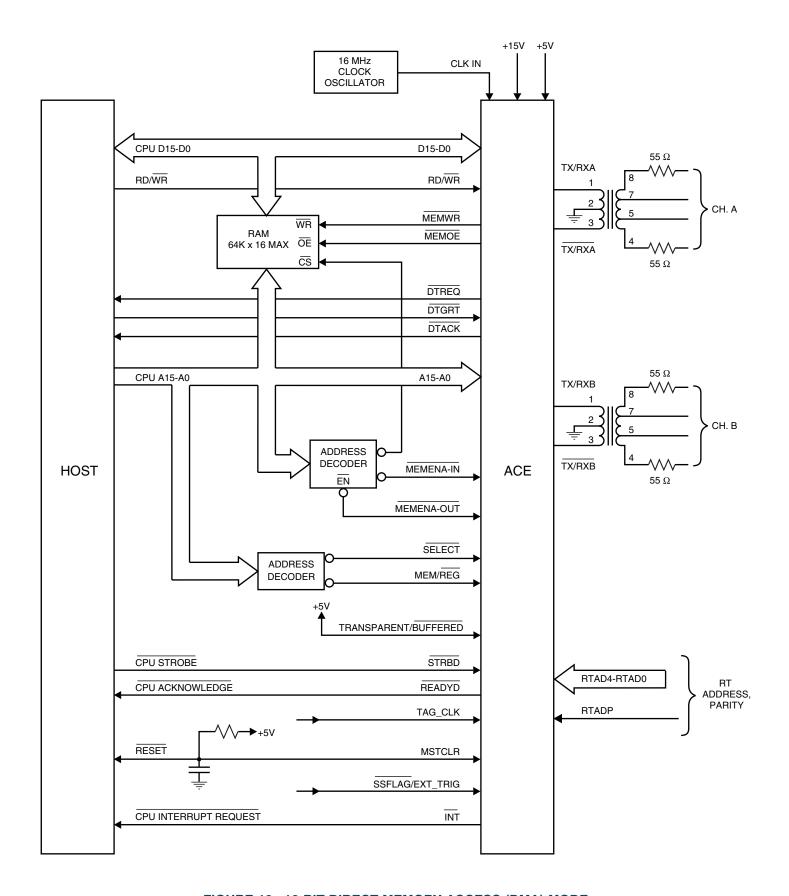

The BU-65170/61580 contains internal address latches and bidirectional data buffers to provide a direct interface to a host processor bus. The BU-65170/61580 may be interfaced directly to both 16-bit and 8-bit microprocessors in a buffered shared RAM configuration. In addition, the ACE may connect to a 16-bit processor bus via a Direct Memory Access (DMA) interface. The BU-65170/61580 includes 4K words of buffered RAM. Alternatively, the ACE may be interfaced to as much as 64K words of external RAM in either the shared RAM or DMA configurations.

The ACE RT mode is multiprotocol, supporting MIL-STD-1553A, MIL-STD-1553B Notice 2, STANAG 3838 (including EFAbus), and the McAir A3818, A5232, and A5690 protocols. Full compliance to the McAir specs, however, requires the use of a sinusoidal transceiver (transceiver option 5). Refer to the BU-61590 data sheet for additional information on McAir terminals.

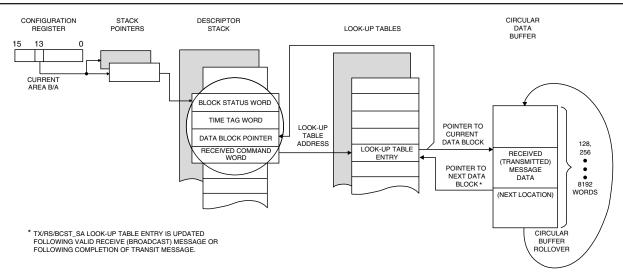

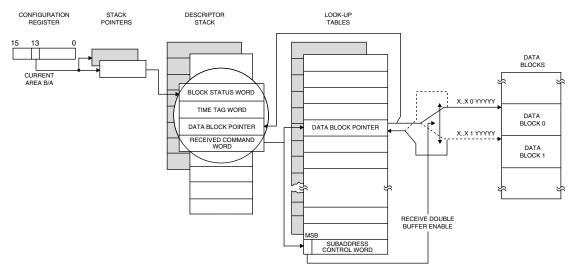

The memory management scheme for RT mode provides an option for separation of broadcast data, in compliance with 1553B Notice 2. Both double buffer and circular buffer options are programmable by subaddress. These features serve to ensure data consistency and to off-load the host processor for bulk data transfer applications.

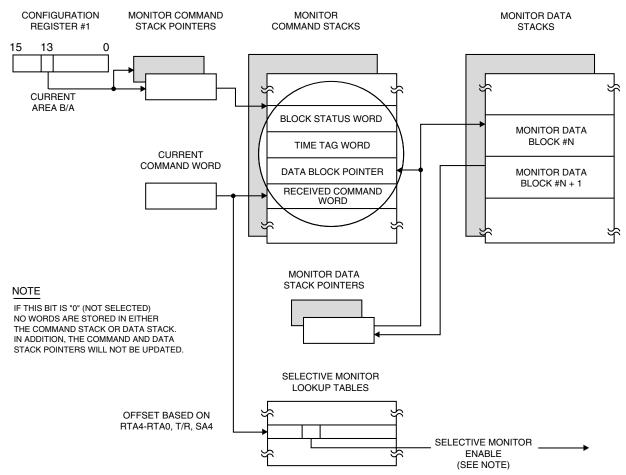

The ACE series implements three monitor modes: a word monitor, a selective message monitor, and a combined RT/selective monitor. Other features include options for automatic retries and programmable intermessage gap for BC mode, an internal Time Tag Register, an Interrupt Status Register and internal command illegalization for RT mode.

# FUNCTIONAL OVERVIEW TRANSCEIVERS

The transceivers in the BU-65170/61580X3(X6) are fully monolithic, requiring only a +5 volt power input. Besides eliminating the need for an additional power supply, the use of a 5 volt (only) transceiver requires the use of step-up, rather than step-down, isolation transformers. This provides the advantage of a higher terminal input impedance than is possible for a 15 volt or 12 volt transmitter. As a result, there is greater margin for the input impedance test, mandated for 1553 validation testing. This allows

for longer cable lengths between an LRU's system connector and the isolation transformers of an embedded 1553 terminal.

For the +5 V and -15 V/-12 V front end, the BU-65170/61580X1(X2) uses low-power bipolar analog monolithic and thick-film hybrid technology. The transceiver requires +5 V and -15 V (-12 V) only (requiring no +15 V/+12 V) and includes voltage source transmitters. The voltage source transmitters provide superior line driving capability for long cables and heavy amounts of bus loading. In addition, the monolithic transceivers in the BU-65170/61580X1 provide a minimum stub voltage level of 20 volts peak-to-peak transformer coupled, making them suitable for MIL-STD-1760 applications.

The receiver sections of the BU-65170/61580 are fully compliant with MIL-STD-1553B in terms of front end overvoltage protection, threshold, common mode rejection, and word error rate. In addition, the receiver filters have been designed for optimal operation with the J´ chip's Manchester II decoders.

## J' DIGITAL MONOLITHIC

The J´ digital monolithic represents the cornerstone element of the ACE family of terminals. The development of the J´chip represents the fifth generation of 1553 protocol and interface design for DDC. Over the years, DDC's 1553 protocol and interface design has evolved from: (1) discrete component sets, consisting of multiple hybrids (with large numbers of chips inside the individual hybrids) and programmable logic devices, to (2) multiple custom ASICs to perform the functions of encoder/decoder and RT protocol within a single hybrid, to (3) the BUS-61553 Advanced Integrated Mux Hybrid (AIM-HY) series, containing, in addition to a dual monolithic/thick-film transceiver and discrete RAM chips, a custom protocol chip and a separate custom memory management/processor interface chip, to (4) the BUS-61559 Advanced Integrated Mux Hybrids with Enhanced RT Features (AIM-HY'er — the AIM-HY'er series includes memory management and processor interface functions beyond those of the AIM-HY series), to (5) the full integration of the J´chip.

The J´ chip consists of a dual encoder/decoder, complete protocol for Bus Controller (BC), 1553A/B/McAir Remote Terminal (RT), and Monitor (MT) modes; memory management and interrupt logic; a flexible, buffered interface to a host processor bus and optional external RAM; and 4K words of on-chip RAM. Reference the region within the dotted line of FIGURE 1. Besides realizing all the protocol, memory management, and interface functions of the earlier AIM-HY'er series, the J´ chip includes a large number of enhancements to facilitate hardware and software design, and to further off-load the 1553 terminal's host processor.

## **DECODERS**

The default mode of operation for the BU-65170 RT and BU-61580 BC/RT/MT requires a 16 MHz clock input. If needed, a software programmable option allows the device to be operat-

ed from a 12 MHz clock input. Most current 1553 decoders sample using a 10 MHz or 12 MHz clock. In the 16 MHz mode (default following a hardware or software reset), the ACE decoders sample 1553 serial data using the 16 MHz clock. In the 12 MHz mode, the decoders sample using both clock edges; this provides a sampling rate of 24 MHz. The faster sampling rate for the J´ chip's Manchester II decoders provides superior performance in terms of bit error rate and zero-crossing distortion tolerance.

For interfacing to fiber optic transceivers for MIL-STD-1773 applications, a transceiverless version of the J´chip, the BU-65620, can be used. These versions provide a pin-programmable option for a direct interface to the single-ended outputs of a fiber optic receiver. No external logic is needed.

#### TIME TAGGING

The ACE includes an internal read/writable Time Tag Register. This register is a CPU read/writable 16-bit counter with a programmable resolution of either 2, 4, 8, 16, 32, or 64  $\mu s$  per LSB. Also, the Time Tag Register may be clocked from an external oscillator. Another option allows software-controlled incrementing of the Time Tag Register. This supports self-testing for the Time Tag Register. For each message processed, the value of the Time Tag register is loaded into the second location of the respective descriptor stack entry ("TIME TAG WORD") for both BC and RT modes.

Additional provided options will: clear the Time Tag Register following a Synchronize (without data) mode command or load the Time Tag Register following a Synchronize (with data) mode command; enable an interrupt request and a bit setting in the Interrupt Status Register when the Time Tag Register rolls over from 0000 to FFFF. Assuming the Time Tag Register is not loaded or reset, this will occur at approximately 4-second time intervals, for 64  $\mu s/LSB$  resolution, down to 131 ms intervals, for 2  $\mu s/LSB$  resolution.

Another programmable option for RT mode is the automatic clearing of the Service Request Status Word bit following the ACE's response to a Transmit Vector Word mode command.

# **INTERRUPTS**

The ACE series components provide many programmable options for interrupt generation and handling. The interrupt output pin (INT) has three software programmable modes of operation: a pulse, a level output cleared under software control, or a level output automatically cleared following a read of the Interrupt Status Register.

Individual interrupts are enabled by the Interrupt Mask Register. The host processor may easily determine the cause of the interrupt by using the Interrupt Status Register. The Interrupt Status Register provides the current state of the interrupt conditions. The Interrupt Status Register may be updated in two ways. In the standard interrupt handling mode, a particular bit in the Interrupt Status Register will be updated only if the condition exists and the corresponding bit in the Interrupt Mask Register is enabled. In the enhanced interrupt handling mode, a particular bit in the

Interrupt Status Register will be updated if the condition exists regardless of the contents of the corresponding Interrupt Mask Register bit. In any case, the respective Interrupt Mask Register bit enables an interrupt for a particular condition.

# ADDRESSING, INTERNAL REGISTERS, AND MEMORY MANAGEMENT

The software interface of the BU-65170/61580 to the host processor consists of 17 internal operational registers for normal operation, an additional 8 test registers, plus 64K x 16 of shared memory address space. The BU-65170/61580's 4K x 16 of internal RAM resides in this address space. Reference TABLE 2 and 24.

Definition of the address mapping and accessibility for the ACE's 17 non-test registers, and the test registers, is as follows:

**Interrupt Mask Register** is used to enable and disable interrupt requests for various conditions.

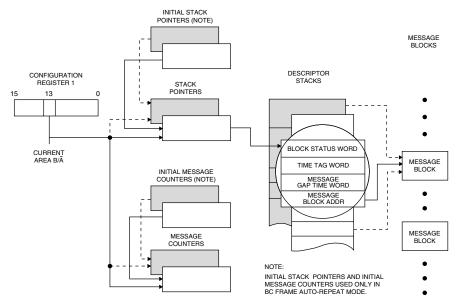

**Configuration Registers #1 and #2** are used to select the BU-61580's mode of operation, and for software control of RT Status Word bits, Active Memory Area, BC Stop-on-Error, RT Memory Management mode selection, and control of the Time Tag operation.

**Start/Reset Register** is used for "command" type functions, such as software reset, BC/MT Start, Interrupt Reset, Time Tag Reset, and Time Tag Register Test. The Start/Reset Register includes provisions for stopping the BC in its auto-repeat mode, either at the end of the current message or at the end of the current BC frame.

**BC/RT Command Stack Pointer Register** allows the host CPU to determine the pointer location for the current or most recent message when the BU-61580 is in BC or RT modes.

BC Control Word/RT Subaddress Control Word Register: In BC mode, it allows host access to the current, or most recent BC Control Word. The BC Control Word contains bits that select the active bus and message format, enable off-line self-test, masking of Status Word bits, enable retries and interrupts, and specify MIL-STD-1553A or -1553B error handling. In RT mode, this register allows host access to the current or most recent Subaddress Control Word. The Subaddress Control Word is used to select the memory management scheme and enable interrupts for the current message. The read/write accessibility can be used as an aid for testing the ACE.

Time Tag Register maintains the value of a real-time clock. The resolution of this register is programmable from among 2, 4, 8, 16, 32, and 64  $\mu$ s/LSB. The TAG\_CLK input signal also may cause an external oscillator to clock the Time Tag Register. Start-of-Message (SOM) and End-of-Message (EOM) sequences in BC, RT, and Message Monitor modes cause a write of the current value of the Time Tag Register to the stack area of RAM.

**Interrupt Status Register** mirrors the Interrupt Mask Register and contains a Master Interrupt bit. It allows the host processor to determine the cause of an interrupt request by means of a single READ operation.

**Configuration Registers #3, #4, and #5** are used to enable many of the BU-61580's advanced features. These include all the enhanced mode

features: that is, all the functionality beyond that of the previous generation product, the BUS-61559 Advanced Integrated Mux Hybrid with Enhanced RT Features (AIM-HY'er). For all three modes, use of the Enhanced Mode enables the various read-only bits in Configuration Register #1. For BC mode, the enhanced mode features include the expanded BC Control Word and BC Block Status Word, additional Stop-On-Error and Stop-On-Status Set functions, frame auto-repeat, programmable intermessage gap times, automatic retries, expanded Status Word Masking, and the capability to generate interrupts following the completion of any selected message. For RT mode, the enhanced mode features include the expanded RT Block Status Word, the combined RT/Selective Message Monitor mode, internal wrapping of the RTFAIL output signal (from the J´chip) to the RTFLAG RT Status Word bit, the double buffering scheme for individual receive (broadcast) subaddresses, and the alternate (fully software programmable) RT Status Word. For MT mode, use of the enhanced mode enables use of the Selective Message Monitor, the combined RT/Selective Monitor modes, and the monitor triggering capability.

**Data Stack Address Register** is used to point to the current address location in shared RAM used for storing message words (second Command Words, Data Words, RT Status Words) in the Selective Word Monitor mode.

Frame Time Remaining Register provides a read only indication of the time remaining in the current BC frame. The resolution of this register is 100 µs/LSB.

**Message Time Remaining Register** provides a read only indication of the time remaining before the start of the next message in a BC frame. The resolution of this register is 1  $\mu$ s/LSB.

BC Frame/RT Last Command/MT Trigger Word Register: In BC mode, it programs the BC frame time, for use in the frame auto-repeat mode. The resolution of this register is 100  $\mu s/LSB$ , with a range of 6.55 seconds; in RT mode, this register stores the current (or most previous) 1553 Command Word processed by the ACE RT; in the Word Monitor mode, this register specifies a 16-bit Trigger (Command) Word. The Trigger Word may be used to start or stop the monitor, or to generate interrupts.

Status Word Register and BIT Word Registers provide read-only indications of the BU-65170/61580's RT Status and BIT Words.

**Test Mode Registers 0-7:** These registers may be used to facilitate production or maintenance testing of the BU-65170/61580 and systems incorporating the BU-65170/61580.

|               | TABLE 2. ADDRESS MAPPING |    |           |            |    |                                                                     |

|---------------|--------------------------|----|-----------|------------|----|---------------------------------------------------------------------|

| ADDRESS LINES |                          |    |           | NES        |    | REGISTER<br>DESCRIPTION/ACCESSIBILITY                               |

| HEX           | <b>A4</b>                | А3 | <b>A2</b> | <b>A</b> 1 | A0 |                                                                     |

| 00            | 0                        | 0  | 0         | 0          | 0  | Interrupt Mask Register (RD/WR)                                     |

| 01            | 0                        | 0  | 0         | 0          | 1  | Configuration Register #1 (RD/WR)                                   |

| 02            | 0                        | 0  | 0         | 1          | 0  | Configuration Register #2 (RD/WR)                                   |

| 03            | 0                        | 0  | 0         | 1          | 1  | Start/Reset Register (WR)                                           |

| 03            | 0                        | 0  | 0         | 1          | 1  | BC/RT Command Stack Pointer Register (RD)                           |

| 04            | 0                        | 0  | 1         | 0          | 0  | BC Control Word*/RT Subaddress Control Word Register (RD/WR)        |

| 05            | 0                        | 0  | 1         | 0          | 1  | Time Tag Register (RD/WR)                                           |

| 06            | 0                        | 0  | 1         | 1          | 0  | Interrupt Status Register (RD)                                      |

| 07            | 0                        | 0  | 1         | 1          | 1  | Configuration Register #3 (RD/WR)                                   |

| 08            | 0                        | 1  | 0         | 0          | 0  | Configuration Register #4 (RD/WR)                                   |

| 09            | 0                        | 1  | 0         | 0          | 1  | Configuration Register #5 (RD/WR)                                   |

| 0A            | 0                        | 1  | 0         | 1          | 0  | Data Stack Address Register (RD)*                                   |

| 0B            | 0                        | 1  | 0         | 1          | 1  | BC Frame Time Remaining Register (RD)*                              |

| 0C            | 0                        | 1  | 1         | 0          | 0  | BC Time Remaining to Next Message<br>Register (RD)*                 |

| 0D            | 0                        | 1  | 1         | 0          | 1  | BC Frame Time*/RT Last Command/MT<br>Trigger Word* Register (RD/WR) |

| 0E            | 0                        | 1  | 1         | 1          | 0  | RT Status Word Register (RD)                                        |

| 0F            | 0                        | 1  | 1         | 1          | 1  | RT BIT Word Register (RD)                                           |

| 10            | 1                        | 0  | 0         | 0          | 0  | Test Mode Register 0                                                |

| •             |                          |    |           |            |    |                                                                     |

| •             |                          |    |           |            |    |                                                                     |

| 17            | 1                        | 0  | 1         | 1          | 1  | Test Mode Register 7                                                |

| 18            | 1                        | 1  | 0         | 0          | 0  | reserved                                                            |

| •             |                          |    |           |            |    |                                                                     |

| •             |                          |    |           |            |    |                                                                     |

| 1F            | 1                        | 1  | 1         | 1          | 1  | reserved                                                            |

<sup>\*</sup> Not applicable to BU-65170/61571

| TABLE   | 3. INTERRUPT MASK REGISTER (READ/WRITE 00h)    |

|---------|------------------------------------------------|

| BIT     | DESCRIPTION                                    |

| 15(MSB) | RESERVED                                       |

| 14      | RAM PARITY ERROR                               |

| 13      | BC/RT TRANSMITTER TIMEOUT                      |

| 12      | BC/RT COMMAND STACK ROLLOVER                   |

| 11      | MT COMMAND STACK ROLLOVER                      |

| 10      | MT DATA STACK ROLLOVER                         |

| 9       | HS FAIL                                        |

| 8       | BC RETRY                                       |

| 7       | RT ADDRESS PARITY ERROR                        |

| 6       | TIME TAG ROLLOVER                              |

| 5       | RT CIRCULAR BUFFER ROLLOVER                    |

| 4       | BC CONTROL WORD/RT SUBADDRESS CONTROL WORD EOM |

| 3       | BC END OF FRAME                                |

| 2       | FORMAT ERROR                                   |

| 1       | BC STATUS SET/RT MODE CODE/MT PATTERN TRIGGER  |

| 0(LSB)  | END OF MESSAGE                                 |

| TABLE   | TABLE 5. CONFIGURATION REGISTER #2 (READ/WRITE 02h) |  |  |  |

|---------|-----------------------------------------------------|--|--|--|

| BIT     | DESCRIPTION                                         |  |  |  |

| 15(MSB) | ENHANCED INTERRUPTS                                 |  |  |  |

| 14      | RAM PARITY ENABLE (BU-61585/6 AND BU-65621 ONLY)    |  |  |  |

| 13      | BUSY LOOKUP TABLE ENABLE                            |  |  |  |

| 12      | RX SA DOUBLE BUFFER ENABLE                          |  |  |  |

| 11      | OVERWRITE INVALID DATA                              |  |  |  |

| 10      | 256-WORD BOUNDARY DISABLE                           |  |  |  |

| 9       | TIME TAG RESOLUTION 2(TTR2)                         |  |  |  |

| 8       | TIME TAG RESOLUTION 1 (TTR1)                        |  |  |  |

| 7       | TIME TAG RESOLUTION 0 (TTR0)                        |  |  |  |

| 6       | CLEAR TIME TAG ON SYNCHRONIZE                       |  |  |  |

| 5       | LOAD TIME TAG ON SYNCHRONIZE                        |  |  |  |

| 4       | INTERRUPT STATUS AUTO CLEAR                         |  |  |  |

| 3       | LEVEL/PULSE INTERRUPT REQUEST                       |  |  |  |

| 2       | CLEAR SERVICE REQUEST                               |  |  |  |

| 1       | ENHANCED RT MEMORY MANAGEMENT                       |  |  |  |

| 0(LSB)  | SEPARATE BROADCAST DATA                             |  |  |  |

|          | TABLE 4. CONFIGURATION REGISTER #1 (READ/WRITE 01H) |                                                          |                                             |                                                 |  |  |

|----------|-----------------------------------------------------|----------------------------------------------------------|---------------------------------------------|-------------------------------------------------|--|--|

| BIT      | BC FUNCTION (Bits<br>11-0 Enhanced Mode Only)       | RT WITHOUT ALTERNATE<br>STATUS                           | RT WITH ALTERNATE<br>STATUS (Enhanced Only) | MONITOR FUNCTION (Enhanced mode only bits 12-0) |  |  |

| 15 (MSB) | RT/BC-MT (logic 0)                                  | (logic 1)                                                | (logic 1)                                   | (logic 0)                                       |  |  |

| 14       | MT/BC-RT (logic 0)                                  | (logic 0)                                                | (logic 0)                                   | (logic 1)                                       |  |  |

| 13       | CURRENT AREA B/Ā                                    | CURRENT AREA B/A                                         | CURRENT AREA A/B                            | CURRENT AREA B/A                                |  |  |

| 12       | MESSAGE STOP-ON-ERROR                               | MESSAGE MONITOR ENABLED (MMT)                            | MESSAGE MONITOR<br>ENABLED (MMT)            | MESSAGE MONITOR ENABLED (MMT)                   |  |  |

| 11       | FRAME STOP-ON-ERROR                                 | DYNAMIC BUS CONTROL<br>ACCEPTANCE                        | S10                                         | TRIGGER ENABLED WORD                            |  |  |

| 10       | STATUS SET STOP-ON-MESSAGE                          | BUSY                                                     | S09                                         | START-ON-TRIGGER                                |  |  |

| 9        | STATUS SET STOP-ON-FRAME                            | SERVICE REQUEST                                          | S08                                         | STOP-ON-TRIGGER                                 |  |  |

| 8        | FRAME AUTO-REPEAT                                   | SUBSYSTEM FLAG                                           | S07                                         | NOT USED                                        |  |  |

| 7        | EXTERNAL TRIGGER ENABLED                            | RTFLAG (Enhanced Mode Only)                              | S06                                         | EXTERNAL TRIGGER ENABLED                        |  |  |

| 6        | INTERNAL TRIGGER ENABLED                            | NOT USED                                                 | S05                                         | NOT USED                                        |  |  |

| 5        | INTERMESSAGE GAP TIMER<br>ENABLED                   | NOT USED                                                 | S04                                         | NOT USED                                        |  |  |

| 4        | RETRY ENABLED                                       | NOT USED                                                 | S03                                         | NOT USED                                        |  |  |

| 3        | DOUBLED/SINGLE RETRY                                | NOT USED                                                 | S02                                         | NOT USED                                        |  |  |

| 2        | BC ENABLED (Read Only)                              | NOT USED                                                 | S01                                         | MONITOR ENABLED(Read Only)                      |  |  |

| 1        | BC FRAME IN PROGRESS (Read Only)                    | NOT USED                                                 | S00                                         | MONITOR TRIGGERED<br>(Read Only)                |  |  |

| 0 (LSB)  | BC MESSAGE IN PROGRESS<br>(Read Only)               | RT MESSAGE IN PROGRESS<br>(Enhanced mode only,Read Only) | RT MESSAGE IN<br>PROGRESS (Read Only)       | MONITOR ACTIVE<br>(Read Only)                   |  |  |

| 1       | ABLE 6. START/RESET REGISTER (WRITE 03H) |

|---------|------------------------------------------|

| BIT     | DESCRIPTION                              |

| 15(MSB) | RESERVED                                 |

| •       | •                                        |

| •       | •                                        |

| •       | •                                        |

| 7       | RESERVED                                 |

| 6       | BC/MT STOP-ON-MESSAGE                    |

| 5       | BC STOP-ON-FRAME                         |

| 4       | TIME TAG TEST CLOCK                      |

| 3       | TIME TAG RESET                           |

| 2       | INTERRUPT RESET                          |

| 1       | BC/MT START                              |

| 0(LSB)  | RESET                                    |

| TABLE 7 | TABLE 7. BC/RT COMMAND STACK POINTER REG. (READ 03H) |  |  |  |

|---------|------------------------------------------------------|--|--|--|

| BIT     | DESCRIPTION                                          |  |  |  |

| 15(MSB) | COMMAND STACK POINTER 15                             |  |  |  |

| •       | •                                                    |  |  |  |

| •       | •                                                    |  |  |  |

| •       | •                                                    |  |  |  |

| 0(LSB)  | COMMAND STACK POINTER 0                              |  |  |  |

|         | TABLE 8. BC CONTROL WORD REGISTER<br>READ/WRITE 04H, (BU-61580 ONLY) |

|---------|----------------------------------------------------------------------|

| BIT     | DESCRIPTION                                                          |

| 15(MSB) | RESERVED                                                             |

| 14      | M.E. MASK                                                            |

| 13      | SERVICE REQUEST BIT MASK                                             |

| 12      | SUBSYS BUSY BIT MASK                                                 |

| 11      | SUBSYS FLAG BIT MASK                                                 |

| 10      | TERMINAL FLAG BIT MASK                                               |

| 9       | RESERVED BITS MASK                                                   |

| 8       | RETRY ENABLED                                                        |

| 7       | BUS CHANNEL A/B                                                      |

| 6       | OFF LINE SELF TEST                                                   |

| 5       | MASK BROADCAST BIT                                                   |

| 4       | EOM INTERRUPT ENABLE                                                 |

| 3       | 1553A/B SELECT                                                       |

| 2       | MODE CODE FORMAT                                                     |

| 1       | BROADCAST FORMAT                                                     |

| 0(LSB)  | RT-RT FORMAT                                                         |

|         | TABLE 9. RT SUBADDRESS CONTROL WORD (READ/WRITE 04H) |

|---------|------------------------------------------------------|

| BIT     | DESCRIPTION                                          |

| 15(MSB) | RX: DOUBLE BUFFER ENABLE                             |

| 14      | TX: EOM INT                                          |

| 13      | TX: CIRC BUF INT                                     |

| 12      | TX: MEMORY MANAGEMENT 2 (MM2)                        |

| 11      | TX: MEMORY MANAGEMENT 1 (MM1)                        |

| 10      | TX: MEMORY MANAGEMENT 0 (MM0)                        |

| 9       | RX: EOM INT                                          |

| 8       | RX: CIRC BUF INT                                     |

| 7       | RX: MEMORY MANAGEMENT 2 (MM2)                        |

| 6       | RX: MEMORY MANAGEMENT 1 (MM1)                        |

| 5       | RX: MEMORY MANAGEMENT 0 (MM0)                        |

| 4       | BCST: EOM INT                                        |

| 3       | BCST: CIRC BUF INT                                   |

| 2       | BCST:MEMORY MANAGEMENT 2 (MM2)                       |

| 1       | BCST: MEMORY MANAGEMENT 1 (MM1)                      |

| 0(LSB)  | BCST: MEMORY MANAGEMENT 0 (MM0)                      |

| TABLE 10. TIME TAG REGISTER (READ/WRITE 05H) |             |

|----------------------------------------------|-------------|

| BIT                                          | DESCRIPTION |

| 15(MSB)                                      | TIME TAG 15 |

| •                                            | •           |

| •                                            | •           |

| •                                            | •           |

| 0(LSB)                                       | TIME TAG 0  |

| TABLE 11. INTERRUPT STATUS REGISTER (READ 06H) |                                                  |

|------------------------------------------------|--------------------------------------------------|

| BIT                                            | DESCRIPTION                                      |

| 15(MSB)                                        | MASTER INTERRUPT                                 |

| 14                                             | RAM PARITY ERROR                                 |

| 13                                             | BC/RT TRANSMITTER TIMEOUT                        |

| 12                                             | BC/RT COMMAND STACK ROLLOVER                     |

| 11                                             | MT COMMAND STACK ROLLOVER                        |

| 10                                             | MT DATA STACK ROLLOVER                           |

| 9                                              | HS FAIL                                          |

| 8                                              | BC RETRY                                         |

| 7                                              | RT ADDRESS PARITY ERROR                          |

| 6                                              | TIME TAG ROLLOVER                                |

| 5                                              | RT CIRCULAR BUFFER ROLLOVER                      |

| 4                                              | BC CONTROL WORD/RT SUBADDRESS CONTROL WORD EOM   |

| 3                                              | BC END OF FRAME                                  |

| 2                                              | FORMAT ERROR                                     |

| 1                                              | BC STATUS SET/RT MODE CODE/MT PATTERN<br>TRIGGER |

| 0(LSB)                                         | END OF MESSAGE                                   |

| TABLE 12. CONFIGURATION REGISTER #3 (READ/WRITE 07H) |                              |

|------------------------------------------------------|------------------------------|

| BIT                                                  | DESCRIPTION                  |

| 15(MSB)                                              | ENHANCED MODE ENABLE         |

| 14                                                   | BC/RT COMMAND STACK SIZE 1   |

| 13                                                   | BC/RT COMMAND STACK SIZE 0   |

| 12                                                   | MT COMMAND STACK SIZE 1      |

| 11                                                   | MT COMMAND STACK SIZE 0      |

| 10                                                   | MT DATA STACK SIZE 2         |

| 9                                                    | MT DATA STACK SIZE 1         |

| 8                                                    | MT DATA STACK SIZE 0         |

| 7                                                    | ILLEGALIZATION DISABLED      |

| 6                                                    | OVERRIDE MODE T/R ERROR      |

| 5                                                    | ALTERNATE STATUS WORD ENABLE |

| 4                                                    | ILLEGAL RX TRANSFER DISABLE  |

| 3                                                    | BUSY RX TRANSFER DISABLE     |

| 2                                                    | RTFAIL-FLAG WRAP ENABLE      |

| 1                                                    | 1553A MODE CODES ENABLE      |

| 0(LSB)                                               | ENHANCED MODE CODE HANDLING  |

| TABLE 13. CONFIGURATION REGISTER #4 (READ/WRITE 08H) |                                 |

|------------------------------------------------------|---------------------------------|

| BIT                                                  | DESCRIPTION                     |

| 15(MSB)                                              | EXTERNAL BIT WORD ENABLE        |

| 14                                                   | INHIBIT BIT WORD IF BUSY        |

| 13                                                   | MODE COMMAND OVERRIDE BUSY      |

| 12                                                   | EXPANDED BC CONTROL WORD ENABLE |

| 11                                                   | BROADCAST MASK ENABLE/XOR       |

| 10                                                   | RETRY IF -A AND M.E.            |

| 9                                                    | RETRY IF STATUS SET             |

| 8                                                    | 1ST RETRY ALT/SAME BUS          |

| 7                                                    | 2ND RETRY ALT/SAME BUS          |

| 6                                                    | VALID M.E./NO DATA              |

| 5                                                    | VALID BUSY/NO DATA              |

| 4                                                    | MT TAG GAP OPTION               |

| 3                                                    | LATCH RT ADRRESS WITH CONFIG #5 |

| 2                                                    | TEST MODE 2                     |

| 1                                                    | TEST MODE 1                     |

| 0(LSB)                                               | TEST MODE 0                     |

| TABLE 14. CONFIGURATION REGISTER #5 (READ/WRITE 09H) |                                                   |

|------------------------------------------------------|---------------------------------------------------|

| BIT                                                  | DESCRIPTION                                       |

| 15(MSB)                                              | 12MHZ CLOCK SELECT                                |

| 14                                                   | LOGIC "0"                                         |

| 13                                                   | EXTERNAL TX INHIBIT A, read only BU-65170/61580X6 |

| 12                                                   | EXTERNAL TX INHIBIT B, read only BU-65170/61580X6 |

| 11                                                   | EXPANDED CROSSING ENABLED                         |

| 10                                                   | RESPONSE TIMEOUT SELECT 1                         |

| 9                                                    | RESPONSE TIMEOUT SELECT 0                         |

| 8                                                    | GAP CHECK ENABLED                                 |

| 7                                                    | BROADCAST DISABLED                                |

| 6                                                    | RT ADDRESS LATCH/TRANSPARENT (see NOTE)           |

| 5                                                    | RT ADDRESS 4                                      |

| 4                                                    | RT ADDRESS 3                                      |

| 3                                                    | RT ADDRESS 2                                      |

| 2                                                    | RT ADDRESS 1                                      |

| 1                                                    | RT ADDRESS 0                                      |

| 0(LSB)                                               | RT ADDRESS PARITY                                 |

Notes for TABLE 14: Read only, logic "0" for 65170/61580, logic "1" for 65171/61581/61586.

| TABLE 15. MONITOR DATA STACK ADDRESS REGISTER (READ/WRITE 0AH) |                               |

|----------------------------------------------------------------|-------------------------------|

| BIT                                                            | DESCRIPTION                   |

| 15(MSB)                                                        | MONITOR DATA STACK ADDRESS 15 |

| •                                                              | •                             |

| •                                                              | •                             |

| •                                                              | •                             |

| 0(LSB)                                                         | MONITOR DATA STACK ADDRESS 0  |

| TABLE 16. BC FRAME TIME REMAINING REGISTER (READ/WRITE 0BH) |                            |

|-------------------------------------------------------------|----------------------------|

| BIT                                                         | DESCRIPTION                |

| 15(MSB)                                                     | BC FRAME TIME REMAINING 15 |

| •                                                           | •                          |

| •                                                           | •                          |

| •                                                           | •                          |

| 0(LSB)                                                      | BC FRAME TIME REMAINING 0  |

Note: resolution = 1 μs per LSB

| TABLE 17. BC MESSAGE TIME REMAINING REGISTER (READ/WRITE 0CH) |                              |

|---------------------------------------------------------------|------------------------------|

| BIT                                                           | DESCRIPTION                  |

| 15(MSB)                                                       | BC MESSAGE TIME REMAINING 15 |

| •                                                             | •                            |

| •                                                             | •                            |

| •                                                             | •                            |

| 0(LSB)                                                        | BC MESSAGE TIME REMAINING 0  |

Note: resolution = 1  $\mu$ s per LSB

| TABLE 18. BC FRAME TIME/RT LAST COMMAND/T TRIGGER REGISTER (READ/WRITE 0DH) |             |

|-----------------------------------------------------------------------------|-------------|

| BIT                                                                         | DESCRIPTION |

| 15(MSB)                                                                     | BIT 15      |

| •                                                                           | •           |

| •                                                                           | •           |

| •                                                                           | •           |

| 0(LSB)                                                                      | BIT 0       |

| TABLE   | TABLE 19. RT STATUS WORD REGISTER (READ/WRITE 0EH) |  |

|---------|----------------------------------------------------|--|

| BIT     | DESCRIPTION                                        |  |

| 15(MSB) | LOGIC "0"                                          |  |

| 14      | LOGIC "0"                                          |  |

| 13      | LOGIC "0"                                          |  |

| 12      | LOGIC "0"                                          |  |

| 11      | LOGIC "0"                                          |  |

| 10      | MESSAGE ERROR                                      |  |

| 9       | INSTRUMENTATION                                    |  |

| 8       | SERVICE REQUEST                                    |  |

| 7       | RESERVED                                           |  |

| 6       | RESERVED                                           |  |

| 5       | RESERVED                                           |  |

| 4       | BROADCAST COMMAND RECEIVED                         |  |

| 3       | BUSY                                               |  |

| 2       | SUBSYSTEM FLAG                                     |  |

| 1       | DYNAMIC BUS CONTROL ACCEPT                         |  |

| 0(LSB)  | TERMINAL FLAG                                      |  |

| TABLE 20. RT BIT WORD REGISTER (READ 0FH) |                                  |

|-------------------------------------------|----------------------------------|

| BIT                                       | DESCRIPTION                      |

| 15(MSB)                                   | TRANSMITTER TIMEOUT              |

| 14                                        | LOOP TEST FAILURE B              |

| 13                                        | LOOP TEST FAILURE A              |

| 12                                        | HANDSHAKE FAILURE                |

| 11                                        | TRANSMITTER SHUTDOWN B           |

| 10                                        | TRANSMITTER SHUTDOWN A           |

| 9                                         | TERMINAL FLAG INHIBITED          |

| 8                                         | CHANNEL B/Ā                      |

| 7                                         | HIGH WORD COUNT                  |

| 6                                         | LOW WORD COUNT                   |

| 5                                         | INCORRECT SYNC RECEIVED          |

| 4                                         | PARITY/MANCHESTER ERROR RECEIVED |

| 3                                         | RT-RT GAP/SYNCH/ADDRESS ERROR    |

| 2                                         | RT-RT NO RESPONSE ERROR          |

| 1                                         | RT-RT 2ND COMMAND WORD ERROR     |

| 0(LSB)                                    | COMMAND WORD CONTENTS ERROR      |

# NOTE: TABLES 21 TO 24 ARE NOT REGISTERS, BUT THEY ARE WORDS STORED IN RAM.

| TABLE 21. BC MODE BLOCK STATUS WORD |                             |

|-------------------------------------|-----------------------------|

| BIT                                 | DESCRIPTION                 |

| 15(MSB)                             | EOM                         |

| 14                                  | SOM                         |

| 13                                  | CHANNEL B/Ā                 |

| 12                                  | ERROR FLAG                  |

| 11                                  | STATUS SET                  |

| 10                                  | FORMAT ERROR                |

| 9                                   | NO RESPONSE TIMEOUT         |

| 8                                   | LOOP TEST FAIL              |

| 7                                   | MASKED STATUS SET           |

| 6                                   | RETRY COUNT 1               |

| 5                                   | RETRY COUNT 0               |

| 4                                   | GOOD DATA BLOCK TRANSFER    |

| 3                                   | WRONG STATUS ADDRESS/NO GAP |

| 2                                   | WORD COUNT ERROR            |

| 1                                   | INCORRECT SYNC TYPE         |

| 0(LSB)                              | INVALID WORD                |

| TABLE 22. RT MODE BLOCK STATUS WORD |                              |

|-------------------------------------|------------------------------|

| BIT                                 | DESCRIPTION                  |

| 15(MSB)                             | EOM                          |

| 14                                  | SOM                          |

| 13                                  | CHANNEL B/A                  |