Enhanced Miniature Advanced Communications Engine (Enhanced Mini-ACE<sup>®</sup> Series) Users Guide MN-6186X-001 Volume 1 - Architectural Reference

The information provided in this User's Guide is believed to be accurate; however, no responsibility is assumed by Data Device Corporation for its use, and no license or rights are granted by implication or otherwise in connection therewith.

Specifications are subject to change without notice. Please visit our Web site at **www.ddc-web.com** for the latest information

105 Wilbur Place, Bohemia, New York 11716-2426 For Technical Support – 1-800-DDC-5757 ext. 7771 Headquarters - Tel: (631) 567-5600, Fax: (631) 567-7358 United Kingdom - Tel: +44-(0)1635-811140, Fax: +44-(0)1635-32264 France - Tel: +33-(0)1-41-16-3424, Fax: +33-(0)1-41-16-3425 Germany - Tel: +49-(0)89-150012-11, Fax: +49-(0)89-150012-12 Japan - Tel: +81-(0)3-3814-7688, Fax: +81-(0)3-3814-7689 Asia - Tel: +65-6489-4801 India - Tel: +91 80 30110474 World Wide Web - <u>http://www.ddc-web.com</u>

All rights reserved. No part of this User's Guide may be reproduced or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of Data Device Corporation.

Rev R - February, 2018 © 2000, 2005 Data Device Corp.

## **RECORD OF CHANGE**

| Revision | Date    | Pages        | Description                                 |

|----------|---------|--------------|---------------------------------------------|

| A        | 3/2003  | All          | Reformatted                                 |

| В        | 8/2004  | All          | Major Revision, See MarCom for Markup       |

| С        | 8/2005  | All          | Major Revision                              |

| D        | 1/2007  | All          | Major Revision                              |

|          | 6/2007  | 255          | Added note and warning under Figure 19      |

| E        | 7/2007  | 127          | Change in Table 86                          |

| F        | 12/2007 | 222, various | Added double buffering support note,        |

|          |         |              | modified Tables 61 and 155, misc            |

|          |         |              | typographical edits.                        |

| G        | 2/2008  | Various      | Removed tables 1 and 2, edited former table |

|          |         |              | 4, renumbered all tables.                   |

| H        | 5/2008  | 180          | Changed minor typo                          |

| J        | 8/2008  | 13, 34, 68   | Edits to tables 6 and 40. Changed note on   |

|          |         |              | page 68.                                    |

| K        | 1/2009  | Various      | Addition of the Total-ACE product line      |

| L        | 5/2009  | 85, 114      | Edit to Table 69 and Table 85               |

| M        | 4/2010  | 94, 96       | Edits to Table 75 and corresponding Equal   |

|          |         |              | and Less Than Flag descriptions on page 96, |

|          |         |              | edits to Table 111                          |

| N        | 2/2012  | 101, 290     | Update to section 4.31 and 6.45             |

| Р        | 11/2012 | 290, 313     | Changed "0x8B90" to "0X8B80" on page 290.   |

|          |         |              | Removed redundant RT_AD_LAT text on         |

|          |         |              | page 313.                                   |

| R        | 2/2018  | 44           | Updated "Important Note" section.           |

|          |         |              |                                             |

|          |         |              |                                             |

## TABLE OF CONTENTS (VOLUME 1)

| 1 | Р      | REFACE                                                                   | XIII |

|---|--------|--------------------------------------------------------------------------|------|

|   |        | xt Usage                                                                 |      |

|   | 1.2 Sp | ecial Handling and Cautions                                              | xiii |

|   | 1.3 Tr | ademarks                                                                 | xiii |

| _ |        |                                                                          |      |

| 2 |        |                                                                          |      |

|   | 2.1 De | evice Specifications                                                     | 4    |

| 3 | F      | JNCTIONAL OVERVIEW                                                       |      |

| Ŭ |        | ansceivers                                                               |      |

|   |        |                                                                          |      |

| 4 |        | EGISTERS                                                                 |      |

|   |        | wer Turn-On / Initialization State                                       |      |

|   |        | /erall Address Mapping: Words vs. Bytes                                  |      |

|   | 4.3 Sc | oftware Interface: Internal RAM and Registers                            |      |

|   |        | ernal Registers Address and Bit Mapping                                  |      |

|   | 4.5 Re | egister Function Summary                                                 | 24   |

|   | 4.6 Re | egister Bit Maps and Bit Descriptions                                    | 27   |

|   | 4.7 In | errupt Mask Register #1                                                  | 27   |

|   | 4.8 Co | onfiguration Register #1                                                 |      |

|   | 4.9 Co | onfiguration Register #2                                                 |      |

|   | 4.10   | Start/Reset Register                                                     |      |

|   | 4.11   | Command Stack Pointer Register/Enhanced BC Instruction List Register     |      |

|   | 4.12   | BC Control Word/RT Subaddress Control Word Register                      | 52   |

|   | 4.13   | Time Tag Register                                                        | 53   |

|   | 4.14   | Interrupt Status Register #1                                             | 55   |

|   | 4.15   | Configuration Register #3                                                | 62   |

|   | 4.16   | Configuration Register #4                                                | 70   |

|   | 4.17   | Configuration Register #5                                                |      |

|   | 4.18   | RT/Monitor Data Stack Address                                            | 80   |

|   | 4.19   | BC Frame Time Remaining                                                  | 81   |

|   | 4.20   | BC Message Time Remaining                                                | 81   |

|   | 4.21   | Non-Enhanced BC Frame Time/Enhanced BC Initial Instruction Pointer/RT La |      |

|   |        | igger Register                                                           |      |

|   | 4.22   | RT Status Word Register                                                  |      |

|   | 4.23   | RT Bit Word Register                                                     |      |

|   | 4.24   | Block Status Word                                                        |      |

|   | 4.25   | Configuration Register #6                                                |      |

|   | 4.26   | Configuration Register #7                                                |      |

|   | 4.27   | BC Condition Code Register                                               |      |

|   | 4.28   | BC General Purpose Flag Register                                         |      |

|   | 4.29   | Bit Test Status Register                                                 |      |

#### TABLE OF CONTENTS

|   | 4.30    | Inter       | rupt Mask Register #2                                                            | 100    |

|---|---------|-------------|----------------------------------------------------------------------------------|--------|

|   | 4.31    | Inter       | rupt Status Register #2                                                          | 101    |

|   | 4.32    | BC (<br>105 | General Purpose Queue Pointer Register/RT, MT Interrupt Status Queue Pointer Re  | gister |

| 5 | B       | C OF        | PERATION                                                                         | 106    |

|   | 5.1 De  | efinitio    | ns                                                                               | 106    |

|   | 5.2 Int | roduc       | tion                                                                             | 106    |

|   | 5.3 Le  | gacy        | BC Mode                                                                          | 107    |

|   | 5.4 BC  | C Men       | nory Organization                                                                | 107    |

|   | 5.5 25  | 6-Wo        | rd Boundaries                                                                    | 109    |

|   | 5.5     | .1          | ACTIVE AREAS DOUBLE BUFFERING                                                    | 109    |

|   | 5.6 Pr  | ogran       | nming BC Message Frames                                                          | 110    |

|   | 5.6     | .1          | BC MEMORY MANAGEMENT                                                             | 110    |

|   | 5.6     | .2          | MESSAGE BLOCK FORMATS                                                            | 114    |

|   | 5.6     | .3          | BC CONTROL WORD                                                                  | 119    |

|   | 5.6     | .4          | DESCRIPTOR STACK                                                                 | 125    |

|   | 5.6     | .5          | BC TIME-TO-NEXT MESSAGE TIME                                                     | 131    |

|   | 5.6     | .6          | BC FRAME AUTO-REPEAT                                                             | 132    |

|   | 5.6     | .7          | MINOR AND MAJOR FRAMES                                                           | 133    |

|   | 5.6     | .8          | BC START SEQUENCE AND OPTIONS                                                    | 134    |

|   | 5.6     | .9          | BC INTERRUPTS                                                                    | 136    |

|   | 5.7 Ot  | her B       | C Functions                                                                      |        |

|   | 5.7     | .1          | AUTOMATIC RETRIES                                                                |        |

|   | 5.7     | .2          | BC RESPONSE TIMEOUT                                                              |        |

|   | 5.7     | .3          | BC STATUS WORD MASKING                                                           |        |

|   | 5.7     | .4          | LEGACY BC SOFTWARE INITIALIZATION SEQUENCE                                       |        |

|   | 5.7     | .5          | LEGACY BC PSEUDO CODE EXAMPLE                                                    | 146    |

|   | 5.7     | .6          | PSEUDO CODE                                                                      |        |

|   | 5.7     | .7          | SERVICING IN-PROGRESS OR COMPLETED BC FRAMES                                     |        |

|   | 5.7     | .8          | TERMINATING OF BC FRAMES                                                         | 151    |

|   | 5.7     | .9          | BUS CONTROLLER START-OF-MESSAGE, END-OF-MESSAGE, AND RETRY<br>TRANSFER SEQUENCES | 152    |

|   | 5.7     | .10         | BC START-OF-MESSAGE (SOM) SEQUENCE                                               | 152    |

|   | 5.7     | .11         | BC END-OF-MESSAGE (EOM) SEQUENCE                                                 | 153    |

|   | 5.7     | .12         | BC MESSAGE RETRY SEQUENCE                                                        | 153    |

|   | 5.7     | .13         | BC EXCEPTION CONDITIONS                                                          | 153    |

|   | 5.7     | .14         | BC OFF-LINE AND ON-LINE SELF-TESTS                                               | 157    |

|   | 5.8 Er  | hance       | ed BC Mode Architecture                                                          | 159    |

|   | 5.8     | .1          | INTRODUCTION                                                                     | 159    |

|   | 5.8     | .2          | ENHANCED BC MODE: MESSAGE SEQUENCE CONTROL                                       | 160    |

|   | 5.8     | .3          | BC INSTRUCTION SET                                                               | 161    |

|   | 5.8     | .4          | EXECUTE AND FLIP OPERATION                                                       | 164    |

|   | 5.8     | .5          | BC MESSAGE SEQUENCE CONTROL                                                      | 173    |

|   | 5.8     | .6          | GENERAL PURPOSE QUEUE                                                            | 173    |

|   | 5.9 Ap  | plication Examples of the Enhanced BC Mode                              | 174 |

|---|---------|-------------------------------------------------------------------------|-----|

|   | 5.9     | 1 MINOR AND MAJOR FRAMES                                                | 174 |

|   | 5.9     | 2 ASYNCHRONOUS MESSAGE FRAME INSERTION                                  | 178 |

|   | 5.9     | 3 DATA BLOCK DOUBLE BUFFERING                                           | 179 |

|   | 5.9     | 4 DATA LOGGING USING THE GENERAL PURPOSE QUEUE                          | 188 |

|   | 5.9     | 5 USE OF EXTERNAL TRIGGER                                               | 188 |

|   |         |                                                                         |     |

| 6 | R       | Γ OPERATION                                                             | 189 |

|   |         | roduction                                                               |     |

|   |         | Memory Organization                                                     |     |

|   | 6.3 RT  | Memory Management                                                       | 194 |

|   |         | baddress Control Word                                                   |     |

|   | 6.5 Sir | ngle Message Mode                                                       | 200 |

|   | 6.6 25  | 6-Word Boundaries                                                       | 201 |

|   |         | Subaddress Double Buffering Mode                                        |     |

|   | 6.8 Ci  | cular Buffer Mode                                                       | 204 |

|   | 6.9 Gl  | obal Circular Buffer                                                    | 206 |

|   | 6.10    | RT Descriptor Stack                                                     | 207 |

|   | 6.11    | RT Interrupts                                                           | 207 |

|   | 6.12    | RT Block Status Word                                                    | 209 |

|   | 6.13    | Bits that can be set with Enhanced Mode Only                            | 211 |

|   | 6.14    | Time Tag Word                                                           | 212 |

|   | 6.15    | Data Block Pointer or Mode Code Data Word                               | 213 |

|   | 6.16    | Command Word Received                                                   | 213 |

|   | 6.17    | Superceding Commands                                                    | 213 |

|   | 6.18    | RT Interrupts                                                           | 214 |

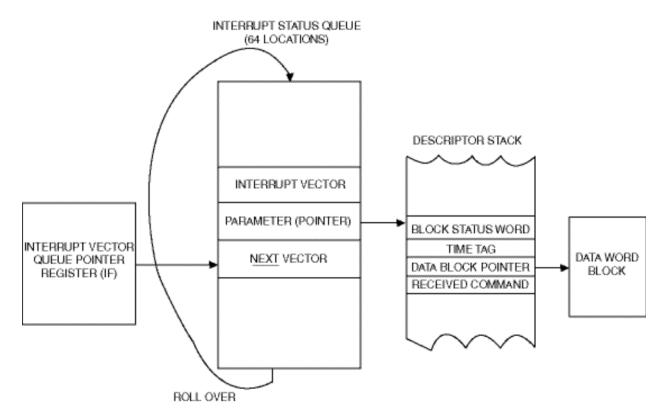

|   | 6.19    | Interrupt Status Queue                                                  | 215 |

|   | 6.20    | Implementing Bulk Data Transfers                                        | 221 |

|   | 6.21    | RT Command Illegalization                                               |     |

|   | 6.22    | Effects of Illegalization                                               | 222 |

|   | 6.23    | Illegalization RAM Memory Map                                           | 223 |

|   | 6.2     | -                                                                       |     |

|   | 6.24    | Accessing the Illegalization Table                                      | 227 |

|   | 6.25    | Enhanced Mode Code Handling                                             |     |

|   | 6.26    | Broadcast Option                                                        |     |

|   | 6.27    | Busy Bit (See Table 124 for Tabular Mapping of Conditions Listed Below) |     |

|   | 6.28    | Subaddress Busy Word                                                    |     |

|   | 6.29    | RT Address Inputs                                                       |     |

|   | 6.30    | RT Status Word                                                          |     |

|   | 6.31    | RT-to-RT Response Timeout                                               |     |

|   | 6.32    | RT Built-In-Test (Bit) Word                                             |     |

|   | 6.33    | RT Start-of-Message and End-of-Message Transfer Sequences               |     |

|   | 6.34    | RT Start-of-Message (SOM) Sequence                                      |     |

|   | 6.35    | RT End-of-Message (EOM) Sequence                                        |     |

|   | 0.00    | ···· =··· ····························                                  |     |

|   | 6.36    | Sum     | mary of RT Exception Conditions                                    | 253 |

|---|---------|---------|--------------------------------------------------------------------|-----|

|   | 6.37    | Sum     | mary of Responses to Mode Code Messages                            | 260 |

|   | 6.38    | Deta    | iled Functional Description of Mode Codes ("1553B" Implementation) | 261 |

|   | 6.3     | 8.1     | DYNAMIC BUS CONTROL (T/R* = 1; 00000)                              | 261 |

|   | 6.3     | 8.2     | SYNCHRONIZE WITHOUT DATA WORD (T/R* = 1; 00001)                    | 262 |

|   | 6.3     | 8.3     | TRANSMIT STATUS WORD (T/R* = 1; 00010)                             | 262 |

|   | 6.3     | 8.4     | INITIATE SELF-TEST (T/R* = 1; 00011)                               | 263 |

|   | 6.3     | 8.5     | TRANSMITTER SHUTDOWN (T/R* = 1; 00100)                             | 264 |

|   | 6.3     | 8.6     | OVERRIDE TRANSMITTER SHUTDOWN (T/R* = 1; 00101)                    | 264 |

|   | 6.3     | 8.7     | INHIBIT TERMINAL FLAG BIT (T/R* = 1; 00110)                        | 265 |

|   | 6.3     | 8.8     | OVERRIDE INHIBIT TERMINAL FLAG BIT (T/R* = 1; 00111)               | 265 |

|   | 6.3     | 8.9     | RESET REMOTE TERMINAL (T/R* = 1; 01000)                            | 266 |

|   | 6.3     | 8.10    | RESERVED MODE CODES (T/R*=1; 01001 - 01111)                        | 267 |

|   | 6.3     | 8.11    | TRANSMIT VECTOR WORD (T/R* = 1; 10000)                             | 267 |

|   | 6.3     | 8.12    | SYNCHRONIZE WITH DATA WORD (T/R* = 0; 10001)                       | 268 |

|   | 6.3     | 8.13    | TRANSMIT LAST COMMAND (T/R* = 1; 10010)                            | 269 |

|   | 6.39    | Tran    | smit BIT Word (T/R* = 1; 10011)                                    | 270 |

|   | 6.3     | 9.1     | SELECTED TRANSMITTER SHUTDOWN (T/R* = 0; 10100)                    | 271 |

|   | 6.3     | 9.2     | OVERRIDE SELECTED TRANSMITTER SHUTDOWN (T/R* = 0; 10101)           | 271 |

|   | 6.3     | 9.3     | RESERVED MODE CODES (T/R* = 0; 10110 - 11111)                      | 272 |

|   | 6.40    | RT S    | Software Initialization Procedure                                  | 273 |

|   | 6.41    | RT F    | Pseudo Code Example                                                | 278 |

|   | 6.42    | Pseu    | Ido Code                                                           |     |

|   | 6.43    | Serv    | icing Completed RT Messages                                        |     |

|   | 6.44    | RT E    | Fror Handling                                                      |     |

|   | 6.45    | RT A    | Nuto-Boot Option                                                   | 290 |

|   | 6.46    | Othe    | r RT Features                                                      | 290 |

|   |         |         |                                                                    |     |

| 7 |         |         | OR OPERATION                                                       |     |

|   |         |         | onitor Mode                                                        |     |

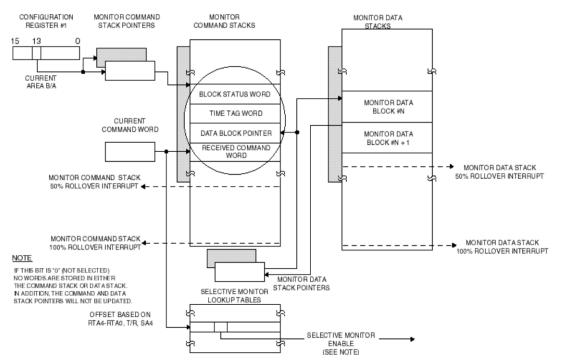

|   |         |         | onitor Memory Map                                                  |     |

|   | 7.3 W   | ord M   | onitor Initialization                                              |     |

|   | 7.3     | .1      | WORD MONITOR START AND STOP                                        |     |

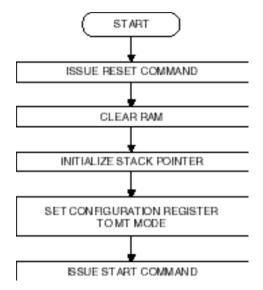

|   | 7.3     |         | WORD MONITOR SOFTWARE INITIALIZATION SEQUENCE                      |     |

|   |         | -       | ishing Command Words From Status Words : Message Reconstruction    |     |

|   |         |         | onitor Trigger                                                     |     |

|   | 7.6 Se  | electiv | e Message Monitor Mode                                             |     |

|   | 7.6     | .1      | MONITOR SELECTION FUNCTION                                         |     |

|   | 7.6     | .2      | MESSAGE MONITOR FORMATS                                            |     |

|   |         | 0       | e Monitor Block Status Word                                        |     |

|   | 7.8 Int | errupt  | Status Queue                                                       |     |

|   | 7.8     | .1      | MESSAGE INTERRUPT EVENT BIT DESCRIPTIONS                           |     |

|   | 7.9 Su  | iperce  | ding Commands                                                      | 314 |

|   | 7.10    | Sele    | ctive Message Monitor SOM and EOM Transfer Sequences               | 315 |

#### TABLE OF CONTENTS

|   | 7.10     | 0.1 MT START-OF-MESSAGE (SOM) SEQUENCE                               |  |

|---|----------|----------------------------------------------------------------------|--|

|   | 7.10     | 0.2 MT END-OF-MESSAGE (EOM) SEQUENCE                                 |  |

|   | 7.10     | 0.3 INITIALIZATION                                                   |  |

|   | 7.10     | 0.4 SERVICING TECHNIQUE                                              |  |

|   |          |                                                                      |  |

| 8 |          | IHANCED MINI-ACE BUILT-IN SELF-TEST                                  |  |

|   | 8.1 Intr | oduction                                                             |  |

|   | 8.2 Dif  | erences from ACE and Mini-ACE (Plus)                                 |  |

|   | 8.3 Pro  | tocol Logic Test                                                     |  |

|   | 8.4 RA   | M Self-Test                                                          |  |

|   | 8.5 Tes  | st Time                                                              |  |

|   | 8.6 Po   | wer-on Self-Test                                                     |  |

|   | 8.7 Re   | gister Bits                                                          |  |

|   | 8.8 Init | iating Self-Test                                                     |  |

|   | 8.9 Tei  | minating Self-Test                                                   |  |

|   | 8.10     | Determining BIT Test Completion and Results                          |  |

|   | 8.11     | BIT Test Status Register                                             |  |

|   | 8.12     | RT BIT Word                                                          |  |

|   | 8.13     | Terminal Flag Status Word bit                                        |  |

|   | 8.14     | Self-Test Registers                                                  |  |

|   | 8.15     | BC/RT Online Loop Test                                               |  |

|   | 8.16     | BC Offline Loop Test                                                 |  |

|   | 8.17     | Transmitter Watchdog (failsafe) Timer Test                           |  |

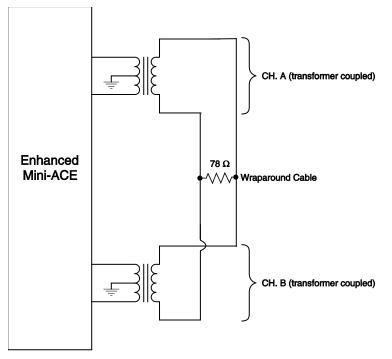

|   | 8.18     | Channel A-to-Channel B Wraparound Self-Test (BC/RT/MT Versions Only) |  |

|   |          |                                                                      |  |

## LIST OF FIGURES (VOLUME 1)

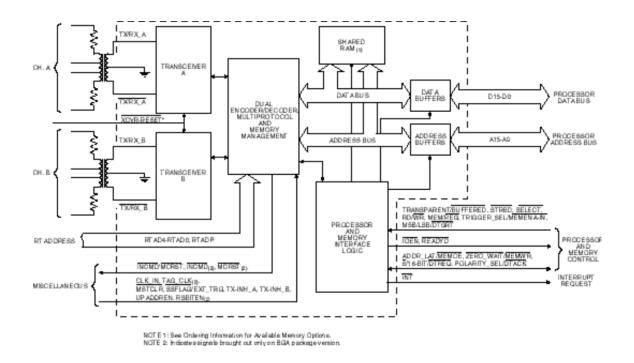

| Figure 1. Enhanced Mini-ACE / Micro-ACE Series Block Diagram                                      | 2         |

|---------------------------------------------------------------------------------------------------|-----------|

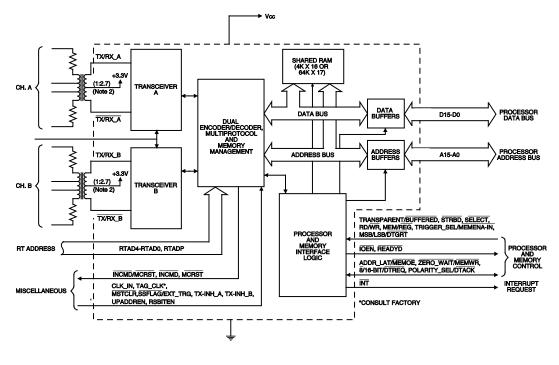

| Figure 2. Mini-ACE Mark3 and Micro-ACE-TE Series Block Diagram (Shown with +3.3V Transce          | eivers) 3 |

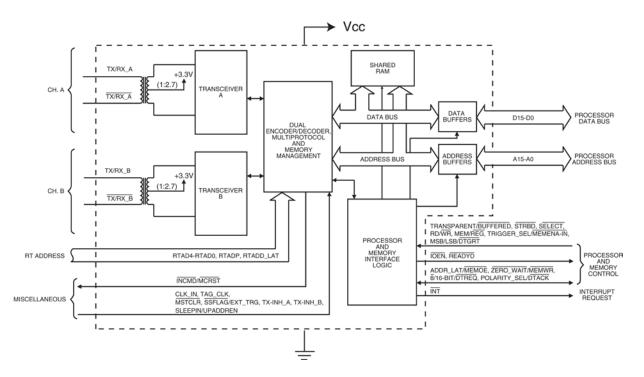

| Figure 3. Total-ACE Block Diagram                                                                 | 3         |

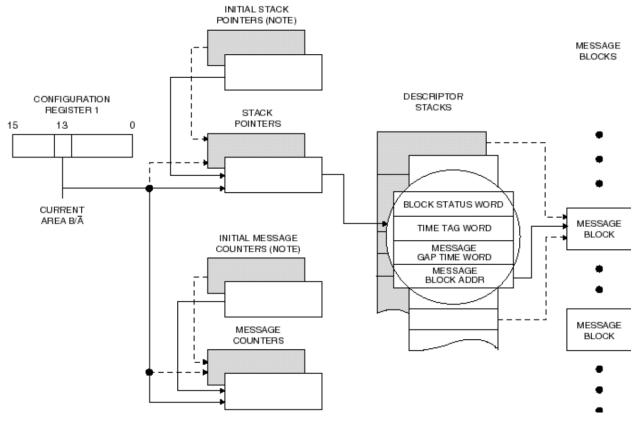

| Figure 4. Legacy BC Memory Management                                                             | 111       |

| Figure 5. BC Message Block Formats                                                                | 116       |

| Figure 6. BC Time-to-Next Message Time                                                            |           |

| Figure 7. BC Major And Minor Frames                                                               |           |

| Figure 8. Message Sequence For Legacy BC Pseudo Code Example                                      |           |

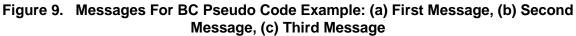

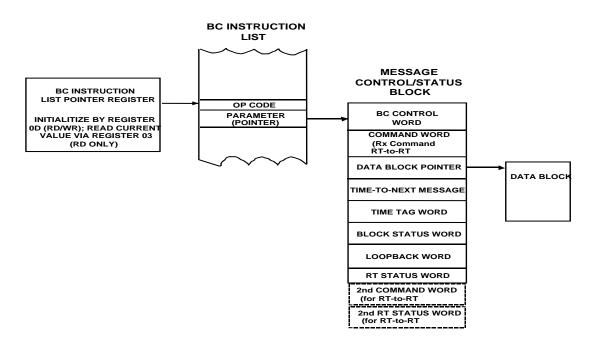

| Figure 9. Messages For BC Pseudo Code Example: (a) First Message, (b) Second Message, (c) Message |           |

| Figure 10. BC Message Sequence Control                                                            |           |

| Figure 11. BC Op Code Format                                                                      |           |

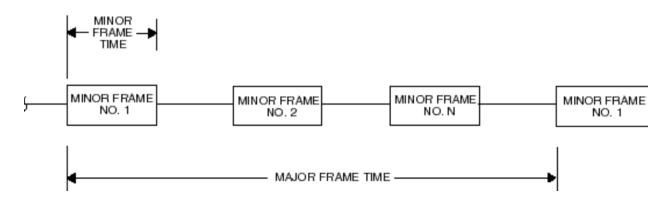

| Figure 12. Use of Execute and Flip (XQF) Operation                                                | 165       |

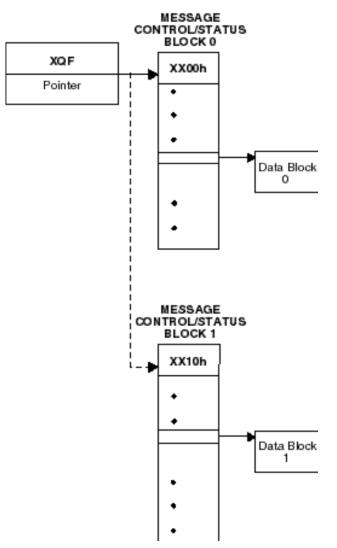

| Figure 13. BC General Purpose Queue                                                               | 173       |

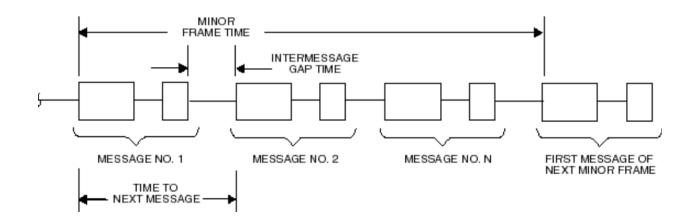

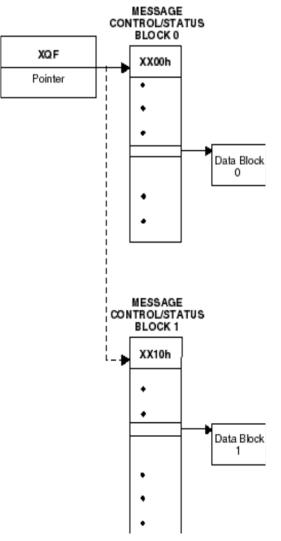

| Figure 14. Intermessage Gap Time, Minor Frame Time                                                |           |

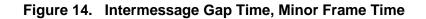

| Figure 15. Minor and Major Frames                                                                 | 175       |

| Figure 16. Use of Execute and Flip (XQF) Instruction For Sub address Double Buffering             |           |

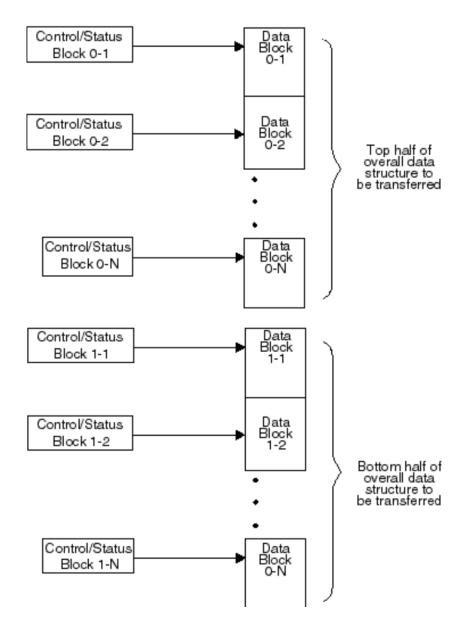

| Figure 17. Bulk Data Transfers                                                                    |           |

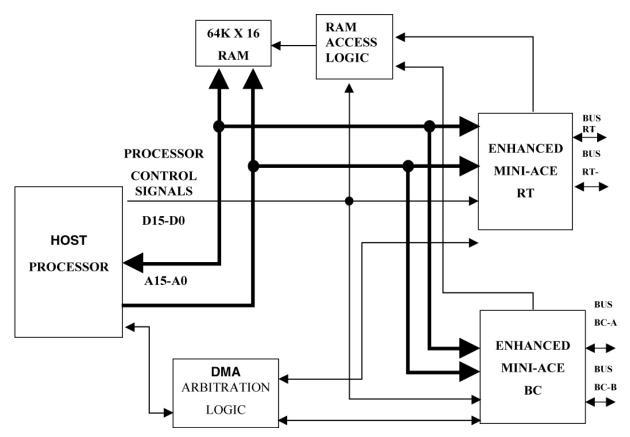

| Figure 18. Enhanced Mini-ACE RT and BC in DMA Configuration with Shared DMA Address Sp            |           |

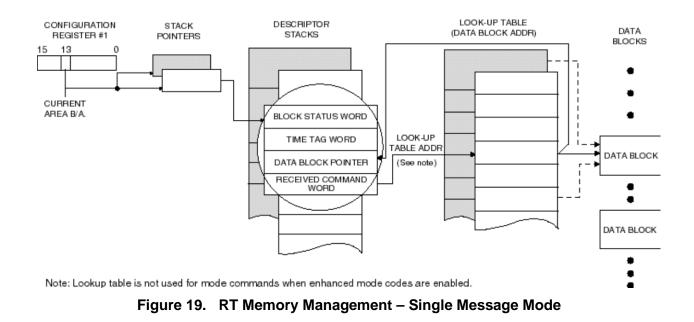

| Figure 19. RT Memory Management – Single Message Mode                                             |           |

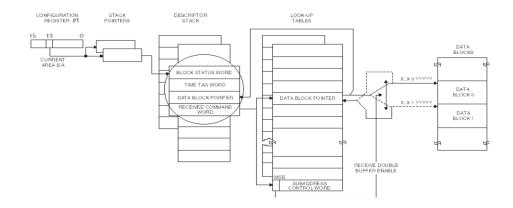

| Figure 20. RT Memory Management – Subaddress Double Buffering Mode                                |           |

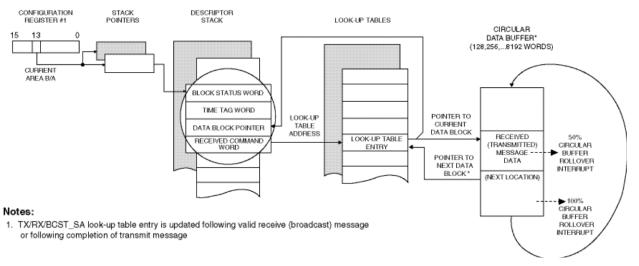

| Figure 21. RT Memory Management – Subaddress-Specific Circular Buffer Mode                        |           |

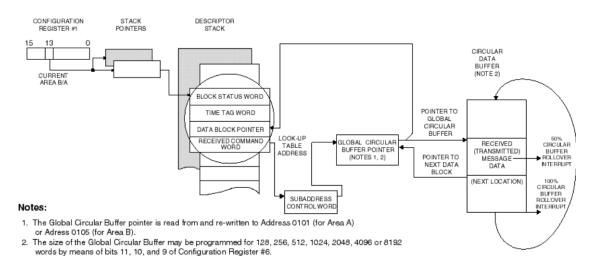

| Figure 22. RT Memory Management - Global Circular Buffer                                          |           |

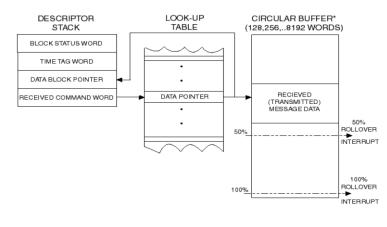

| Figure 23. 50% and 100% Rollover Interrupts                                                       |           |

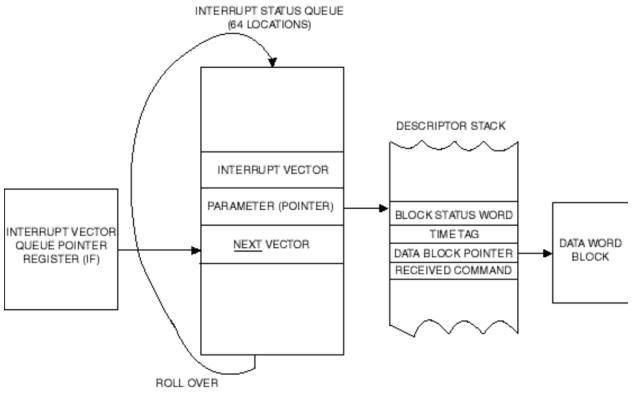

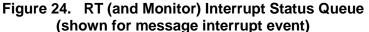

| Figure 24. RT (and Monitor) Interrupt Status Queue (shown for message interrupt event)            | 216       |

| Figure 25. Stack Pointer Area "A"                                                                 |           |

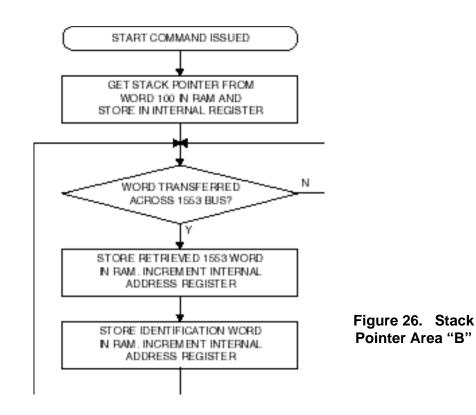

| Figure 26. Stack Pointer Area "B"                                                                 |           |

| Figure 27. Selective Monitor Data Block Formats                                                   |           |

| Figure 28. Selective Message Monitor Operation                                                    |           |

| Figure 29. RT (and Monitor) Interrupt Status Queue (shown message interrupt event)                |           |

| Figure 30. Connection Diagram for CH. A-to-CH. B Wraparound Self-Test                             |           |

## LIST OF TABLES (VOLUME 1)

| Table 1. Protocol Self-Test Times (in ms)                                                                                           | 8    |

|-------------------------------------------------------------------------------------------------------------------------------------|------|

| Table 2. Reset Conditions                                                                                                           | 9    |

| Table 3. Register Offset Addresses                                                                                                  | 11   |

| Table 4. Register Address Mapping                                                                                                   | 12   |

| Table 5. Interrupt Mask Register #1 (Read/Write 00h)                                                                                | 13   |

| Table 6. Configuration Register #1 (Read/Write 01h)                                                                                 | 14   |

| Table 7. Configuration Register #2 (Read/Write 02h)                                                                                 | . 15 |

| Table 8. Start/Reset Register (Write 03h)                                                                                           | . 15 |

| Table 9. BC/RT Command Stack Pointer (Register 03h)                                                                                 | . 15 |

| Table 10. BC Control Word Register (Read/Write 04h)                                                                                 | . 16 |

| Table 11. RT Subaddress Control Word (Read/Write 04h)                                                                               | . 16 |

| Table 12. Time Tag Register (Read/Write 05h)                                                                                        | . 16 |

| Table 13. Interrupt Register #1 (Read/Write 06h)                                                                                    | . 16 |

| Table 14. Configuration Register #3 (Read/Write 07h)                                                                                | 17   |

| Table 15. Configuration Register #4 (Read/Write 08h)                                                                                | . 17 |

| Table 16. Configuration Register #5 (Read/Write 09h)                                                                                | . 17 |

| Table 17. RT/Monitor Data Stack Address Register (Read/Write 0Ah)                                                                   | . 17 |

| Table 18. BC Frame Time Remaining Register (Read/Write 0Bh)                                                                         | . 18 |

| Table 19. BC Message Time Remaining Register (Read0Ch)                                                                              | . 18 |

| Table 20. Non-Enhanced BC Frame Time/Enhanced BC Initial Instruction Pointer/RT Last Command/N<br>Trigger Register (Read/Write 0Dh) |      |

| Table 21. RT Status Word Register (Read 0Eh)                                                                                        |      |

| Table 22. RT BIT Word Register (Read 0Fh)                                                                                           | 18   |

| Table 23. Configuration Register #6 (Read/Write 18h)                                                                                | . 19 |

| Table 24. Configuration Register #7 (Read/Write 19h)                                                                                | . 19 |

| Table 25. BC Condition Code Register (Read 1Bh)                                                                                     | . 19 |

| Table 26. BC General Purpose Flag Register (Write 1Bh)                                                                              | 20   |

| Table 27. Bit Test Status Register (Read 1Ch)                                                                                       | 20   |

| Table 28. Interrupt Mask Register #2 (Read/Write 1Dh)                                                                               | 20   |

| Table 29. Interrupt Status Register #2 (Read 1Eh)                                                                                   | 20   |

| Table 30. BC General Purpose Queue Pointer Register RT, MT Interrupt Status Queue Pointer Register (Read/Write 1Fh)                 |      |

| Table 31. BC Mode Block Status Word                                                                                                 |      |

| Table 32. RT Mode Block Status Word                                                                                                 |      |

| Table 33. MIL-STD-1553 Command Word                                                                                                 |      |

| Table 34. Word Monitor Identification Word                                                                                          |      |

| Table 35. Selective Message Monitor Mode Block Status Word                                                                          |      |

| Table 36. RT Status Word                                                                                                            |      |

| Table 37. RT/Monitor Interrupt Status Word (for Interrupt Status Word)                                                              |      |

| Table 38. Interrupt Mask Register (Read/Write 00H)                                                                                  |      |

| Table 39. Enhanced Mode Interrupts                                                                                                  |      |

| Table 40. Configuration Register #1 (Read/Write01H)                                                                                 |      |

|                                                                                                                                     |      |

#### LIST OF TABLES

| Table 41. Configuration Register #1. Mode Assignments                                                             | 34  |

|-------------------------------------------------------------------------------------------------------------------|-----|

| Table 42. Configuration Register #2 (Read/Write 02H)                                                              | 42  |

| Table 43. Time Tag Resolution                                                                                     |     |

| Table 44. Start/Reset Register (Write 03H)                                                                        | 47  |

| Table 45. Incrementing of Command Stack Pointer RAM Register and Active Area Stack Pointer RAM Location 51        | l   |

| Table 46. BC/RT Command Stack Pointer Register (Read 03H)                                                         | 51  |

| Table 47. BC Control Word Register (Read/Write 04H)                                                               | 52  |

| Table 48. RT Subaddress Control Word (Read/Write 04H)                                                             | 53  |

| Table 49. Time Tag Register (Read/Write 05H)                                                                      |     |

| Table 50. Time Tag Register Resolution                                                                            |     |

| Table 51. Interrupt Status Register #1 (Read Only 05H)                                                            | 56  |

| Table 52. Configuration Register #3 (Read/Write 07H)                                                              | 62  |

| Table 53. BC/RT Command Stack Size                                                                                | 65  |

| Table 54. Monitor Command Stack Size                                                                              |     |

| Table 55. Monitor Data Stack Size                                                                                 |     |

| Table 56. Configuration Register #4 (Read/Write 08H)                                                              | 70  |

| Table 57. Test Mode Selection                                                                                     |     |

| Table 58. Configuration Register #5 (Read/Write 09H)                                                              |     |

| Table 59. Clock Frequency Selection                                                                               |     |

| Table 60. Response Timeout Select                                                                                 | 78  |

| Table 61. RT Monitor Data Stack Address Register (Read/Write0AH)                                                  | 80  |

| Table 62. BC Frame Time Remaining Register (Read-Only 0BH)                                                        | 81  |

| Table 63. BC Message Remaining Register (Read-Only 0CH)                                                           | 82  |

| Table 64. BC Frame Time/RT Last Command/Mt Trigger Register (Read/Write 0DH)                                      | 82  |

| Table 65. RT Status Word Register (Shown for MIL-STD-1553B) (Read-Only 0EH)                                       |     |

| Table 66. RT BIT Word Register (Read-Only 0FH)                                                                    | 83  |

| Table 67. BC Mode Block Status Word                                                                               |     |

| Table 68. RT Mode Block Status Word                                                                               |     |

| Table 69. Message Monitor Mode Block Status Word                                                                  |     |

| Table 70. Configuration Register #6 (Read/Write 18H)                                                              | 85  |

| Table 71. Worst Case Contention Times                                                                             |     |

| Table 72. Global Circular Buffer Size                                                                             |     |

| Table 73. Clock Frequency Selection                                                                               |     |

| Table 74. Configuration Register #7 (Read/Write 19H)                                                              |     |

| Table 75. BC Condition Code Register (Read-Only 1BH)                                                              |     |

| Table 76. Number Of Message Retries                                                                               | 94  |

| Table 77. Operation Of Masked Status Set Condition                                                                |     |

| Table 78. BC General Purpose Flag Register (Write-Only 1BH)                                                       |     |

| Table 79. Control Of General Purpose Flag Bits                                                                    |     |

| Table 80. BIT Test Status Register (Read-Only 1CH)                                                                | 98  |

| Table 81. Interrupt Mask Register #2 (Read/Write 1DH)                                                             |     |

| Table 82. Interrupt Status Register #2 (Read-Only 1EH)                                                            | 101 |

| Table 83. General Purpose Pointer Register (RD/WR 1FH) RT, MT Interrupt Status Queue Pointer Register (RD/WR 1FH) | 105 |

| Table 84. Typical Legacy BC Memory Map (Shown For 4K RAM)                                                                                                                                                                                                                                                                                                                                                                 | 108                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Table 85. MIL-STD-1553B Command Word                                                                                                                                                                                                                                                                                                                                                                                      | 114                                                                                            |

| Table 86. MIL-STD-1553B Status Word                                                                                                                                                                                                                                                                                                                                                                                       | 115                                                                                            |

| Table 87. BC Control Word Register                                                                                                                                                                                                                                                                                                                                                                                        | 119                                                                                            |

| Table 88. Operation of BC Control Word Status Mask Bits                                                                                                                                                                                                                                                                                                                                                                   | 120                                                                                            |

| Table 89. BC Message Retry Conditions                                                                                                                                                                                                                                                                                                                                                                                     | 122                                                                                            |

| Table 90. Effect of Broadcast command received status word bit on STATUS SET condition                                                                                                                                                                                                                                                                                                                                    | 123                                                                                            |

| Table 91. Effects of BC Control Word 1553A/B* BIT                                                                                                                                                                                                                                                                                                                                                                         | 124                                                                                            |

| Table 92. BC Message Formats                                                                                                                                                                                                                                                                                                                                                                                              | 125                                                                                            |

| Table 93. BC Mode Block Status Word                                                                                                                                                                                                                                                                                                                                                                                       | 126                                                                                            |

| Table 94. Effect of Broadcast Command Received Status Word Bit on STATUS SET Condition                                                                                                                                                                                                                                                                                                                                    | 127                                                                                            |

| Table 95. Number of Message Retries                                                                                                                                                                                                                                                                                                                                                                                       | 128                                                                                            |

| Table 96. BC Start Sequences                                                                                                                                                                                                                                                                                                                                                                                              | 135                                                                                            |

| Table 97. BC Response Timeout Select                                                                                                                                                                                                                                                                                                                                                                                      | 139                                                                                            |

| Table 98. Operation of Status Masking (Other Than Broadcast Command Received)                                                                                                                                                                                                                                                                                                                                             | 140                                                                                            |

| Table 99. Operation of Status Masking (Including Broadcast Command Received)                                                                                                                                                                                                                                                                                                                                              | 141                                                                                            |

| Table 100. Memory Map For BC Example Pseudo Code                                                                                                                                                                                                                                                                                                                                                                          | 147                                                                                            |

| Table 101. BC Exception Conditions                                                                                                                                                                                                                                                                                                                                                                                        | 154                                                                                            |

| Table 102. BC Operations for Message Sequence Control                                                                                                                                                                                                                                                                                                                                                                     | 166                                                                                            |

| Table 103. BC Condition Codes                                                                                                                                                                                                                                                                                                                                                                                             | 171                                                                                            |

| Table 104. Code Example for Minor Frame Control                                                                                                                                                                                                                                                                                                                                                                           | 176                                                                                            |

| Table 105. Code Example for Use of Minor Frame Timer as BC Processor       Watchdog         177       177                                                                                                                                                                                                                                                                                                                 | g Timer                                                                                        |

| Table 106. Code Example of Asynchronous Message Insertion                                                                                                                                                                                                                                                                                                                                                                 | 178                                                                                            |

| Table 107. Example of Double Buffering Using XQF Instruction                                                                                                                                                                                                                                                                                                                                                              | 181                                                                                            |

| Table 108. Code Example of Channel Switching Using XQF Instruction                                                                                                                                                                                                                                                                                                                                                        |                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                           | 188                                                                                            |

| Table 109. Code Example of Data Logging Using the General Purpose Queue                                                                                                                                                                                                                                                                                                                                                   |                                                                                                |

| Table 109. Code Example of Data Logging Using the General Purpose Queue         Table 110. Code Example of External Trigger                                                                                                                                                                                                                                                                                               | 188                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                |

| Table 110. Code Example of External Trigger                                                                                                                                                                                                                                                                                                                                                                               | 193                                                                                            |

| Table 110. Code Example of External TriggerTable 111. Typical RT Memory Map (Shown For 4K RAM)                                                                                                                                                                                                                                                                                                                            | 193<br>195                                                                                     |

| Table 110. Code Example of External TriggerTable 111. Typical RT Memory Map (Shown For 4K RAM)Table 112. Lookup Tables                                                                                                                                                                                                                                                                                                    | 193<br>195<br>197                                                                              |

| Table 110. Code Example of External TriggerTable 111. Typical RT Memory Map (Shown For 4K RAM)Table 112. Lookup TablesTable 113. Register Bits Used To Enable RT Memory Management Features                                                                                                                                                                                                                               | 193<br>195<br>197<br>198                                                                       |

| Table 110. Code Example of External Trigger                                                                                                                                                                                                                                                                                                                                                                               | 193<br>195<br>197<br>198<br>199                                                                |

| Table 110. Code Example of External Trigger.Table 111. Typical RT Memory Map (Shown For 4K RAM)Table 112. Lookup Tables.Table 113. Register Bits Used To Enable RT Memory Management FeaturesTable 114. Control Word Bit Map (Read/Write 04h)Table 115. RT Subaddress Control Word Memory Management Options                                                                                                              | 193<br>195<br>197<br>198<br>199<br>209                                                         |

| Table 110. Code Example of External Trigger                                                                                                                                                                                                                                                                                                                                                                               | 193<br>195<br>197<br>198<br>199<br>209<br>217                                                  |

| Table 110. Code Example of External Trigger.Table 111. Typical RT Memory Map (Shown For 4K RAM)Table 112. Lookup Tables.Table 113. Register Bits Used To Enable RT Memory Management FeaturesTable 114. Control Word Bit Map (Read/Write 04h)Table 115. RT Subaddress Control Word Memory Management OptionsTable 116. RT Mode Block Status Word.Table 117. RT/Monitor Interrupt Vector Word (for Interrupt Status Queue) | 193<br>195<br>197<br>198<br>209<br>217<br>223                                                  |

| Table 110. Code Example of External Trigger                                                                                                                                                                                                                                                                                                                                                                               | 193<br>195<br>197<br>198<br>199<br>209<br>217<br>223<br>224                                    |

| Table 110. Code Example of External Trigger                                                                                                                                                                                                                                                                                                                                                                               | 193<br>195<br>197<br>198<br>209<br>217<br>223<br>224<br>226                                    |

| Table 110. Code Example of External Trigger                                                                                                                                                                                                                                                                                                                                                                               | 193<br>195<br>197<br>198<br>209<br>217<br>223<br>224<br>226<br>229                             |

| Table 110. Code Example of External Trigger                                                                                                                                                                                                                                                                                                                                                                               | 193<br>195<br>197<br>198<br>209<br>217<br>223<br>224<br>226<br>229<br>229                      |

| Table 110. Code Example of External Trigger                                                                                                                                                                                                                                                                                                                                                                               | 193<br>195<br>197<br>198<br>209<br>217<br>223<br>224<br>226<br>229<br>229<br>230               |

| Table 110. Code Example of External Trigger                                                                                                                                                                                                                                                                                                                                                                               | 193<br>195<br>197<br>198<br>199<br>209<br>217<br>223<br>224<br>226<br>229<br>229<br>230<br>233 |

| Table 127. Busy Bit Lookup Table for Definition                                                        | . 238 |

|--------------------------------------------------------------------------------------------------------|-------|

| Table 128. RT Status Word Programming Options                                                          | . 243 |

| Table 129. RT-to-RT Response Timeout Select                                                            | . 247 |

| Table 130. RT Bit Word (Read 0Fh)                                                                      | . 248 |

| Table 131. RT Exception. Conditions                                                                    | . 254 |

| Table 132. Mode Code Summary                                                                           | . 260 |

| Table 133 Memory Map For RT Example Pseudo Code                                                        | . 280 |

| Table 134. Typical Word MT Memory Map                                                                  | . 292 |

| Table 135. Word Monitor Identification Word                                                            | . 293 |

| Table 136. Word Monitor With Trigger Truth Table (Configuration Register #1 Bits)                      | . 298 |

| Table 137. Message Monitor Selection Table Address                                                     | . 300 |

| Table 138. Typical Selective Message Monitor Memory Map (shown for 4K RAM for "Monitor Only"Mode.)302  |       |

| Table 139. Typical RT/Selective Message Monitor Memory Map (shown for 64K RAM for combined RT/MT mode) | . 302 |

| Table 140. Selective Message Monitor Mode Block Status Word                                            | . 304 |

| Table 141. RT/Monitor Interrupt Status Word (for interrupt status queue)                               |       |

| Table 142. Test Time (in ms)                                                                           |       |

| Table 143. BIT Test Status Register (register address 1Ch, read-only)                                  | . 329 |

| Table 144. RT BIT Word                                                                                 | . 331 |

| Table 145. Self-Test Registers                                                                         | . 332 |

| Table 146. Self-Test ROM Address Register (36h)                                                        | . 333 |

| Table 147. Test Vector (RAM or Register) Address Register (37h)                                        | . 333 |

| Table 148. Test Vector (Ram or Register) Data (Latched on Failure) Register (38h)                      | . 333 |

| Table 149. Self-Test-ROM-Data (lower 16-Bits) Register (39h)                                           | . 334 |

| Table 150. Self-Test-ROM-Data (Upper 8-Bits) Register (3Ah)                                            | . 334 |

| Table 151. ROM Address Register (38h)                                                                  | . 334 |

| Table 152. RAM/Register-Address-Register-(Upper-19 –bits)(3Eh)                                         | . 335 |

| Table 153. Final Values of Self Test Registers Following Passed Protocol Self Test                     | . 335 |

## **1 PREFACE**

This User's Guide employs typographical conventions to assist the reader in identifying content.

#### 1.1 Text Usage

BOLD-indicates important information and table, figure, and chapter references.

BOLD ITALIC-designates DDC Part Numbers.

Courier New-indicates code examples.

<...> - indicates user-entered text or commands.

### **1.2 Special Handling and Cautions**

The *Enhanced Mini-ACE Series* uses state-of-the-art components, and proper care should be used to ensure that the device will not be damaged by Electrical Static Discharge (ESD), physical shock, or improper power surges and that precautions are taken to avoid electrocution.

#### **Cautionary Notice**

Turn off power to the PC and unplug from wall.

NEVER insert or remove card with power turned on.

Ensure that standard ESD precautions are followed. As a minimum, one hand should be grounded to the power supply in order to equalize the static potential.

Do not store disks in environments exposed to excessive heat, magnetic fields or radiation.

### 1.3 Trademarks

All trademarks are the property of their respective owners.

## **2** INTRODUCTION

All references throughout this document to the "Enhanced Mini-ACE" shall be interpreted to include Enhanced Mini-ACE, Micro-ACE, Mini-ACE Mark3, Micro-ACE TE, and Total-ACE products. Any specific references to a unique series of components (i.e. Micro-ACE only) will utilize the component part number (i.e. BU-61740B, BU-61840B/61860B etc.).

The Enhanced Mini-ACE family (Enhanced Mini-ACE, Micro-ACE, Mini-ACE Mark 3, Micro-ACE TE, Total-ACE) of MIL-STD-1553 terminals provides complete interfaces between a host processor and a 1553 bus. All these terminals integrate dual transceiver, protocol logic, and 4K words or 64K words of RAM. Additionally, the Total-ACE integrates the isolation transformer(s) as well. The BC/RT/MT versions with 64K words of RAM include built-in RAM parity checking.

The Enhanced Mini-ACE is packaged in a choice of a 1.0-inch square Flat Pack or Gull Wing package, or a 0.815-inch square BGA package (Micro-ACE). The Mini-ACE Mark 3 is packaged in a choice of a 0.890-inch Flat Pack or Gull Wing package, or a 0.815-inch square BGA package (Micro-ACE-TE). The Total-ACE is packaged in a 1.100-inch x 0.600-inch rectangular, plastic BGA.

The Flat Pack or Gull Wing packaged Enhanced Mini-ACE provides footprint compatibility with the previous generation Mini-ACE (Plus) terminal.

All members of the Enhanced Mini-ACE series (Enhanced Mini-ACE, Micro-ACE, Mini-ACE Mark3, Micro-ACE-TE, and Total-ACE) provide software compatibility with the previous generation Mini-ACE (Plus) terminals, and the older ACE series.

The Enhanced Mini-ACE and Micro-ACE are powered by a choice 5V, or 5V/3.3V (3.3V logic). Multiprotocol support of MIL-STD-1553A/B and STANAG 3838, including versions incorporating McAir compatible transmitters, is provided. There is a choice of 10, 12, 16, or 20 MHz clocks.

The Mini-ACE Mark3 and Micro-ACE-TE are powered by a choice of 3.3V/5V (logic), and 3.3V/5V (transceivers). (Certain combination restrictions apply. See datasheet for full ordering information). Multiprotocol support of MIL-STD-1553A/B and STANAG 3838, including versions incorporating McAir compatible transmitters, is provided. There is a choice of 10, 12, 16, or 20 MHz clocks.

The Total-ACE is an all 3.3V device (logic & transceivers) with integrated isolation transformers. (Certain combination restrictions apply. See datasheet for full ordering information). Multiprotocol support of MIL-STD-1553A/B and STANAG 3838, is provided. There is a choice of 10, 12, 16, or 20 MHz clocks.

BC features include a built-in engine, with a set of 20 instructions. This provides an autonomous means of implementing multi-frame message scheduling, message retry schemes, data double buffering, asynchronous message insertion, and reporting to the host CPU. The Enhanced Mini-ACE incorporates a fully autonomous built-in selftest, which provides comprehensive testing of the internal protocol logic and/or RAM.

The Enhanced Mini-ACE RT offers the same choices of subaddress buffering as ACE and Mini-ACE (Plus), along with a global circular buffering option, 50% rollover interrupt for circular buffers, an interrupt status queue, and an "Auto-boot" option to support MIL-STD-1760.

The Enhanced Mini-ACE terminals provide the same flexibility in host interface configurations as the Mini-ACE (Plus) terminals, and the older ACE series along with a reduction in the host processor's worst-case holdoff time.

Figure 1. Enhanced Mini-ACE / Micro-ACE Series Block Diagram

Note 1: See Ordering Information for Available Memory Options. Note 2: Transformer-Coupled configuration and ratio shown.

Figure 2. Mini-ACE Mark3 and Micro-ACE-TE Series Block Diagram (Shown with +3.3V Transceivers)

#### 2.1 Device Specifications

The Latest Device Specifications for the Enhanced Mini-Ace/ Micro-Ace and Mini-ACE Mark3/ Micro-ACE TE, and Total-ACE are available at <a href="http://www.ddc-web.com">http://www.ddc-web.com</a>:

For the latest Enhanced Mini-ACE/Micro-ACE information, see the BU-6174X/6184X/1686X Data Sheet.

For the latest Mini-ACE/Micro-ACE information, see the BU-6474X/6484X/6486X Data Sheet.

For the latest Total-ACE information, see the BU-64843T Data Sheet.

## **3 FUNCTIONAL OVERVIEW**

The BU-61743/61745 RT, and BU-61843/61845/61864/61865 BC/RT/MT Enhanced Mini-ACE (BU-61740B RT, and BU-61840B/61860B BC/RT/MT Micro-ACE), BU-64743/64745 RT, and BU-64843/64845/64863 BC/RT/MT Mini-ACE Mark3 (BU-64840B/64843B/64860B/64863B BC/RT/MT Micro-ACE-TE), and the BU-64843T Total-ACE family of MIL-STD-1553 terminals comprise a complete integrated interface between a host processor and a MIL-STD-1553 bus.

The BU-61743/61745 RT, and BU-61843/61845/61864/61865 BC/RT/MT Enhanced Mini-ACE are packaged in a 1.0-inch square ceramic flatpack package providing footprint (with four pin differences) compatibility with previous generation Mini-ACE terminals.

The BU-64743/64745 RT, and BU-64843/64845/64863 BC/RT/MT Mini-ACE Mark3 are packaged in a 0.890-inch square ceramic flatpack package. The BU-61740B RT, and BU-61840B/61860B BC/RT/MT Micro-ACE and BU-64840B/64843B/64860B/64863B BC/RT/MT Micro-ACE-TE are packaged in a 0.815-inch square BGA package.

The BU-64843T BC/RT/MT Total-ACE (with integrated isolation transformers) is packaged in a 1.100-inch x 0.600-inch rectangular, plastic BGA.

The Enhanced Mini-ACE series of hybrids provides software compatibility with the previous generation Mini-ACE terminals, as well as software compatibility with the older ACE series.

The Enhanced Mini-ACE RT provides complete multi-protocol support of MIL-STD-1553A/B/McAir and STANAG 3838. All versions integrate dual transceiver; along with protocol, host interface, memory management logic; and a minimum of 4K words of RAM. In addition, the BU-61864/BU-61865/61860B/64863/64860B/64863B BC/RT/MT terminals include 64K words of internal RAM, with built-in parity checking.The Enhanced Mini-ACE series includes 5V or 3.3V, voltage source transceivers for improved line driving capability, with options for MIL-STD-1760 and McAir compatibility. As a means of reducing power consumption, there are versions for which the logic is powered by 3.3V, rather than 5V. To provide further flexibility, the Enhanced Mini-ACE may operate with a choice of 10, 12, 16, or 20 MHz clock inputs.

One of the salient new features of the Enhanced Mini-ACE is its enhanced bus controller architecture. The Enhanced BC's highly autonomous message sequence control engine provides a means for offloading the host processor for implementing minor and major frame timing control; asynchronous message insertion; data block double buffering; bulk data transfers; and retry and bus switching strategy. For the purpose of performing messaging to the host processor, the Enhanced BC mode includes a General Purpose Queue, along with user-defined interrupts.

The Enhanced Mini-ACE is the latest device group in the ACE family. The term "enhanced" has also been used in earlier versions of the family to describe new features introduced at each stage. For backward compatibility reasons, the same terms and options have been maintained in the Enhanced Mini-ACE. The user will be aware of Enhanced Mode, set by bit 15 of Configuration Register (CR) # 3 along with the following optional features from earlier families:

| Enhanced RT Memory Management     | CR#2 Bit #1  |

|-----------------------------------|--------------|

| Enhanced RT Interrupt Handling    | CR#2 Bit #15 |

| Enhanced Mode Code Handling       | CR#3 Bit #0  |

| Enhanced Mode Enable              | CR#3 Bit #15 |

| Expanded BC Control Word Enable   | CR#4 Bit #12 |

| Plus for the latest devices:      |              |

| Enhanced BC                       | CR#6 Bit #15 |

| Enhanced Time Tag Synchronization | CR#7 Bit #2  |

| Enhanced BC Watchdog Timer Enable | CR#7 Bit #1  |

In many cases, the user may wish to enable most of these bits at initialization to have all available features active.

A second major new feature of the Enhanced Mini-ACE is the incorporation of a fully autonomous built-in self-test. This test provides comprehensive testing of the internal protocol logic. A separate test verifies the operation of the internal RAM. Since the self-tests are fully autonomous, they eliminate the need for the host to write and read stimulus and response vectors.

The Enhanced Mini-ACE RT offers the same choices of single, double, and circular buffering for individual subaddresses as the ACE and Mini-ACE (Plus). New enhancements to the RT architecture include a global circular buffering option for multiple (or all) receive subaddresses, a 50% rollover interrupt for circular buffers, an interrupt status queue for logging up to 32 interrupt events, and an option to automatically initialize to RT mode with the busy bit set. The interrupt status queue and 50% rollover interrupt features are also included as improvements to the Enhanced Mini-ACE's monitor architecture.

To minimize board space and "glue" logic, the Enhanced Mini-ACE terminals provide the same wide choice of host interface configurations as the ACE and Mini-ACE (Plus). This includes support of shared RAM interfaces to 16-bit or 8-bit processors, memory or port type interfaces, and multiplexed or non-multiplexed address/data buses; plus a DMA interface configuration.

Hermetic, ceramic packaged, Enhanced Mini-ACE series terminals are available in versions operating over the full military temperature range of -55 to +125°C. Available screened to MIL-PRF-38534C, these terminals are ideal for military and industrial processor-to-1553 applications.

#### 3.1 Transceivers

The transceivers in the Enhanced Mini-ACE series of terminals are fully monolithic, requiring only a +5 or 3.3 volt power input. The transmitters are voltage sources, which provide improved line driving capability over current sources. This serves to improve performance on long buses with many taps. The transmitters also offer an option that satisfies the MIL-STD-1760 requirement for a minimum of 20 volts peak-to-peak, transformer coupled output.

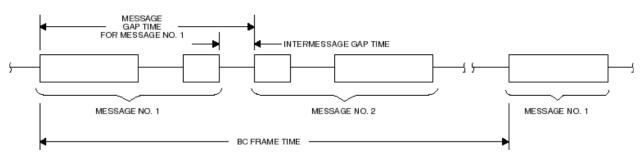

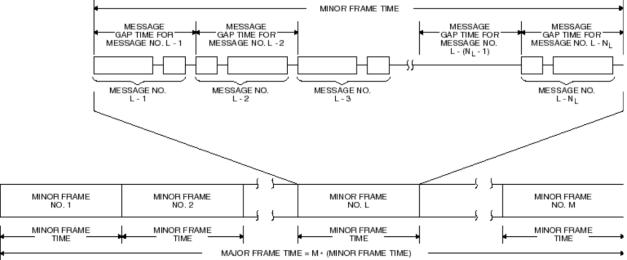

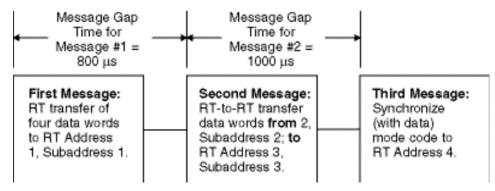

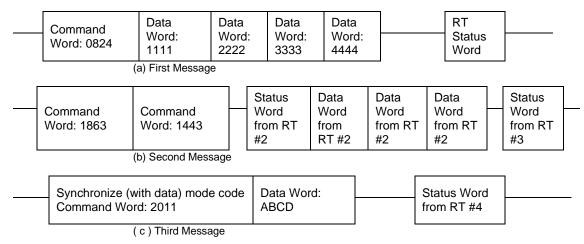

Besides eliminating the demand for an additional power supply, the use of a +5V or 3.3V -only transceivers requires the use of a step-up, rather than a step-down, isolation transformer. This provides the advantage of higher terminal input impedance than is possible for a 15 volt or 12 volt transmitter. As a result, there is a greater margin for the input impedance test, mandated for the 1553 validation test. This characteristic allows for longer cable lengths between a system connector and the isolation transformers of an embedded 1553 terminal. To provide compatibility to McAir specs, the Enhanced Mini-ACE is available with an option for transmitters with increased rise and fall times.