# Device Engineering Incorporated

385 East Alamo Drive Chandler, AZ 85225 Phone: (480) 303-0822 Fax: (480) 303-0824 E-mail: admin@deiaz.com

#### FEATURES

- Operates from single +3.3V power supply.

- Both +5V and -5V are generated on-chip.

- TTL/CMOS TO ARINC 429 Line Drivers.

- 5V/3.3V logic level compatible inputs with 4KV HBM ESD protection

- Rate control input set Hi (100KBS) or Lo (12.5KBS) speed slew rates.

- Drives full ARINC load.

- Output resistors: 5 Ohms or 37.5 Ohms.

- Operating temperature: industrial (-55 to +85°C) or extended (-55 to +125°C)

- Packages (RoHS):

- o 16L SOICN

- o 16L 4x4mm QFN

#### **GENERAL DESCRIPTION**

The DEI5090 line driver is a CMOS integrated circuit designed to directly drive the ARINC 429 avionics' serial digital data bus. The device converts TTL/CMOS serial input data to the tri-level RZ bipolar differential modulation format of the ARINC bus. A TTL/CMOS control input selects the output slew rate for HI (100KBS) and LOW (12.5KBS) speed operation. No external timing capacitors are required.

The part includes a dual polarity voltage doubler, allowing it to operate from a single +3.3V supply using only four external capacitors.

**DEI5090 SINGLE-RAIL**

**ARINC 429 LINE DRIVER**

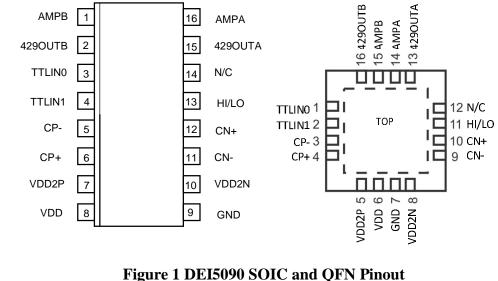

### Table 1 TERMINAL DESCRIPTIONS

| NAME    | FUNCTION      | DESCRIPTION                                                    |

|---------|---------------|----------------------------------------------------------------|

| AMPB    | 429 OUTPUT    | $5\Omega$ ARINC 429 format serial digital data output B        |

| 429OUTB | 429 OUTPUT    | 37.5Ω ARINC 429 format serial digital data output B            |

| TTLIN0  | LOGIC INPUT   | Serial digital data input 0 (10 K $\Omega$ pull down resistor) |

| TTLIN1  | LOGIC INPUT   | Serial digital data input 1 (10 K $\Omega$ pull down resistor) |

| CP-     | ANALOG OUTPUT | VDD2P flyback capacitor negative terminal                      |

| CP+     | ANALOG OUTPUT | VDD2P flyback capacitor positive terminal                      |

| VDD2P   | ANALOG OUTPUT | Voltage doubler positive output (+6.6V for +3.3V supply)       |

| VDD     | POWER INPUT   | +3.3V                                                          |

| GND     | POWER INPUT   | Ground                                                         |

| VDD2N   | ANALOG OUTPUT | Voltage inverter output (-6.6V for +3.3V supply)               |

| CN-     | ANALOG OUTPUT | VDD2N flyback capacitor negative terminal                      |

| CN+     | ANALOG OUTPUT | VDD2N flyback capacitor positive terminal                      |

| HI/LO   | LOGIC INPUT   | Slew rate control. (10 K $\Omega$ pull down resistor)          |

| N/C     | No Connect    |                                                                |

| 429OUTA | 429 OUTPUT    | 37.5 $\Omega$ ARINC 429 format serial digital data output A    |

| AMPA    | 429 OUTPUT    | $5\Omega$ ARINC 429 format serial digital data output A        |

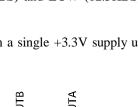

#### FUNCTIONAL DESCRIPTION

Figure 2 Block Diagram

#### Table 2 Speed Control Function

| HI/LO | OUTPUT TRANSITION TIME |

|-------|------------------------|

| 0     | 10us (12.5 KBS data)   |

| 1     | 1.5us (100KBS data)    |

#### **Table 3 Transmit Data Function**

| TTLIN1 | TTLIN0 | <b>4290UTA</b> | <b>429OUTB</b> | NOTES       |

|--------|--------|----------------|----------------|-------------|

| 0      | 0      | 0V             | 0V             | Null output |

| 0      | 1      | -5V            | 5V             | Zero output |

| 1      | 0      | 5V             | -5V            | One output  |

| 1      | 1      | Hi-Z           | Hi-Z           | Hi-Z output |

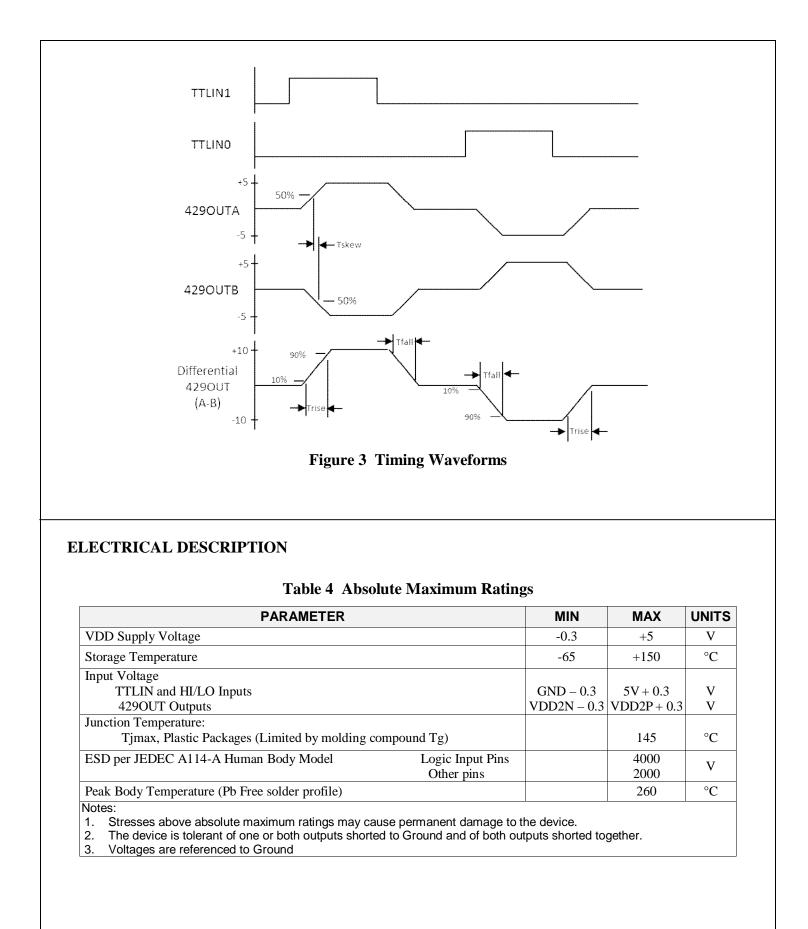

| PARAMETER             | SYMBOL          | CONDITIONS      |

|-----------------------|-----------------|-----------------|

| Supply Voltage        | VDD             | +3.13 to +3.46V |

| Operating Temperature |                 |                 |

| -xEx variants         | T <sub>OP</sub> | -55 to +85 °C   |

| -xMx variants         |                 | -55 to +125 °C  |

## Table 5 Recommended Operating Conditions

#### Table 6 Electrical Characteristics

| PARAMETER                                                     | TEST CONDITION                                                                     | SYMBOL                                                         | MIN                  | NOM                | MAX                  | UNITS        |

|---------------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------|----------------------|--------------------|----------------------|--------------|

|                                                               | LOGIC IN                                                                           | NPUTS                                                          |                      |                    |                      | 1            |

| Input Voltage, Logic 1                                        |                                                                                    | V <sub>IH</sub>                                                | 2.0                  |                    |                      | V            |

| Input Voltage, Logic 0                                        |                                                                                    | V <sub>IL</sub>                                                |                      |                    | 0.8                  | V            |

| Input Current                                                 | VIN = 0.1V                                                                         | I <sub>IL</sub>                                                | -20                  |                    | 20                   | uA           |

| Input Current                                                 | VIN = 3.46V                                                                        | I <sub>IH</sub>                                                | 260                  | 346                | 433                  | uA           |

|                                                               | ARINC OU                                                                           | JTPUTS                                                         |                      |                    |                      |              |

| ARINC Output Voltage<br>(Differential)<br>One<br>Null<br>Zero | Differential Output Voltage<br>= 429OUTA – 429OUTB.<br>No Load.                    | V <sub>DIF1</sub><br>V <sub>DIFnul1</sub><br>V <sub>DIF0</sub> | 9.0<br>-0.5<br>-11.0 | 10.0<br>0<br>-10.0 | 11.0<br>+0.5<br>-9.0 | V<br>V<br>V  |

| ARINC Output Voltage<br>(Single Ended)<br>Hi<br>Null<br>Lo    | Referenced to Ground<br>No Load.                                                   | Vo <sub>HI</sub><br>Vo <sub>null,</sub><br>Vo <sub>LO</sub>    | 4.5<br>-0.25<br>-5.5 | 5.0<br>0<br>-5.0   | 5.5<br>+0.25<br>-4.5 | V<br>V<br>V  |

| Output Resistance:<br>429OUT pins<br>AMP pins                 | Room Temperature                                                                   | Rout                                                           |                      | 37.5<br>5          |                      | Ohms<br>Ohms |

| ARINC Output Tri-State<br>Current                             | TTLIN0= TTLIN1= VDD<br>-5.75V < VOUT < 5.75V                                       | Ihiz                                                           | -1.0                 |                    | 1.0                  | uA           |

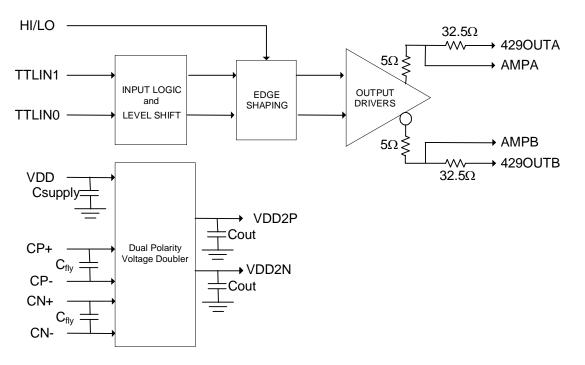

| Output Slew Rate<br>Hi Speed                                  | HI/LO = 1<br>No Load<br>10% to 90% voltage<br>amplitude of differential<br>output. | $T_{ m rise} \ T_{ m fall}$                                    | 1.0                  | 1.5                | 2.0                  | us           |

| Output Slew Rate<br>Lo Speed                                  | HI/LO = 0<br>No Load<br>10% to 90% voltage<br>amplitude of differential<br>output. | ${ m T_{rise}} \ { m T_{fall}}$                                | 5                    | 10                 | 15                   | us           |

| Output skew time between<br>A and B outputs.                  | HI/LO = 1<br>Measured at 50% voltage<br>amplitude of both outputs.                 | T <sub>skew</sub>                                              |                      |                    | 200                  | ns           |

| PARAMETER                                        | TEST CONDITION                                                                            | SYMBOL                                | MIN | NOM | MAX      | UNITS    |

|--------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------|-----|-----|----------|----------|

|                                                  | SUPPLY CU                                                                                 | JRRENT                                |     |     | 1        | 1        |

| Quiescent Operating Supply<br>Current:           | VDD=3.3V<br>HI/LO = 0 or 1<br>TTLIN0=TTLIN1= 0V<br>No Load<br>-xEx (85°C)<br>-xMx (125°C) | I <sub>VDD</sub>                      |     | 45  | 75<br>85 | mA       |

|                                                  | VOLTAGE D                                                                                 | OUBLER                                |     | 1   |          | 1        |

| Start-up transient (VDD2P, VDD2N)                | 10% of VDD to 50% of<br>VDD2P/N                                                           | T <sub>START</sub>                    |     |     | 10       | ms       |

| Operating Switching<br>Frequency                 |                                                                                           | F <sub>SW</sub>                       |     | 250 |          | KHz      |

| Worst case maximum voltage doubler output        | VDD = 3.6V, T = -55C,<br>Open load                                                        | V <sub>DD2P(max)</sub>                |     |     | 6.92     | V        |

| Ratio of bulk storage to fly-<br>back capacitors | $C_{OUT}/C_{FLY}$                                                                         | C <sub>OUT</sub><br>/C <sub>FLY</sub> | 2.2 | 10  |          | -        |

| Fly-back capacitor<br>Capacitance<br>ESR         | [0.5, 1.0]MHz                                                                             | $C_{FLY}$                             | 1.0 | 4.7 | 500      | uF<br>mΩ |

| Bulk storage capacitor<br>Capacitance<br>ESR     | [0.5, 1.0]MHz                                                                             | C <sub>OUT</sub>                      | 2.2 | 47  | 300      | uF<br>mΩ |

| VDD By-pass capacitor                            | - / 4                                                                                     | C <sub>SUPPLY</sub>                   |     | 68  |          | uF       |

#### **DESIGN CONSIDERATIONS**

#### **Power Supply and Voltage Doubler Capacitors**

$C_{SUPPLY}$  (see Figure 2): The VDD supply should be decoupled with a 68uF or larger tantalum or ceramic capacitor to source the voltage doubler ripple current, and a 0.1uF ceramic capacitor to provide high frequency filtering. The ripple current can be in the range of 100s of ma during peak loading.

$C_{FLY}$ : The two fly-back capacitors transfer energy from the charge pump inverters to the rectifiers. 4.7uf 10V X7R low DF ceramic capacitors are recommended. They should be in close proximity to the IC to minimize power loss and noise due to routing impedance. It may be beneficial to include parallel 0.1uf caps to minimize high frequency impedance.

$C_{OUT}$ : The two voltage doubler output capacitors filter the charge pump rectifier outputs. They should be at least 10x capacitance of the  $C_{FLY}$ . 47uf 10V/16V X5R/X7R low DF ceramic capacitors are recommended. They should be in close proximity to the IC to minimize power loss and noise due to routing impedance. It may be beneficial to include parallel 0.1uf caps to minimize high frequency impedance.

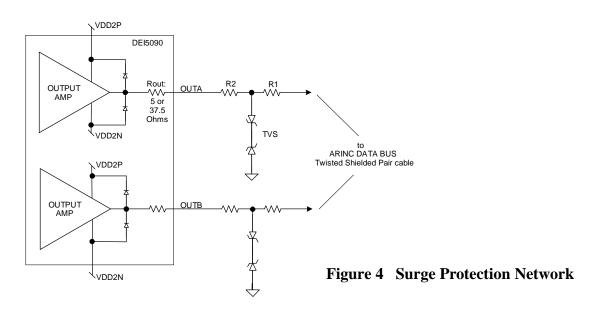

#### **Transient Voltage Protection**

The DEI5090 Line Driver requires external components to achieve immunity from surges such as those defined by DO160 Section 22, "Lightning Induced Transient Susceptibility". Typical surge protection includes silicon Transient Voltage Suppressor (TVS) devices and may include part of the 37.5 Ohms output resistance as external resistors to limit the surge current.

The DEI5090 has a robust output stage which includes large driver devices and clamp diodes to the VDD2P and VDD2N power rails as shown in figure 4. It withstands surge currents of  $\pm 0.5A$  for 175us without damage when powered with +3.3V supplies. At that surge current, the diodes clamp at ~1V above (below) the VDD2P (VDD2N) supply rail. ~350mA flows to the VDD2N (VDD2P) supply through the output amplifier, and ~150mA flows to the VDD2P (VDD2N) internal supply through the clamp diode. The outputs may be damaged by surges greater than 1A / 175us. At that current, the diode clamps at ~1.8V above (below) the supply.

The external lightning protection network should be designed to meet the specific requirements and constraints of the application equipment. The protection network should limit the OUTA/B pin surge current to the 0.5A / 175us maximum. The generalized circuit of figure 4 represents several TVS protection network options:

- The on-chip Rout value is 5 or 37.5 Ohms

- Select the total output resistance, Rout + R1 + R2 = 37.5 Ohms to meet ARINC bus requirements

- Select  $R1 = 20\Omega$ ,  $R2 = 12.5\Omega$ , Rout = 5 $\Omega$  to use low TVS with surge current rating (small TVS devices)

- ο Select R1 = 0Ω, Rout + R2 = 37.5Ω to use high TVS clamp voltage (20V + VDD2P/VDD2N)

- If the VDD2P/VDD2N internal supplies are un-powered or below operating voltage during the surge event, large currents may flow through the internal clamp diodes and damage the driver. If the application requires lightning immunity while un-powered, Select R1 =  $0\Omega$ , Rout + R2 =  $37.5\Omega$ , and select the TVS clamp voltage for <20V.

- Select TVS devices for the following

- TVS Surge power/current rating must withstand the application requirements for Lightning Induced Transient Levels and Waveforms. Microsemi Corporation publishes an application note specific to the DO160 lightning requirements (Micronote 126).

- Select low capacitance TVS devices to minimize the load on the line driver. (Examples: Microsemi LC and HSMBJSA series TVS) This is a priority for Hi Speed ARINC applications where the low capacitance is important for optimum signal integrity and power consumption. Note that the maximum total capacitance on the ARINC bus is 30nF line to line.

- Select the TVS clamp voltage at the lightning surge conditions such that the voltage/current into the DEI5090 OUT pin is within the safe region.

- If R1 is used to limit the TVS surge current, the resistor must withstand the surge current and voltage.

Some general considerations related to Lightning Immunity:

- Analyze the TVS high current signal and ground return path to insure adequate surge current capability. The IR voltage and L\*di/dt voltage in the ground return will add additional stress beyond the TVS clamp voltage.

- Observe suitable PCB design rules for traces subject to high voltage and high current surges.

- When possible, locate TVS devices close to the equipment connector to minimize the length of the surge voltage/current traces within the equipment.

- The shields of ARINC 429 data bus cables should be terminated to aircraft ground at all ends and at all bulkhead disconnects.

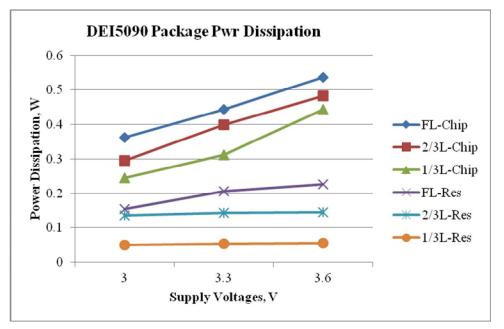

#### **Package Power Dissipation**

Good thermal management is fundamental to Line Driver device reliability. It is particularly important in designs operating at the HI speed data rate (100KBS) with high capacitive loads as this produces maximum power dissipation. It is inappropriate to continuously operate the plastic package above 145°C. Like all microcircuits, long term reliability is improved with lower operating temperatures.

The Line Driver's operating Tj is determined by internal power dissipation, package thermal resistance, and ambient temperature. The typical chip and internal  $32.5\Omega$  resistor power dissipation (Pd) simulation results are shown in Figure 5 with following variables:

- Data Rate The Hi Speed (100KBS) rate produces maximum power dissipation

- Load Full ARINC 429 load is  $30nF||400 \Omega$  line-to-line, 2/3 load is  $20nF||600 \Omega$  line-to-line, and 1/3 load is  $10nF||1200 \Omega$  line-to-line.

- Supply Voltages are 3.6V, 3.3V, and 3.0V at 25°C.

- Rout configuration The power dissipated in the two  $37.5\Omega$  output resistors is internal to the IC.

#### Note:

- 1. 100% Data Duty Cycle.

- 2. Full Load: 400  $\Omega$ //30nF, Mid Load: 600  $\Omega$ //20nF, Light Load: 1200  $\Omega$ //10nF

#### Figure 5 DEI5090 Chip and Internal 32.5Ω Resistor Power Dissipation vs Load

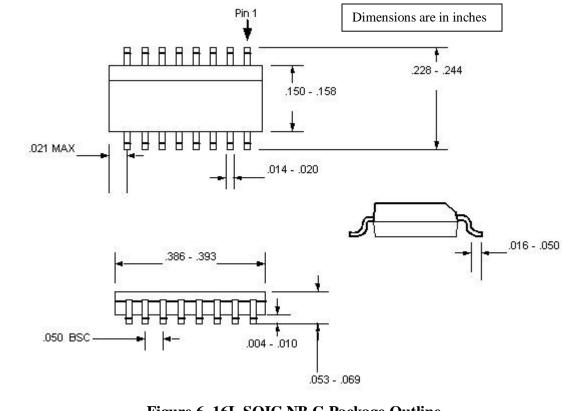

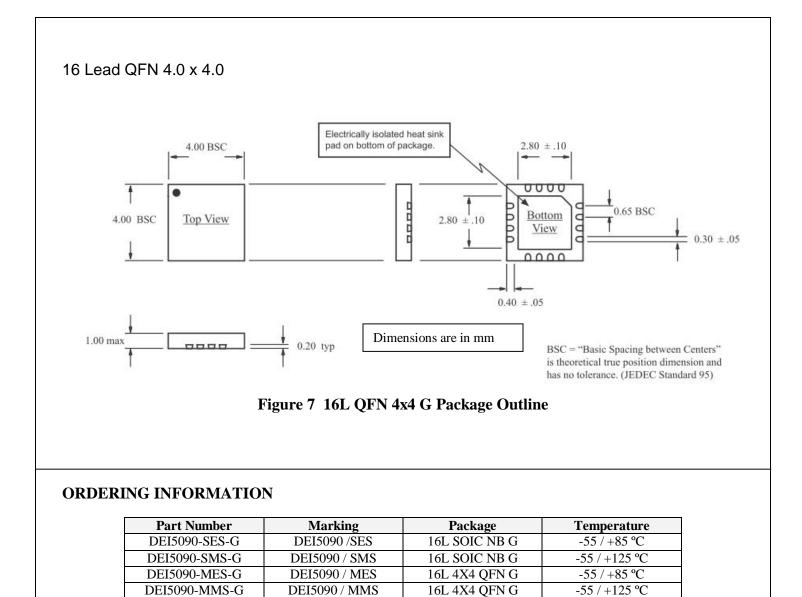

#### **PACKAGE DESCRIPTIONS**

| PACKAGE TYPE  | PACKAGE<br>REF  | THERMAL<br>RESIST.<br>$\theta_{JC} / \theta_{JA}$<br>(°C/W) | JEDEC MOISTURE<br>SENSITIVITY LEVEL<br>& PEAK BODY<br>TEMP | LEAD FINISH<br>MATERIAL /<br>JEDEC Pb-<br>Free<br>CODE | Pb Free<br>DESIGNATION |

|---------------|-----------------|-------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------|------------------------|

| 16L SOIC NB G | 16 NB<br>SOIC G | 29 / 73                                                     | MSL 1<br>260ºC                                             | NiPdAu<br>e4                                           | RoHS<br>Compliant      |

| 16L QFN 4X4 G | 16 QFN<br>G     | 10 / (1)                                                    | MSL 3<br>260ºC                                             | NiPdAu<br>e4                                           | RoHS<br>Compliant      |

| Table 7 | Package | Characteristics |

|---------|---------|-----------------|

|---------|---------|-----------------|

Notes:

1.  $\theta_{JA}$  is optimum with the exposed pad soldered to a PCB land with thermal vias connected to an internal ground plane.

#### 16 Lead SOIC NB G

### Figure 6 16L SOIC NB G Package Outline

DEI reserves the right to make changes to any products or specifications herein. DEI makes no warranty, representation, or guarantee regarding suitability of its products for any particular purpose.