# Device Engineering Incorporated

385 East Alamo Drive Chandler, AZ 85225 Phone: (480) 303-0822 Fax: (480) 303-0824 E-mail: admin@deiaz.com

## FEATURES

- Protection for power electronics on 28VDC avionics or industrial power bus to DO-160, Category Z, Abnormal Surge Voltage (DC) levels.

- Controls power P-FET to clamp transient at 34V.

- Small foot print (8L SOIC NB).

- Wide input voltage range.

- Programmable Undervoltage Lockout.

- Logic compatible On/Off input.

- Stable over temperature.

- Soft start delay.

## **GENERAL DESCRIPTION**

**DEI1028**

Voltage Clamping

Circuit

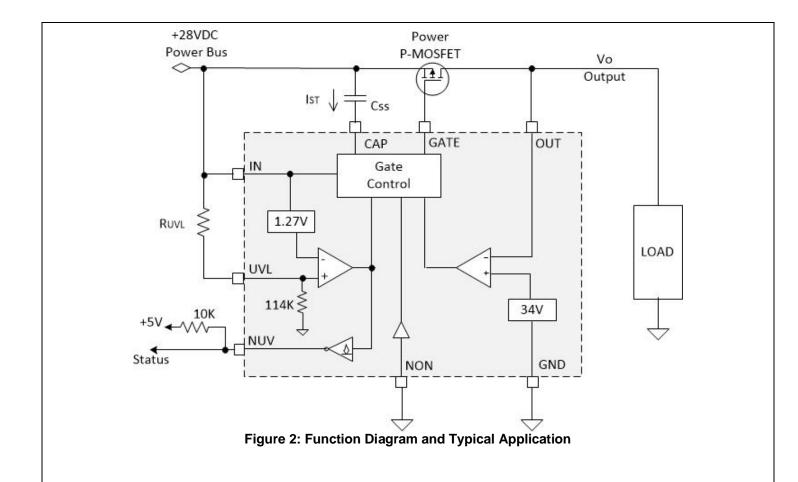

The DEI1028 is a control circuit for a 28VDC power bus voltage clamp. It is designed for use as the front end to a 28VDC input power supply to provide transient voltage protection. It controls the gate drive of a P-Channel power MOSFET to linearly clamp the output during over-voltage transients. The output voltage is maintained below the clamping threshold of 35V (max) which is adequate to protect most Commercial-Off-The-Shelf switching supplies, linear regulators, and op amps.

There is an Undervoltage Lockout feature that shuts the Power MOSFET off when the input voltage is below a user programmed threshold. An open collector logic output annunciates the under-voltage status. There is also a logic on/off input which may be used to control the power circuit. An external capacitor may be used to set a delay from when input power is applied to when the MOSFET is turned on.

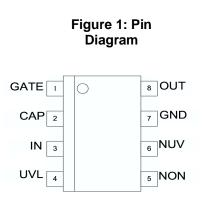

#### Table 1 Pin Definitions

| Pin # | Name | Description                                                                                                |  |  |

|-------|------|------------------------------------------------------------------------------------------------------------|--|--|

| 1     | GATE | <b>OUTPUT</b> . Controls the gate of the external P-channel power MOSFET.                                  |  |  |

| 2     | САР  | <b>IN/OUT</b> . Controls the soft start delay of the device. Use 0.22uF for 200ms minimum soft start time. |  |  |

| 3     | IN   | <b>INPUT.</b> Power input for the DEI1028 Voltage Clamp.                                                   |  |  |

| 4     | UVL  | <b>INPUT.</b> Controls the under voltage lockout condition of the device.                                  |  |  |

| 5     | NON  | INPUT. Logic low enables device. Logic high disables device.                                               |  |  |

| 6     | NUV  | <b>OUTPUT</b> . Open collector output. Active low when IN is below UVL threshold.                          |  |  |

| 7     | GND  | POWER. Ground                                                                                              |  |  |

| 8     | OUT  | <b>INPUT.</b> Feedback to gate control from drain of Power MOSFET.                                         |  |  |

## ELECTRICAL DESCRIPTION

Table 2: Absolute Maximum Ratings

|                 | Parameter                   |                  | Symbol           | Min  | Max  | Units |

|-----------------|-----------------------------|------------------|------------------|------|------|-------|

| IN Pin:         |                             | Continuous       |                  | -0.5 | +40  |       |

|                 |                             | 1 ms Transient   | V <sub>IN</sub>  | -50  | -    | V     |

|                 |                             | 100 ms Transient |                  | -    | +100 |       |

| UVL Pin:        | Relative to V <sub>IN</sub> |                  | V <sub>UVL</sub> | -6   | -0.5 | V     |

| CAP Pin:        | Relative to $V_{IN}$        |                  | V <sub>CAP</sub> | -20  | 20   | V     |

| GATE Pin:       | Relative to $V_{IN}$        |                  | $V_{GATE}$       | -10  | 0.5  | V     |

| NON Pin:        |                             |                  | V <sub>NON</sub> | -0.5 | 6.0  | V     |

| NUV Pin:        |                             |                  | V <sub>NUV</sub> | -0.5 | 20   | V     |

| OUT Pin:        |                             |                  | V <sub>OUT</sub> | -0.5 | 40   | V     |

| Operating Tempe | rature                      |                  | T <sub>A</sub>   | -55  | 125  | °C    |

| Storage Tempera | ture                        |                  | T <sub>STG</sub> | -65  | 125  | °C    |

| Notos:          |                             |                  |                  |      |      |       |

Notes:

(1) Voltages are relative to GND unless otherwise stated

(2) Stresses above absolute maximum ratings may cause permanent damage to the device.

| Parameter Symbol Conditions <sup>(4)</sup> Min Ma                                |                                                                                   |                                                                                                                                                                       |           | Max          | Units |

|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------|-------|

| Clamp                                                                            |                                                                                   |                                                                                                                                                                       |           |              |       |

| Clamp output voltage                                                             | V <sub>OCL1</sub>                                                                 | V <sub>IN</sub> = 40V, 60V                                                                                                                                            | 33        | 35           | V     |

| amp output voltage $V_{OCL2}$ $V_{IN} = 80V^{(2)}$                               |                                                                                   | 33                                                                                                                                                                    | 35        | V            |       |

|                                                                                  |                                                                                   | $R_{UVL} = 13.6 \text{ K}\Omega, V_{IN} = 14 \text{V}^{(5)}$                                                                                                          | 9         | 10           | V     |

| Source-Gate FET voltage (OFF)                                                    | V <sub>SG2</sub>                                                                  | $R_{\rm UVL} = 13.6 \text{ K}\Omega, V_{\rm IN} = 10 \text{V}^{(5)}$                                                                                                  | 0         | 0.7          | V     |

| Source-Gate FET voltage (ON)                                                     | V <sub>SG1</sub>                                                                  | $R_{UVL} = 7 \text{ K}\Omega, V_{IN} = 25 V^{(5)}$                                                                                                                    | 9         | 10           | V     |

| Source-Gate FET voltage (OFF)                                                    | V <sub>SG2</sub>                                                                  | $R_{UVL} = 7 \text{ K}\Omega, V_{IN} = 19.5 \text{V}^{(5)}$                                                                                                           | 0         | 0.7          | V     |

| Source-Gate FET voltage<br>(Linear control)                                      | $V_{SG3}$                                                                         | $35V < V_{IN} \le 80V^{(1)}$<br>$V_{OUT}$ = Clamp Voltage (33-35V)                                                                                                    | 0.7       | 9            | V     |

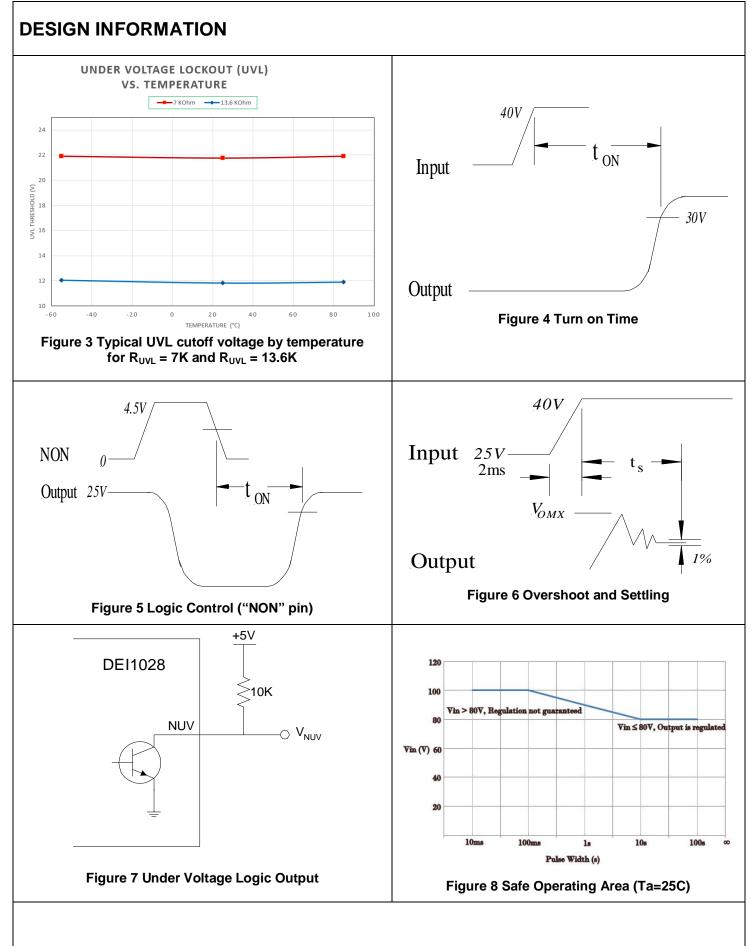

| Turn-on time                                                                     | t <sub>ON</sub>                                                                   | $C_{SS} = 0.22 \mu F^{(1)}$<br>See Figure 4 & Figure 5                                                                                                                | 200       | 550          | ms    |

| Power-on delay factor                                                            | R <sub>ST</sub>                                                                   | $V_{IN} > 10V$ $R_{ST} = V_{ST}/I_{ST}$ $= CAP \text{ switch voltage wrt } V_{IN} / CAP \text{ Charge current}$                                                       | 0.92      | 2.5          | MΩ    |

| Output overshoot voltage                                                         | V <sub>OMX</sub>                                                                  | See Figure 6 <sup>(1)</sup>                                                                                                                                           |           | 35           | V     |

| Output settling time                                                             | t <sub>s</sub>                                                                    | See Figure 6 <sup>(1)</sup>                                                                                                                                           |           | 2            | ms    |

|                                                                                  |                                                                                   | Supply Input                                                                                                                                                          |           | · · · ·      |       |

| Supply Current                                                                   | I <sub>IN</sub>                                                                   | $V_{IN} = 30V$                                                                                                                                                        |           | 5            | mA    |

|                                                                                  |                                                                                   | Logic IO                                                                                                                                                              |           |              |       |

| NON input logic 1 level                                                          | V <sub>IH</sub>                                                                   | $V_{IN} = 14V$                                                                                                                                                        | 2.8       |              | V     |

| NON input logic 0 level                                                          | V <sub>IL</sub>                                                                   | $V_{IN} = 14V$                                                                                                                                                        |           | 0.8          | V     |

| NON input logic 0 current                                                        | I <sub>IL</sub>                                                                   | $V_{NON} = 0V$<br>$V_{IN} = 14V$                                                                                                                                      | -300      | -30          | μΑ    |

| NUV output logic 1 level                                                         | V <sub>OH</sub>                                                                   | $\label{eq:R_UVL} \begin{array}{l} R_{UVL} = 13.6 \ K\Omega, \ V_{IN} = 14V, \\ R_{PU} = 10 \ k\Omega \ to \ 5V \ See \ Figure \ 7. \end{array}$                      | 4.75      |              | V     |

| NUV output logic 0 level                                                         | V <sub>OL</sub>                                                                   | $R_{UVL}$ = 13.6 K $\Omega$ , $V_{IN}$ = 10V<br>$I_{OL}$ = 420 µA See Figure 7.                                                                                       |           | 0.8          | V     |

|                                                                                  | Un                                                                                | der Voltage Lockout (UVL)                                                                                                                                             |           |              |       |

| V <sub>IN</sub> Undervoltage Lockout                                             | V <sub>UVL</sub> 13.6K                                                            | Minimum $V_{IN}$ where GATE becomes active. $R_{UVL}$ = 13.6 K $\Omega$                                                                                               | 11.0      | 13.0         | V     |

| Threshold                                                                        | V <sub>UVL</sub> 7K                                                               | Minimum $V_{IN}$ where GATE becomes active. $R_{UVL} = 7 \text{ K}\Omega$                                                                                             | 21.0      | 23.0         | V     |

| Table 2: Absolute Maxim<br>3.MOSFET capacitance (Cg<br>must be connected between | est. Duration<br>um Ratings fo<br>s) must be in<br>een the DEI10<br>= -55 to +85° | of voltage must be limited to 100ms<br>or more info.<br>the range 500 ~ 5000pF. If below<br>028 OUT and GATE pins.<br>C (-SES), -55 to +105°C (-SKS), V <sub>IN</sub> | 500pF, ar | n external 4 | -     |

#### **Table 3 Operating Characteristics**

© 2017 Device Engineering Inc.

### Gate Drive

The DEI1028 device is designed to control the gate of a P-Channel power MOSFET such as the IRF9540. At normal operation, the gate output turns the transistor ON to saturation. Below under voltage conditions the MOSFET is shut off. In clamp mode the MOSFET is driven to linear mode, keeping the output at approximately 34 V.

### Undervoltage Lockout

An Undervoltage Lockout feature is provided to prevent large currents from flowing through the MOSFET if the input voltage is too low. The resistor is placed between the IN and UVL pins. The following formula is used to determine the resistor value to set the nominal (25 °C) lockout threshold voltage:

$$R_{UVL}(Ohm) = 114K \times \frac{1.27}{(V_{UVL} - 1.27)}$$

See Figure 3 for temperature characteristics.

### **Power On Delay**

An external capacitor between CAP and the input voltage may be used to set a turn on delay time. See Figure 4. The CAP pin may be left open if no delay capacitor is used.

At start up, the voltage across the capacitor is approximately zero, the voltage at the CAP pin is approximately the input voltage, and the MOSFET is turned off. The 1028 CAP pin provides a current sink (~1ua) to charge the capacitor. The 1028 turns the MOSFET on when the voltage across the capacitor reaches a threshold voltage (~1.5V). The ratio of that threshold voltage over the charge current determines the power on delay time according to:

$$t_{ON}(s) \approx C_{SS}(F) \times R_{ST}(Ohm)$$

Where  $R_{ST}$  is as specified in Table 3 Operating Characteristics.

#### Safe Operating Area

The device protects against an 80V spike of ≤100ms duration, and provides overshoot protection. Pulses greater than 80V may cause the device to remove drive to the external FET, turning it off and causing the output to go below its clamped output voltage regulation level. This effect is worse at low temperature. The device provides conditioned power with Vin ≤80V, as described in DO160 Sect 16 Category Z "Typical Abnormal DC Surge Voltage Characteristics". See Figure 8.

#### Surge Operation

As shown in Figure 8, surges  $\leq$  80V will regulate and protect. For surges >80V, the device may lose drive to the external FET, but will continue to protect the output. The application designer must consider the safe operating area of the external FET separately.

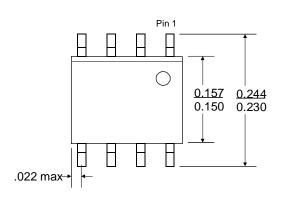

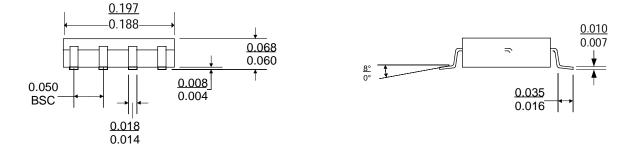

#### PACKAGE DESCRIPTION 8 Lead SOICN

#### Table 4 Package Characteristics, 8L SOICN

| PACKAGE TYPE                                                                                                                      | 8 LEAD SOICN        |

|-----------------------------------------------------------------------------------------------------------------------------------|---------------------|

| REFERENCE                                                                                                                         | 8L NB SOIC G        |

| $\begin{array}{ll} \mbox{THERMAL RESISTANCE:} \\ \theta_{JA} & (\mbox{4 layer PCB with Power Planes}) \\ \theta_{JC} \end{array}$ | 135 °C/W<br>40 °C/W |

| JEDEC MOISTURE SENSITIVITY LEVEL                                                                                                  | MSL 1 / 260°C       |

| LEAD FINISH MATERIAL /<br>Pb-free CODE                                                                                            | NiPdAu<br>e4        |

| Pb-Free DESIGNATION                                                                                                               | RoHS Compliant      |

| JEDEC REFERENCE                                                                                                                   | MS-012-AC           |

Dimension are in inches

#### Figure 9 Mechanical Outline, 8L SOICN

## **ORDERING INFORMATION**

| Table 5 | Ordering | Information |

|---------|----------|-------------|

|---------|----------|-------------|

| PART NUMBER   | MARKING                  | PACKAGE      | TEMPERATURE<br>RANGE |

|---------------|--------------------------|--------------|----------------------|

| DEI1028-SES-G | DEI1028<br>E4            | 8L NB SOIC G | -55 / +85 °C         |

| DEI1028–SKS-G | DEI1028<br>E4 + Blue Dot | 8L NB SOIC G | -55 / +105 °C        |

DEI reserves the right to make changes to any products or specifications herein. DEI makes no warranty, representation, or Guarantee regarding suitability of its products for any particular purpose.