FEATURES

- Fully Integrated 1553A/B Notice 2, McAir, STANAG 3838 Interface Terminal

- Compatible with older ACE and Mini-ACE, series.

- Choice Of:

- RT or BC/RT/MT In Same Footprint

- RT or BC/RT/MT with 4K RAM

- BC/RT/MT with 64K RAM, and RAM parity

- Choice of 5V or 3.3V Logic

- -1” Square Ceramic Flatpack or Gull Wing

- +5V Transceiver with 1760 and McAir Compatible Options

- Comprehensive Built-In Self-Test

- Flexible Processor/Memory Interface, with Reduced Host Wait Time

- Choice of 10, 12, 16, or 20 MHz Clock

- Highly Autonomous BC with Built-In Message Sequence Control:

- Frame Scheduling

- Branching

- Asynchronous Message Insertion

- General Purpose Queue

- User-defined Interrupts

- Advanced RT Functions

- Global Circular Buffering

- Interrupt Status Queue

- 50% Circular Buffer Rollover Interrupts

- Selective Message Monitor

- Selection by Address,T/R Bit, Subaddress

- Command and Data Stacks

- 50% and 100% Stack Rollover Interrupts

- Available with Full Military Temperature Range and Screening

PCI Version:

- 32-bit/33 MHz, 3.3 Volt PCI Target Interface

APPLICATIONS

A robust COTS solution for avionics, ground vehicles, and other military aerospace applications, the PCI Enhanced Mini-ACE MIL-STD-1553 series is compatible with DDC's earlier generations of ACE terminals.

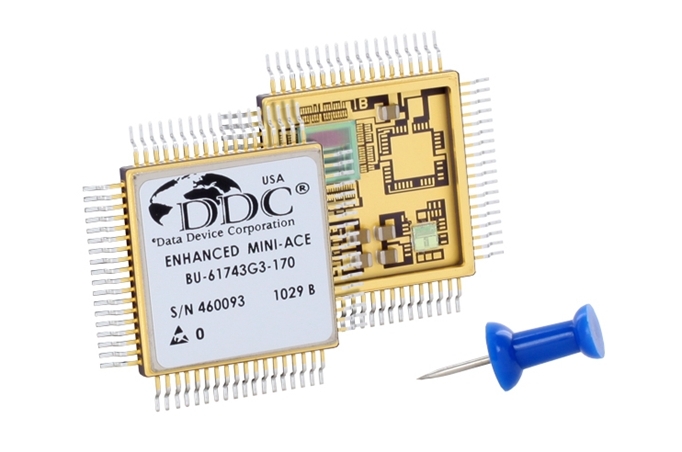

The Enhanced Mini-ACE family of MIL-STD-1553 terminals provides complete interfaces between a host processor and 1553 bus, integrating dual transceiver, protocol logic, and 4K or 64K words of RAM.

The terminals offer a choice of 5V or 3.3V logic, and feature multi-protocol support of MIL-STD-1553A/B and STANAG 3838, including versions incorporating McAir compatible transmitters. There is a choice of 10,12,16, or 20 MHz clocks. The BC/RT/MT versions with 64K words of RAM include built-in RAM real-time parity checking.

BC features include a built-in programmable message sequence control engine with a set of 20 instructions. This feature provides an autonomous means of implementing multi-frame message scheduling, message retry schemes, data double buffering, asynchronous message insertion, and reporting to the host CPU.

The RT offers the same choices of subaddress buffering as the ACE and Mini-ACE, along with a global circular buffering option, 50% rollover interrupt for circular buffers, an interrupt status queue, and an "Auto-boot" option to support MIL-STD-1760.

The Enhanced Mini-ACE incorporates a fully autonomous built-in self-test engine, providing comprehensive testing of the internal protocol logic and/or RAM.

The terminals provide the same flexibility in host interface configurations as the ACE and Mini-ACE, along with a reduction in the host processor's worst case hold-off time. Most software features are compatible with the previous generations of ACE and Mini-ACE series. Enhanced Mini-ACE architecture is also available in several new package styles, supply voltages and backend interfaces in the Mini-ACE Mark3, Micro-ACE TE series components.

The PCI Enhanced Mini-ACE MIL-STD-1553 series is a fully integrated solution for interfacing a 32-bit, 33-MHz PCI bus with a MIL-STD-1553 bus. A distinct improvement over multi-component implementations, the PCI Enhanced Mini-ACE reduces real estate and power requirements while eliminating the need for custom FPGA logic by providing a direct interface to embedded PCI buses. To accelerate host write operations, the interface incorporates a built-in FIFO that enables a PCI master to transfer a 32-word 1553 message in approximately 1.5 µs.